반도체 소자 구조에서 스페이서(Spacer)란, 게이트 단자의 사면을 Side Wall 형태로 둘러싼 절연막입니다. ‘공간을 채운다’라는 스페이서의 의미 자체는 이해하기 쉽지만, 스페이서를 Side Wall 형태로 설치해야 하는 이유와 그 목적을 이해하는 데는 약간의 어려움이 따릅니다. 스페이서는 트랜지스터(TR) 크기가 작아지는 과정에서 발생한 구조로써 Short Channel Effect, HCI, LDD, 채널, 게이트 전압과 채널의 관계 등 다양한 분야의 개념을 두루 알고 있어야만 이해하기가 수월하지요.

스페이서는 게이트 단자를 보호하는 역할도 하지만, 초창기의 목적은 하부에 도핑된 LDD 영역을 형성하기 위함이었습니다. 그 이후에는 낸드(NAND) 게이트 보호 및 미세 패턴 구조를 만드는 데도 유용하게 적용되고 있지요. 이번 장에서는 스페이서를 형성하는 목적과 공정 절차에 대해 알아보도록 하겠습니다. ▶<[반도체 특강] 절연층과 게이트 전압의 관계> 편 참고

1. 트랜지스터의 Malfunction 방지를 위한 고육지책

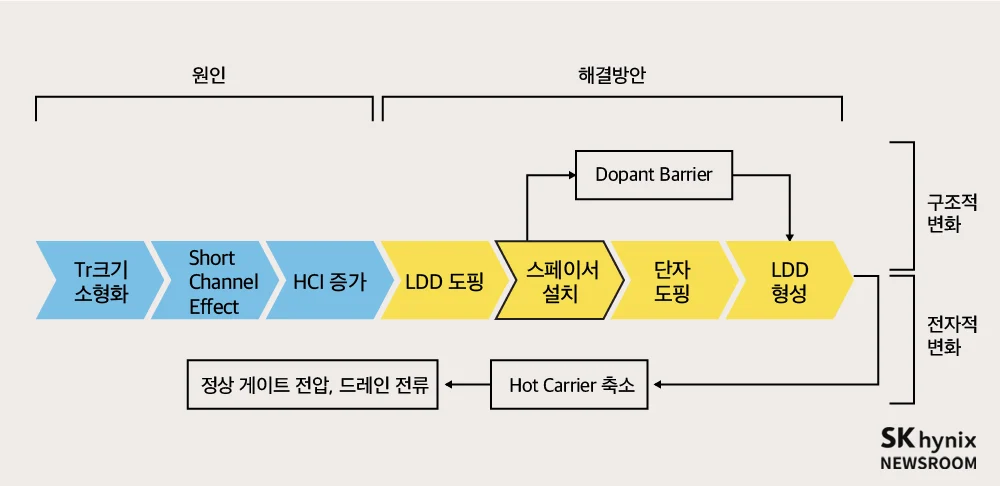

<그림 1> 트랜지스터(TR)의 축소로 발생하는 Short Channel Effect에 대한 해결 방안

채널의 길이가 짧아짐에 따라, 소스에서 드레인으로 건너가는 전자들은 드레인 단자와 근접해지면서 점차 강력한 전계를 받게 됩니다. 이때 높은 충돌에너지로 다수의 Hot Carrier(전자-정공, EHP)를 만들어냅니다. 충돌에너지가 변한 운동에너지를 갖게 된 전자들은 상부의 게이트 옥사이드(Gate Oxide)층으로 비교적 쉽게 월경(경계선을 넘음)해, 계면(게이트와 게이트옥사이드 혹은 게이트 옥사이드와 Substrate 접합면)에 머물게 될(Trapped Electron) 확률이 높아지지요. 이러한 작용을 HCI(Hot Carrier Injection) 효과라고 부릅니다. 하지만 Trap 전자 개수가 변할 경우, 일정한 면적의 채널을 형성하기 위해 게이트에 가하는 전압의 크기 또한 달라져야 하므로, 결국 문턱전압(VT)의 변화가 커져 트랜지스터(TR)는 조종 불능(Out of Control) 상태가 됩니다. 또한, 드레인 근방에서 발생한 정공들은 Sub의 마이너스 전압에 이끌려 불필요한 누설전류를 만들어내지요. ▶<[반도체 특강] Channel , MOSFET라는 세상의 다리> 편 참고

이러한 문제들을 해결하기 위해, 채널이 형성되는 자리인 드레인 단자 바로 앞에 드레인보다 농도가 약한 동일한 타입의 도핑 영역을 둡니다. 그러면 드레인으로 달려가는 전자들이 받는 전계의 크기가 작아지고 충돌에너지가 약화돼 HCI(EHP도 적게 발생)도 줄어들게 되지요. 이렇게 완충 및 버퍼(Buffer)의 역할을 하는 영역을 얇게 도핑됐다는 의미로 LDD(Lightly Doped Drain)라고 부릅니다. 일정 크기 이하로 줄어든 TR을 형성할 경우 대부분 LDD를 적용하고 있지요. LDD를 만들기 위해서는 게이트 단자를 Side Wall 형태의 절연체로 둘러싸야 하는데, 이 구조물이 바로 스페이서(Spacer)랍니다.

2. 스페이서 형성 단계 ① 스크린 옥사이드(Screen Oxide) 설치

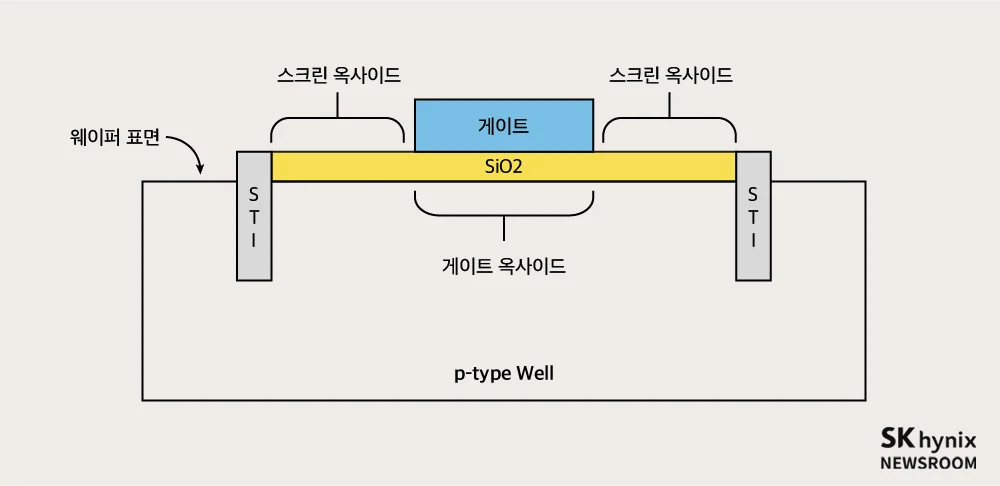

<그림2> 게이트 단자 형성

각 Well에는 TR이 한 개씩 들어서는데, Well의 타입에 따라 반드시 반대 채널 타입의 TR이 형성됩니다. 먼저 STI(Shallow Trench Isolation)가 TR과 TR 사이에 뿌리내린 뒤, 아파트를 짓듯 웨이퍼 표면 위로 여러 층을 적층(Stack)해 한 개의 TR을 완성합니다. 지하층이 만들어진 후 절연막(SiO2)부터 1층이 시작되면서, TR의 Active Area에 해당하는 영역에 절연막이 증착되고 그 위에 게이트층(Layer)이 올라섭니다. 게이트층은 포토 및 식각공정을 거치면서 작은 TR의 크기에 맞춰 알맞게 잘립니다. TR은 게이트 단자를 중심으로 모든 게 형성되고 동작하는 만큼, 3개 단자 중 게이트 단자가 가장 핵심이라 할 수 있습니다. 이러한 게이트 단자의 길이가 줄어듦으로써 Short Channel Effect가 발생하고, 이를 극복하기 위해 LDD 및 스페이서가 연이어 등장하지요.

게이트 옥사이드와 같은 재질이자 동일한 층인 스크린 옥사이드(Screen Oxide)는 LDD를 형성하기 위해, 이온주입 시 이온들이 결정격자 사이를 통과(Channeling)하는 것을 막는 일종의 이온 장애물입니다. 스크린 옥사이드는 이온들의 통행을 막거나 방해함으로써, 이온들이 경계면 근처에 포진하도록 해 이온 밀도를 높이는 역할을 합니다. 만약 이온들의 채널링을 막지 않는다면, 실리콘 깊숙이 이온들이 침투해 사전에 계산된 이온 밀도보다 낮아져 드레인 전류 계산이 틀어지게 되지요.

3. 스페이서 형성 단계 ② LDD(Lightly Doped Drain) 도핑(1차)

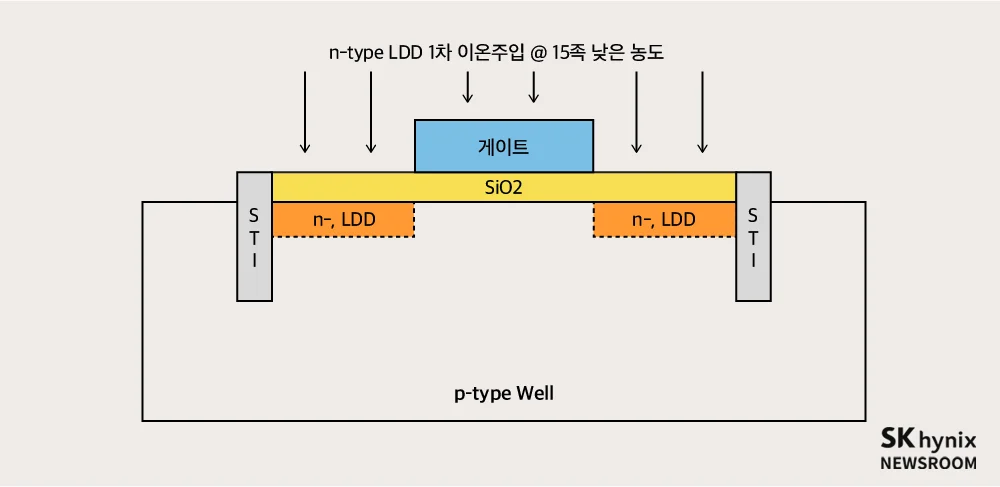

<그림 3> LDD(Lightly Doped Drain)층 형성 @ 낮은 농도 도핑(1차)

게이트층보다 밑에 위치한 실리콘 옥사이드층은 게이트와 동시에 식각되기도 합니다(LDD가 없는 Low Tech일 경우). LDD를 형성해야 할 경우에는 <그림3>과 같이 스크린 옥사이드 영역의 SiO2층을 제거하지 않습니다. LDD의 불순물 도핑(1차)은 채널 타입과 동일하게 진행하지만, 도핑 농도는 소스/드레인보다 1/100~1/1,000 수준으로 약하게 적용합니다. 즉 소스, 드레인, LDD 모두 채널과 동일한 타입으로 진행하는데, N-Type은 15족 원소, P-Type은 13족 원소를 주입합니다. 확산 방식으로 도핑을 할 경우, 등방성의 성질로 인해 불순물들이 게이트 단자 밑으로 침투해 채널의 길이가 더욱 짧아집니다. 따라서 최근에는 대부분 이온주입(Ion-Implantation) 방식으로 도핑을 진행하지요. 단, 소스/드레인 단자까지 도핑을 완료한 후 RTA(Rapid Thermal Annealing) 공정을 진행할 때에는 추가로 이온들이 확산해 들어가는 영역까지 사전 검토해 이온주입을 해야 합니다. ▶<[반도체 특강] 이온-임플란테이션 방식을 이용한 소스와 드레인 단자 만들기> 편 참고

4. 스페이서 형성 단계 ③ 스크린 옥사이드(Screen Oxide) 제거

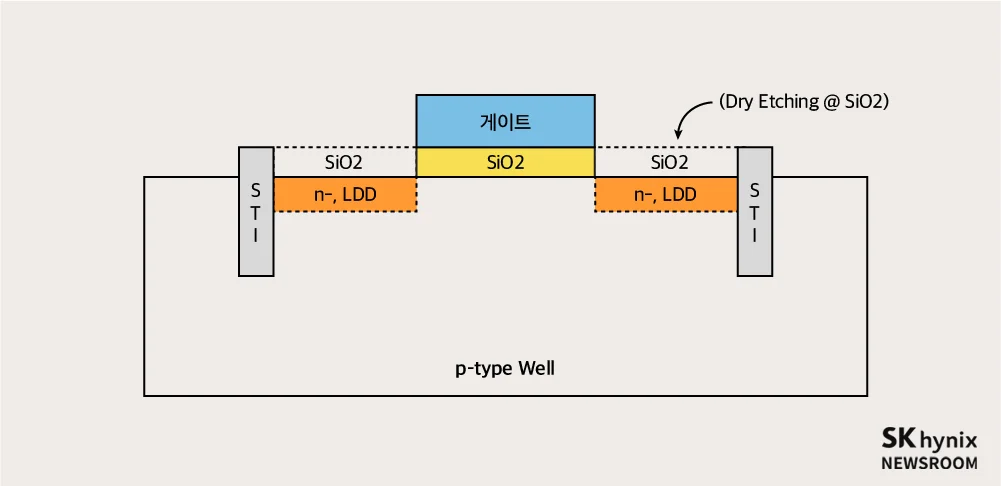

<그림 4> 게이트 옥사이드(Gate Oxide)층 형성 @ 게이트 옥사이드 이외의 영역 식각

LDD를 형성한 후 게이트 옥사이드층 외에는 더이상 절연막이 쓸모없어지므로, 스크린 옥사이드로 사용된 SiO2층을 모두 건식식각(Dry Etching) 방식으로 제거합니다. SiO2는 튼튼한 막이므로 CF4 등 강한 소스가스를 진공챔버 속에 투입해 플라스마를 형성, 이방성 식각으로 제거합니다. 선택비(Selectivity)가 높은 습식용액(등방성)을 사용해도 되지만, 최근에는 게이트 옥사이드 형태를 정확한 수직 형태로 유지하기 위해 대부분 건식식각을 이용합니다. 이는 LDD/드레인 단자 형성 시 등방성 성질을 배제하기 위해, 확산 대신 이온주입 방식을 적용하는 것과 같은 개념이지요. ▶<[반도체 특강] 식각(Etching), 패턴을 완성하다-上> 편, <[반도체 특강] 식각(Etching), 패턴을 완성하다-下> 편 참고

5. 스페이서 형성 단계 ④ 다시 두꺼운 산화막 형성

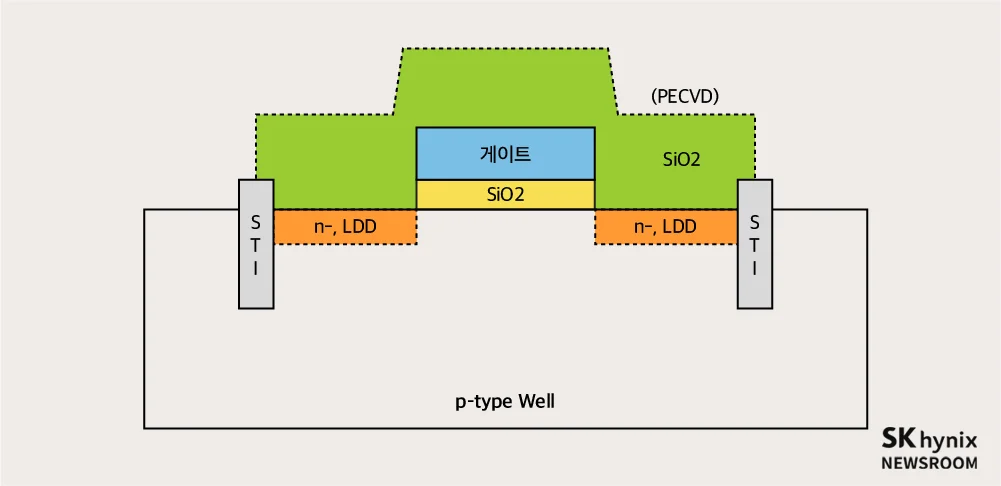

<그림 5> 실리콘 옥사이드(Silicon Oxide)층 형성 @ PECVD(Plasma Enhanced CVD)

다음 단계에서는 프리커서(Precursor)로 실란(SiH4)과 산소 가스를 진공챔버에 투입해 이산화실리콘(SiO2)층을 다시 형성합니다. 두께는 최소한 게이트 높이만큼 쌓아야 하므로, 1차 SiO2층 높이의 몇 배~십몇 배로 두꺼워집니다. 이때 증착되는 층의 게이트 단자 옆 일부(Side Wall)가 스페이서로 사용되지요. 공정은 고진공의 높은 온도에서 LPCVD(Low Pressure CVD)로 진행할 수 있지만, 속도가 느리다는 단점이 있습니다. 또 고절연성이어야 하는 게이트 옥사이드 막도 아니므로, 막질은 약하더라도 플라스마 에너지를 이용해 비교적 낮은 온도(섭씨 400도 정도)에서 PECVD(Plasma Enhanced CVD)로 빠르게 증착합니다.

그러나 낸드(2D)와 같이 특수한 부유게이트(Floating Gate)를 옆 구조물의 오염으로부터 보호해야 할 때는, 절연성이 우수한 막으로 붙여 놓습니다. 반면 일반적인 D램이나 CMOS용 TR일 경우에는 Side Wall로 적절한 막질이면 충분하지요. 절연성 막으로 SiO2가 아니라도 절연에 문제가 없다면 SiON 등도 사용할 수 있지만, 현재로서는 SiO2의 절연성이 가장 적절합니다. 게이트 단자 위층으로도 같은 높이의 막이 한꺼번에 증착되므로, 다음 공정인 식각을 어떻게 할지 검토하며 증착을 진행해야 합니다. ▶<[반도체 특강] 화학적으로 막을 성장시키는 방법, CVD > 편 참고

6. 스페이서 형성 단계 ⑤ Etch Back

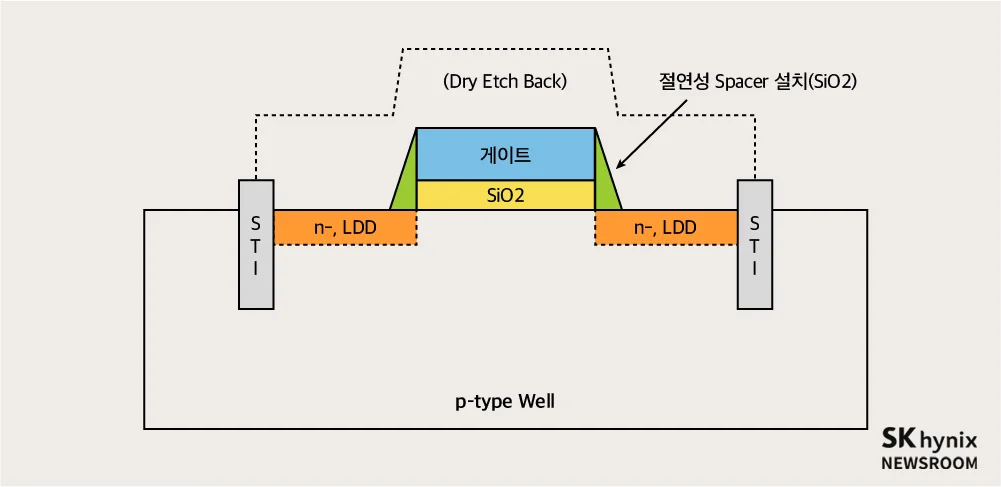

<그림 6> 스페이서 설치 @ Etch Back으로 실리콘 옥사이드층 제거

PECVD로 증착된 두꺼운 SiO2 막을 없애기 위해, 1차 식각 때와 동일하게 CF4를 이용해 이산화실리콘만을 선택적으로 식각(Plasma Etching)합니다. 절연막 제거는 Etch Back으로 진행하는데, 이는 포토공정을 거치지 않고 웨이퍼 표면 전체에 덮인 SiO2를 일괄적으로 식각하는 형태입니다. 커패시터(Capacitor)와 같이 세밀한 CD(Critical Dimension)로 식각하는 것이 아니므로, 빠른 동작속도로 진행합니다. Etch Back은 광범위하게 평탄화하는 형태로써, CMP(Chemical Mechanical Polishing)와 유사한 효과를 줍니다. 하지만 돌출된 게이트 때문에 CMP 공정으로 대체하지는 못하지요. 이때 게이트 단자 주위의 측면 쪽으로는 SiO2가 깎이지 않고 일정 부분이 남게 되는데, 이를 Side Wall 혹은 스페이서라고 합니다.

7. 스페이서의 기능: 이온주입(2차)의 방패막이

<그림 7> 소스/드레인 단자 형성 @ 높은 농도 도핑(2차)

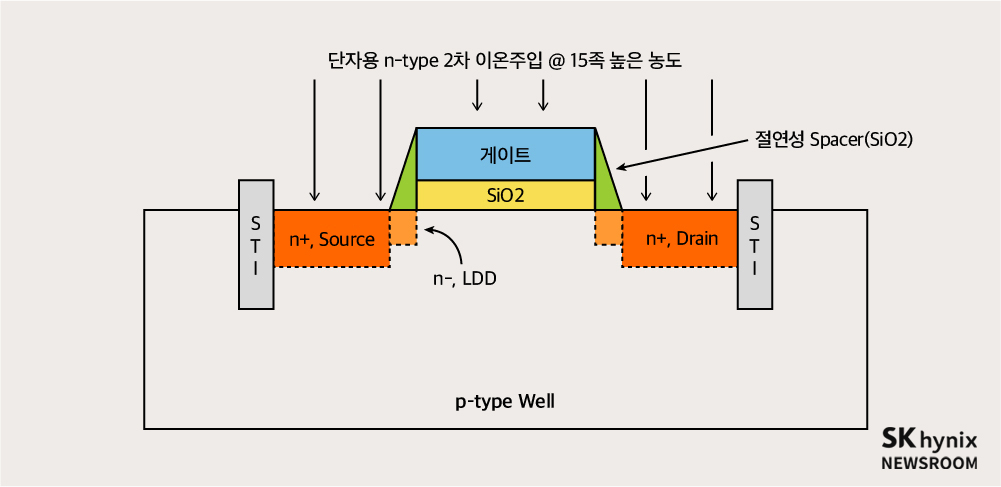

게이트 단자 옆에 얇게 붙어 있는 스페이서를 완성한 후, 소스/드레인 단자를 형성하기 위해 2차 이온주입을 진행합니다. 스페이서가 점유하고 있는 하단은 스페이서의 그림자로 영향을 받지 못하고, 그 외 영역만 높은 농도의 불순물이 도핑되어 소스/드레인 단자가 됩니다. 2차 도핑이 완료된 후에는 스페이서의 하단 부분이 <그림7>과 같이 남게 되는데, 이를 LDD라고 합니다.

절연물질인 스페이서는 LDD를 형성하기 위해 활용되기 시작했습니다. 그러나 TR의 크기가 줄어들면서 인가하는 전압이 작아졌고, 채널에서 전자가 느끼는 전계 크기도 작아져 HCI 문제가 발생할 확률이 줄어들었지요. 이에 따라 스페이서는 예전처럼 강력한 역할을 지니지는 못하지만, 여전히 중요한 기능을 하고 있습니다.눈에 띄지 않는 작은 스페이서로 만들어낼 수 있었던 LDD는, 그동안 고질적인 문제였던 HCI 문제를 해결해줬습니다. 이처럼 반도체 내 구조와 재질들은 크기가 작고 영향이 미미할지라도, 모두 저마다의 역할을 해내기 위해 고심 끝에 탄생한 것들이지요. TR의 크기가 작아져 발생하는 문제를 여러 가지 추가 공정을 거쳐 해결했는데, 그 결과로 얻은 부산물인 스페이서는 플로팅게이트(낸드) 내 전자를 보호하기도 하고, 선폭을 줄이는 멀티패터닝 기술(SPT, DPT, QPT)로써 아주 중요하게 사용되고 있습니다. 또, 소스와 게이트 단자 사이 및 드레인과 게이트 단자 사이 간섭을 줄여 상호 영향을 줄여주는 역할도 하고 있지요. 앞으로 스페이서의 또 다른 변신이 주목되는 이유입니다.

※ 본 칼럼은 반도체/ICT에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.