게이트 단자 내 절연층이 1개일 때는 외부에서 주어진 전압의 손실 없이 게이트 전압이 거의 대부분 기판(Substrate)에 전달됩니다. 그러나 절연층이 2개 이상일 때는 단자에 인가한 전압보다 게이트를 거쳐 기판에 전달되는 전압이 급격히 줄어들게 되는데요. 이는 2개의 절연막이 형성한 커패시턴스(Capacitance) 비율이 만들어낸 결과입니다. 절연막의 커패시턴스 값은 게이트 단자에 절연막을 만들 당시 외부에서 공급한 각종 공정상수들을 측정하여 계산해 내지요(이는 예측값으로, 실제값과는 오차가 발생할 수 있습니다). 이러한 커패시턴스의 값은 채널을 이동하는 전자 개수의 계산치와 합하여 드레인 전류를 도출해내는 중요한 요소가 됩니다. 오늘은 비휘발성 디바이스에 적용하는 게이트 단자 내 형성된 2개의 절연막으로 인해 게이트 전압이 얼마나 줄어드는지 알아보겠습니다.

워드라인을 통해 공급되는 게이트 전압

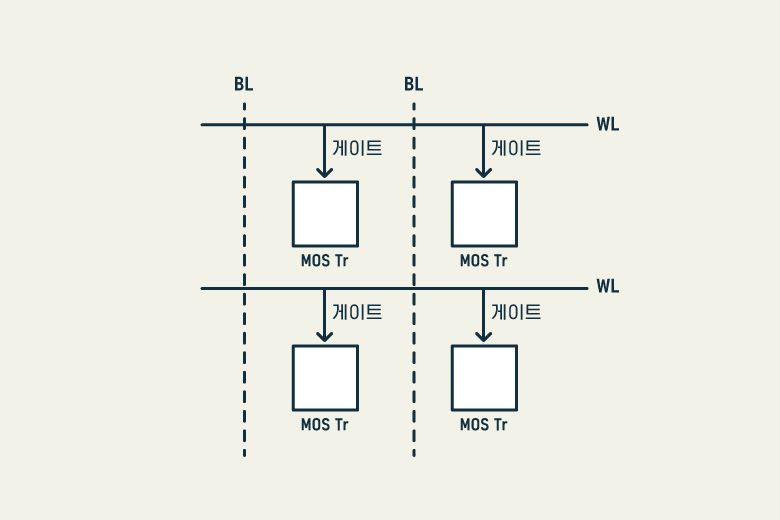

▲ 워드라인을 통한 게이트 전압 공급

칩 외부에서 워드라인(Word Line, WL)을 타고 들어온 전압은 MOSFET의 3개 단자 중 게이트 단자에 전압을 공급합니다. 워드라인의 공급 형태는 휘발성 메모리이건 비휘발성 메모리이건, 혹은 비휘발성 메모리 중에서도 NOR Flash 메모리이건 NAND Flash 메모리이건 모두 병렬 구조 방식으로 전압을 공급하지요. 병렬구조란 각 트랜지스터(Transistor, Tr)의 게이트 단자에 전압을 개별적으로 직접 공급한다는 뜻입니다.

게이트 단자 내 구조에 따라 달라지는 전압

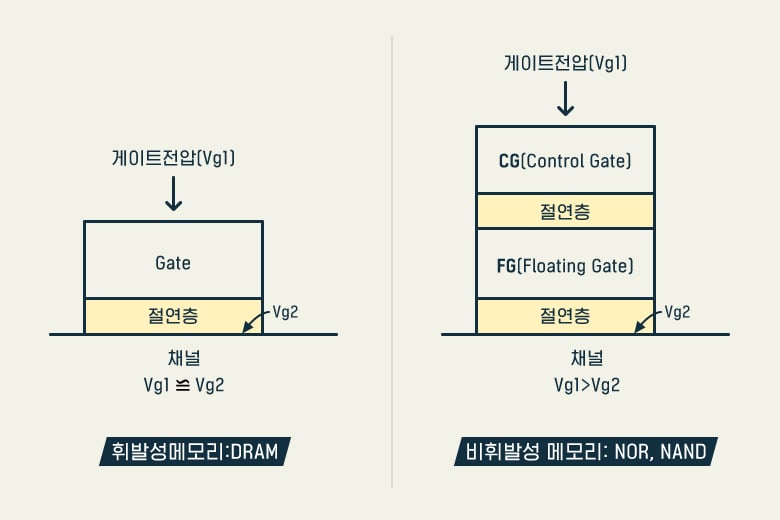

▲ 절연층 변수로 영향받는 게이트 전압의 세기

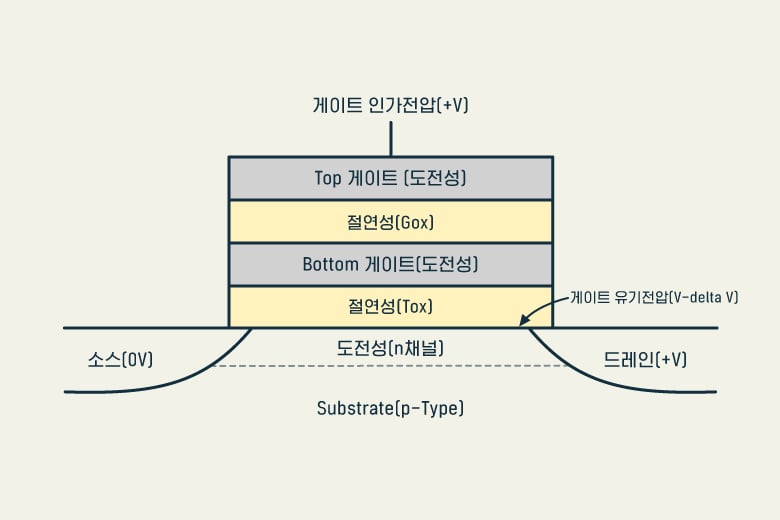

게이트 전압은 도전층과 절연층을 거쳐 채널로 전달되는데, 휘발성 메모리인 DRAM에는 절연층(Oxide Layer)이 1개 있고, 비휘발성 메모리에서는 절연층이 2개 있습니다. 절연층의 조합은 게이트 전압이 실질적으로 채널에 전달되는 전압의 세기를 다르게 합니다. 언뜻 생각해보아도 절연층이 많을수록 전달되는 전압의 세기가 약해지겠지요. 예를 들어 지각층이 여러 개 층으로 구성되어 있으면 표면에 전달되는 지진파의 세기도 약해지듯이 말입니다.

절연층의 커패시터 역할

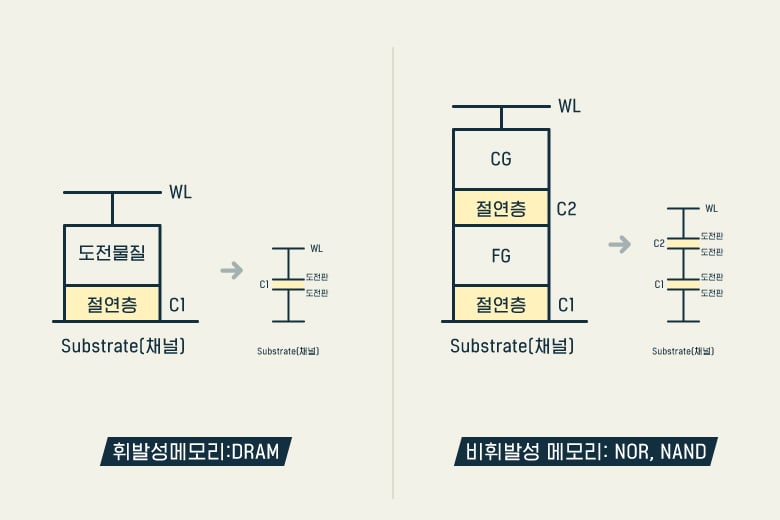

▲ 절연층의 커패시터 역할

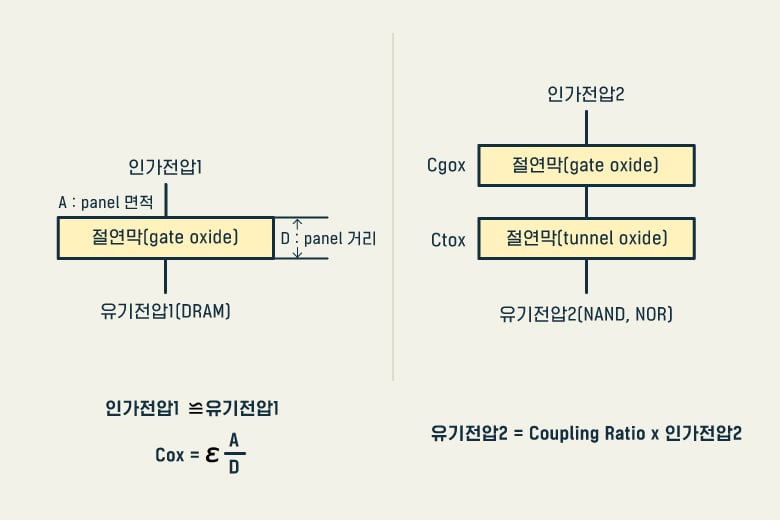

반도체에서는 도전적인 특징을 갖는 층(이하 도전층)과 절연적인 특징을 갖는 층(이하 절연층)을 지그재그식으로 형성합니다. 즉 절연층은 도전층 사이에 끼어 있고, 도전층은 절연층과 절연층 사이에 두게 됩니다. 커패시터(Capacitor) 구조를 보면 도전판과 도전판 사이에 절연층이 끼어 있듯이, 게이트 단자에서도 마찬가지로 도전층 사이에 있는 절연층은 커패시터 역할을 합니다. DRAM에서는 절연층의 역할이 단순하지만, 비휘발성 메모리에서는 2개의 절연층이 있기 때문에 절연층의 역할이 복잡해집니다. 그래서 절연층이 1개 있는 DRAM 게이트 단자는 커패시터가 1개 있는 셈이고, 절연층이 2개 있는 NAND Flash나 NOR Flash는 커패시터가 2개 있다고 볼 수 있습니다.

줄어드는 절연층 두께

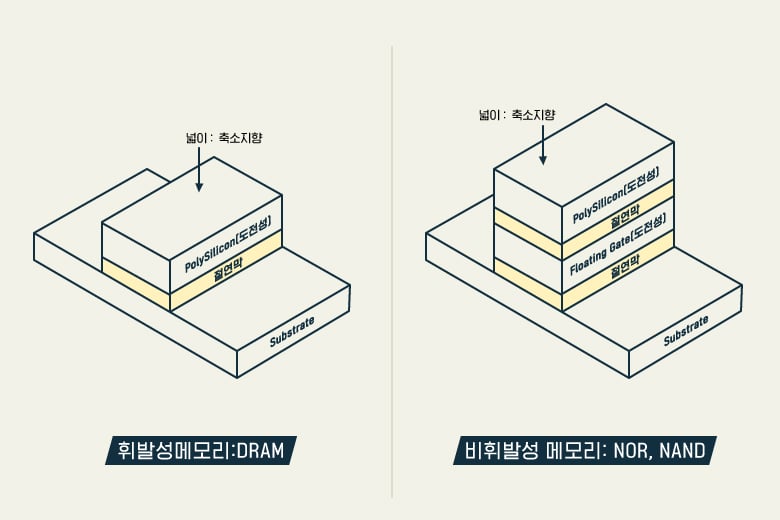

▲ 넓이와 두께를 계속적으로 줄여야 하는 게이트 내의 절연막

커패시터의 단위인 커패시턴스는 도전판의 넓이에 비례하고, 도전판과 도전판 사이의 거리에 반비례합니다. 즉 커패시터를 구성하는 도전판 사이의 폭이 좁을수록 커패시턴스의 값은 상승합니다. 게이트 단자 내 절연층도 동일한 양상을 보입니다. 커패시터에서 두 도전판 사이의 폭이 절연층의 두께를 의미하므로, 절연층의 두께가 좁을수록 게이트 절연막의 커패시턴스 값이 올라갑니다. 반면, 절연막의 넓이를 넓힐수록 커패시턴스의 값은 당연히 상승하겠지요. 절연막 하부에 최소 필요한 전하량을 끌어모으려면 일정 수준의 커패시턴스 값을 유지시켜 주어야 합니다. 하지만 게이트 내 절연막의 넓이는 계속 줄여야 하고 커패시턴스 값은 일정 상수 값을 유지시켜야 하므로, 절연막의 두께를 계속적으로 줄일 수밖에 없습니다.

커패시턴스 값을 높이는 방법

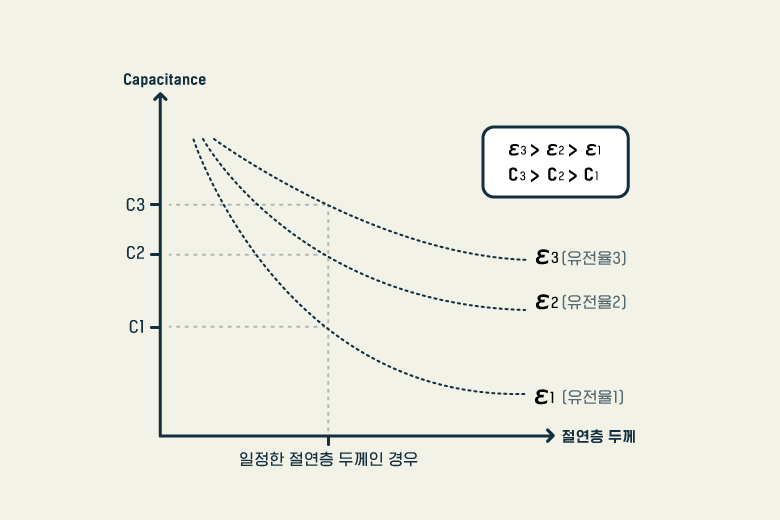

▲ 유전율과 커패시턴스의 관계

게이트 내 절연막에서 절연층 두께를 좁히는 방법 이외에, 커패시턴스의 값을 높이는 또 다른 방법으로는 절연물질의 유전율을 높이는 것입니다(C=εA(절연막 넓이)/L(절연막 두께)). 커패시턴스의 값은 유전율(ε, epsilon)을 높이면 상승하므로, 높은 유전율인 high-K 물질(HKMG 등)을 사용합니다. ▶<게이트 옥사이드의 기능과 신뢰성 > 편 참고 그림에서 보면 절연막의 두께가 일정할 때 유전율이 높으면 커패시턴스 값은 상승함을 알 수 있습니다. 유전율이 높은 절연체일수록 절연층이 두꺼워져도 유전률이 낮은 것에 비해 커패시턴스의 감소율이 작습니다.

플로팅 게이트로 인한 게이트 전압의 영향

▲ 플로팅 게이트로 인한 게이트 전압의 영향

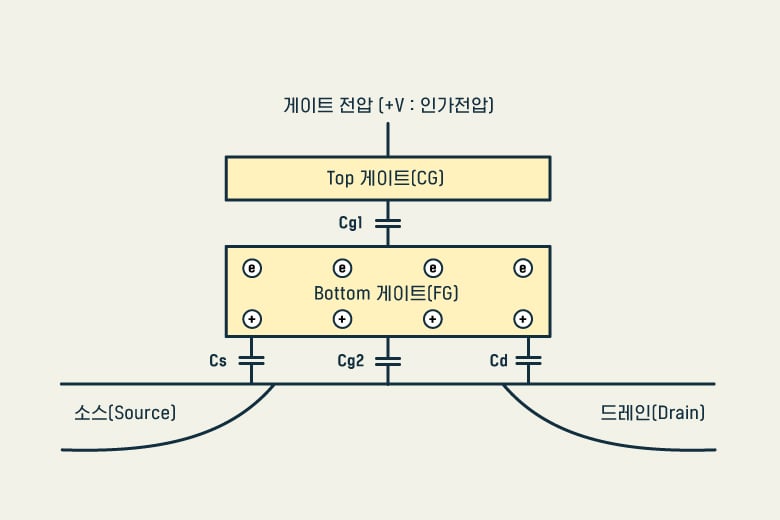

채널에 직접적인 영향을 주는 게이트 전압은 일정 크기 이상이어야 합니다. 하지만 낸드의 구조는 중간에 플로팅 게이트(Floating Gate: Bottom Gate 혹은 부유게이트)가 있기 때문에 플로팅 게이트의 위아래 절연막이 2개의 커패시터 역할을 합니다. 따라서 워드라인을 타고 들어온 게이트 인가전압에 비해 채널에 직접적인 영향을 주는 게이트 유기전압은 낮아지지요. 이는 부유게이트가 없는 디램과는 현격히 다른 현상입니다. 결국 원하는 채널을 형성하려면 게이트 단자에 인가되는 전압이 기준이 아니라 기판(채널)에 도달하는 전압을 기준으로 추가할 전압을 역으로 산출하여 게이트 단자에 인가해야 합니다.

커플링 비율(Coupling Ratio)에 따른 게이트 전압 강하

▲ 게이트 유기전압

플로팅 게이트가 없는 DRAM의 경우 절연막이 1개 층이므로, 절연체 내 쌍극자 현상으로 인해 게이트 전압이 거의 대부분 기판에 도달합니다. ▶<수직축으로 본 전자들의 여행: MOSFET> 편 참고 비휘발성 메모리의 게이트 전압 강하는 2개의 절연막을 거치면서 절연막이 커패시터의 역할을 하게 되고, 그로 인해 발생된 커패시턴스들의 일정한 비율만큼 감소하게 됩니다. 즉 인가된 게이트 전압으로 인해 기판에 최종적으로 유기되는 전압은 인가전압(워드라인 전압)에 2개 커패시터가 만들어 낸 커플링 비율을 곱한 값이 됩니다. 서로 직렬로 연결된 2개 커패시터로 인한 비율을 커패시턴스의 커플링 비율이라 하며, Cgox/(Cgox + Ctox)가 됩니다. 반면 Cgox(게이트 단자의 상부 절연층)에 유기되는 전압은 (Ctox/Ctox + Cgox)Vgate가 되겠지요.

절연막이 형성하는 기생 커패시턴스

▲ 절연막이 형성하는 여러가지 기생 커패시턴스

실질적으로 2개의 절연막이 만들어내는 커패시턴스의 종류는 좀 더 복잡합니다. 특히 Bottom 게이트와 소스 혹은 드레인과의 사이에 각각의 다른 종류의 커패시턴스를 형성하므로, 실제 기판에 도달하는 게이트 전압은 여러 가지 기생 커패시턴스의 영향까지 포함하여 계산되어야 합니다. 더욱이 커패시턴스는 옆 Tr과 부유게이트(FG) 사이의 간섭(14개 방향)으로 인해서도 영향을 받으므로 입체적으로 계산하면 CCR(Capacitive Coupling Ratio)의 종류는 매우 많아집니다. 그에 따라 채널에 인가되는 게이트 전압은 더욱 복잡한 함수관계가 될 수밖에 없습니다.

게이트 전압의 목적은 궁극적으로 채널을 형성시키고 또 더 나아가서 채널의 두께를 조절하는 것입니다. 채널의 두께에 가장 민감하게 영향을 끼치는 것이 게이트 전압이 되겠지요. 하지만 워드라인에서 게이트 단자를 거쳐 실질적으로 기판(채널)에 도달하는 전압을 정확하게 측정할 수도 없고, 그로 인해 최종적으로 얻은 결과치인 채널의 두께를 유추하여 계산하기도 만만치 않습니다. 그럼에도 불구하고 드레인 전류량의 측정을 통해 미지의 세계의 움직임을 역추적하여 Tr 구조에서부터 공정변수 및 상수를 관리해야만 제대로 동작하는 Tr이 만들어집니다. 예를 들어 공정상수에 따라 반도체 제조 시에 얼마의 가스량을 투입하고 시간을 유지할 것인지 등을 결정하게 되지요. 집적도가 높아질수록 Tr의 전압과 전류값이 줄어들 수밖에 없고, 반대로 줄어든 것만큼 미약한 신호를 정확하게 측정하기는 더욱 어려워지지만, 이를 극복할 노하우는 계속 발전되어야 할 것입니다.

※ 본 칼럼은 반도체/ICT에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.