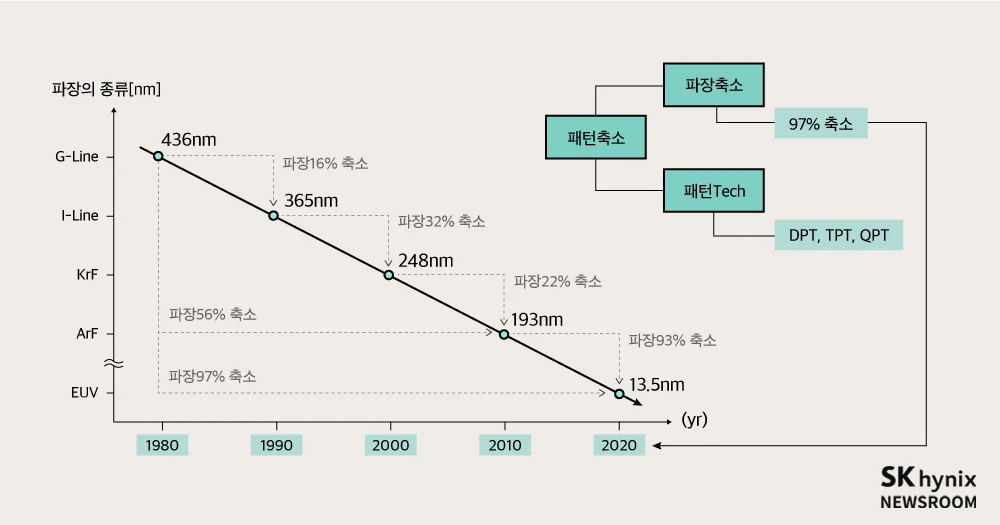

1. 패턴의 크기를 줄이는 방식: 파장과 SPT(Spacer Patterning Technology)

<▲그림1> 파장의 진화: 1980년대 파장 대비 97% 축소

패턴의 크기를 줄이는 방법으로는 파장을 축소하거나, 기술적으로 패턴을 새롭게 찍어내는 방식이 있습니다. 파장 축소는 가장 원초적이고도 효과적인 방식으로, 작은 패턴으로 PR(Photo Resist, 감광액)을 감광시켜 진행합니다. 파장 축소 방식은 1980년대 대비 패턴의 크기를 약 97%를 줄이는 성과를 거둔 매력적인 방식으로써, 앞으로도 활발하게 쓰일 것으로 보입니다.

그 외 스페이서(Spacer, 게이트 단자를 보호하는 절연물질)를 형상화하는 방식인 SPT(Spacer Patterning Technology)를 적용한 DPT(Double SPT), TPT(Triple SPT), QPT(Quadruple SPT) 등의 다양한 방식으로 선폭을 2분의 1, 4분의 1, 8분의 1로 축소해 나가고 있지요. ▶<[반도체 특강] 스페이서(Spacer), 철갑을 두른 게이트> 편 참고

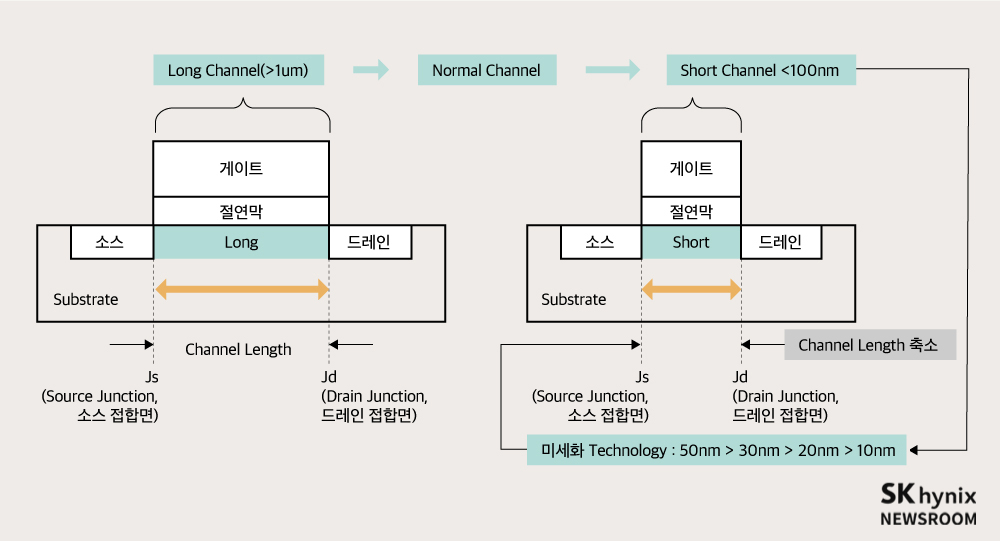

<▲그림2> 채널의 진화: Long Channel 대비 100분의 1배로 축소

채널(Channel)은 소스(Source) 단자에서 드레인(Drain) 단자까지의 물리적인 거리 내에서 형성되는 인버젼 영역(Inversion Area: nMOS인 경우 p-Type에서 n-Type으로 변경)이라고 정의합니다. 반도체 Tech.란 곧 구조적인 채널 길이(Channel length)를 의미하는데, 이는 게이트의 길이와 거의 같으며 배선 시 배선 폭을 뜻하기도 합니다. 일반적으로 이를 선폭이라고 부르지요. 한편 현재의 Tech. 기준은 과거의 S-D(Source-Drain) 거리에만 의존하는 형태가 아니라, FinFET(Fin Field Effect Transistor) 등의 영향으로 구조적인 사항 및 기타 여러 변수를 포함해 그 기준이 매우 복잡해지고 있고, 기업체 별로도 다변화되는 추세입니다.

따라서 전압을 인가했을 때의 실질적인 유효채널(Effective Channel, 물리적인 채널 길이보다는 같거나 짧음)은 소스-드레인 단자의 구조 내에서 형성될 수밖에 없습니다. 소스 단자와 드레인 단자 사이에 놓이는 채널의 길이는 Long(>1μm), Normal, Short(<100nm)로 짧아져 왔습니다. 기능적으로는 전하 캐리어가 건너갈 수 있도록 캐리어와 동일한 Type의 전하들이 모여들어 소스와 드레인을 이어주는 역할을 합니다. TR의 전체 부피가 줄어듦에 따라 채널의 길이가 비례하여 줄어들 때, 축소화로 인해 가장 영향을 많이 받는 부위가 채널입니다. ▶<[반도체 특강] Channel, MOSFET라는 세상의 다리> 편 참고

– 게이트 전압에 의한 채널 생성

nMOSFET에서 게이트 단자에 양전압을 인가할 경우 전계(Electric Field)가 게이트 단자의 하부로 전달됐다가, 게이트 단자 밑 게이트옥사이드(Gate Oxide, 절연막) 내에서는 절연입자들의 쌍극자 현상에 의해 게이트옥사이드 하부로 전달됩니다. 최종적으로 게이트옥사이드와 13족으로 도핑된 실리콘(Substrate)의 경계면까지 전달된 전계는 도핑된 실리콘 내의 전자를 끌어모아 채널을 형성하지요. 이때 채널의 폭이 형성됩니다. ▶<[반도체 특강] 공핍층, 연금술의 결정체> 편 참고

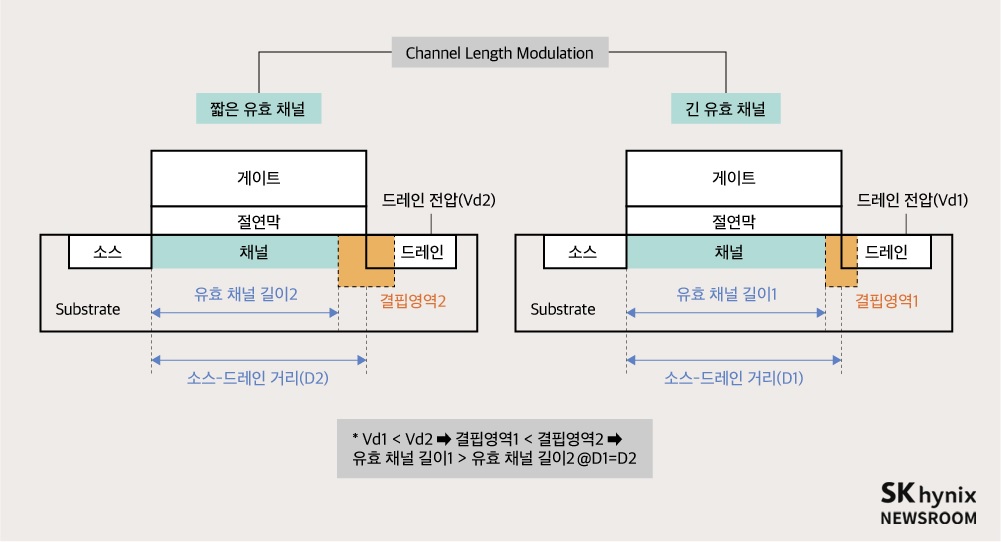

<▲그림3> 드레인 전압에 따라 연동되는 채널의 길이(Channel Length Modulation)

– 유효채널 길이 축소

구조적인 미세화(Shrink)로 인해 소스와 드레인 단자 사이에서 일어나는 가장 뚜렷한 변화는, 3개의 단자에 전압을 인가했을 때 나타나는 유효채널의 길이가 전압치에 의해 변동되는 채널 길이 변조(Channel Length Modulation)가 발생한다는 것입니다(주로 짧아짐).

nMOSFET인 경우 소스/게이트/드레인 전압을 인가하면 소스와 드레인 사이에 채널이 형성되고, 소스/드레인 단자의 소스 정션(Source Junction, Js, 소스 접합면)과 드레인 정션(Drain Junction, Jd, 드레인 접합면)에 결핍영역(Js는 순방향, Jd는 역방향)이 생깁니다. 정상적인 채널 상태라면 결핍영역으로부터 약간의 영향을 받으면서, 채널이 소스 단자에서 드레인 단자에 이르기까지 대부분의 영역에 걸쳐 연결돼야 합니다. 이때 TR의 상태는 Cut-off에서 활성 영역으로 전환된 상태입니다.

하지만 드레인 전압을 더 높이면 TR은 포화영역으로 들어가면서, 전압에 비례해 결핍영역의 범위가 넓어지고, 반대로 하강시킬 경우 결핍영역은 짧아집니다. 이에 따라 유효채널의 길이도 결핍영역이 확장 및 축소되는 것에 반비례해 축소 혹은 확장되지요. 여기서 다루고자 하는 문제는 정상적으로 드레인 전압을 인가하더라도 채널의 물리적 길이가 짧아진 상태에서는 유효채널 길이가 축소되고, 이 채널 길이가 과도하게 짧아짐으로 인해 여러 가지 문제가 발생하기 시작하지요. ▶<[반도체 특강] 사막으로의 여행, 결핍영역> 편 참고

2. 펀치 스루(Punch Through), 통제되지 않고 우회하는 전류

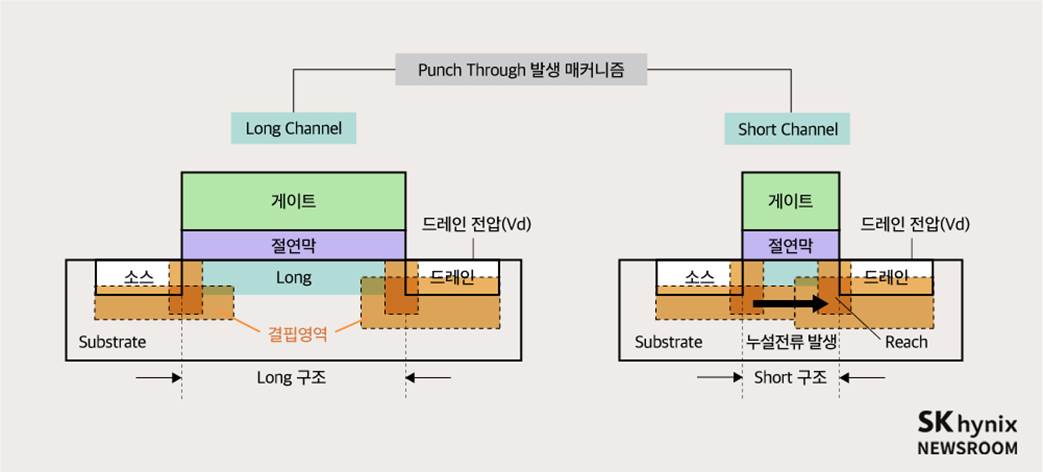

<▲그림4>; 결핍영역의 Reach로 인한 펀치 스루 발생

– 원인

소스 단자와 드레인 단자에 동작전압이 인가되면, 소스와 드레인의 각 정션(Junction)에 결핍영역이 생성됩니다. 이때 드레인의 인가전압이 더 높으므로, Js보다 Jd의 결핍영역이 좀 더 광범위하게 형성됩니다. 드레인 단자에 인가되는 전압이 상승하면 이와 비례해 Js와 Jd의 결핍영역이 더 넓게 퍼집니다. 이때 채널의 길이가 충분하다면 아무리 결핍영역의 폭이 넓어져도 가운데에 채널을 충분히 형성할 수 있으며, 게이트 전압에 의해 통제되는 채널의 온전한 기능으로 TR이 정상적으로 동작하지요.

그런데 소스-드레인 사이의 거리가 충분하지 않으면, 두 결핍영역이 서로 닿게 되어 유효채널이 매우 짧게 형성되거나 거의 형성되지 못합니다. 결국 소스-드레인의 물리적인 거리가 짧을 경우, 양쪽에서 커져 오던 결핍영역끼리 서로 닿게(Reach) 되지요. 이러한 상황에서는 게이트 전압이 인가되지 않아도 드레인 단자의 전압이 높으므로, 소스에서 드레인 쪽으로 결핍영역을 통해 전류가 흐르게 됩니다. Js에서는 순방향 전류(다수 캐리어인 전자)가, Jd에서는 역방향 전류(소수 캐리어인 전자)가 흐르는데, 이 두 전류는 전자의 흐름으로 모두 드레인 단자의 양전압으로 머리를 향하지요. 이러한 전류는 게이트 전압이 통제할 수 없는 전류로써 TR의 On/Off를 교통정리 하는 데 기여하지 못하는 누설전류(Leakage Current)가 되고, 이를 펀치 스루(Punch Through 혹은 Reach Through)라고 합니다.

Long Channel에서의 정상적인 드레인 전류는 게이트 전압에 의해 통제되고, 드레인 전압을 과도하게 증가시켜도 전류가 포화해 더이상 증가하지 않습니다. 그러나 Short Channel(유효채널)에서는 드레인 전압에 비례하여 누설전류가 무한정 이차함수적으로 증가(y=x^2로 증가)하게 되므로, 이때 계속 드레인 전압을 증가시키면 결국 TR이 파괴되거나 동작 불량 혹은 동작 불능 상태가 됩니다.

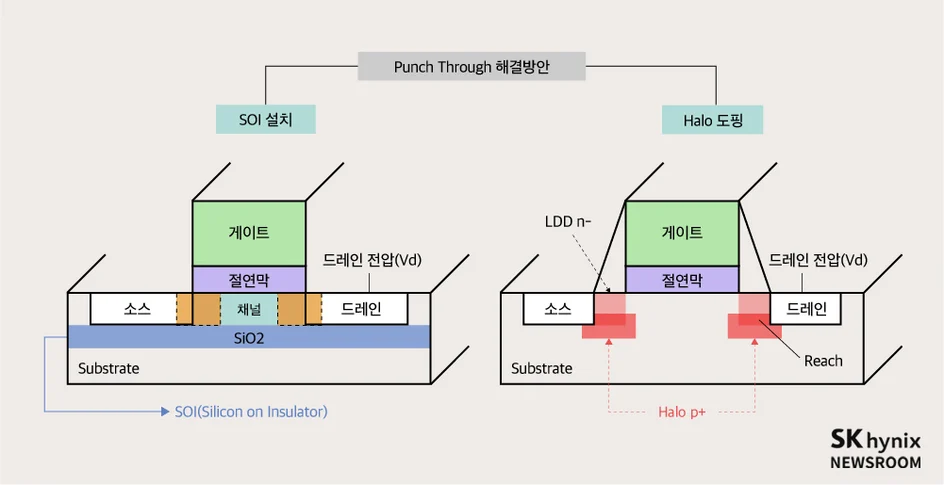

<그림5> 펀치 스루의 해결방안 2가지

– 해결방안

펀치 스루를 방지하려면, 짧아진 S-D 거리를 늘릴 수는 없고, 특히 Jd의 결핍영역이 형성될 공간을 제한 혹은 막아야 하므로, 내부를 일부 변경해야 합니다. 1) 먼저 소스/드레인 단자 하부에 절연층인 SOI(Silicon On Insulator)를 형성해 소스나 드레인 하부에 결핍영역이 형성되지 못하게 강제로 원천봉쇄합니다.

2) 혹은 구조는 기존 형태로 하되, 소스와 드레인 단자의 하부에 단자의 농도보다 더 높은 농도의 불순물로 이온주입을 해두면 결핍영역의 형성을 어느 정도 방지할 수 있습니다(Halo 도핑). nMOSFET인 경우, p+로 15족 농도의 도핑을 하고, pMOSFET인 경우는 n+로 도핑하기 위해 불순물 도즈를 가장 높게 책정해 이온주입을 합니다. 위치는 LDD(Lightly Doped Drain) 하부이므로, Halo > LDD > 소스/드레인 단자 순으로 공정을 진행합니다.

3. 누설전류(Leakage Current), 무법천지의 전류 흐름

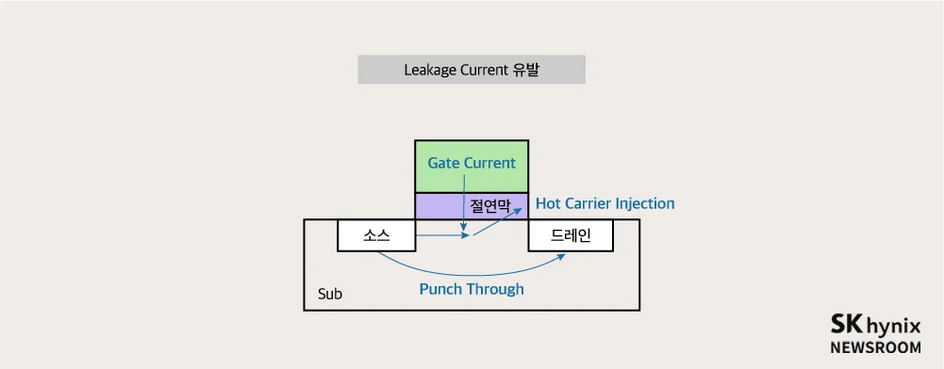

<그림6> 누설전류 3종류

– 누설전류(Leakage Current) 유발

Short Channel Effect의 대표적인 이슈는 누설전류(Leakage Current)입니다. 누설전류의 종류로는 TR이 Off 모드임에도 불구하고 흐르는 Off Current Leakage와, On 모드일지라도 문턱전압 이하에서는 흐르면 안 되는 Subthreshold Current Leakage 등이 있지요.

또한, SiO2의 두께가 얇아 어쩔 수 없이 게이트에서 절연막을 통과해 기판으로 흐르는 Gate Current Leakage가 있으며, 소스에서 드레인 단자로 정상적으로 전류가 흐르다가 절연막의 두께가 얇아져 게이트 전압에 이끌려 채널에서 절연막으로 올라가는 전자 무리도 있지요(Hot Carrier Injection). 이 전자들은 실리콘과 절연막의 경계면에 Trap이 되어 문턱전압을 교란하고, 절연막을 뚫고 게이트로 진입하기도 합니다. 특히 소스-드레인 사이가 좁아져 채널 상에 드레인 전압으로 인한 전계가 커짐으로써 Hot Carrier들이 더욱 활성화되지요.

펀치 스루 현상에 의해 발생한 누설전류의 경우, 포화 전류 특성을 보이지 않고 흘러서, 관리되지 못하는 전류로 증가합니다. 그런데, 드레인 전압에 의해 소스와 채널 사이의 전위장벽이 낮아지는 현상인 DIBL(Drain-Induced Barrier Lowering)은 누설전류보다는 에너지적인 특이현상을 다루고 있습니다. 드레인 전압이 Jd에만 영향을 주어야 함에도 채널이 좁아지다 보니 본의 아니게 채널 건너의 Js까지 영향을 끼쳐 전위장벽을 저하시킴으로써(결핍영역을 축소시킴) 소스에서 순방향 전류가 더욱 쉽게 빠져나오도록 합니다. 이 모두 계산에 없었던 과다전류가 흐르는 현상들이지요. ▶<[반도체 특강] 게이트 옥사이드의 기능과 신뢰성> 편 참고

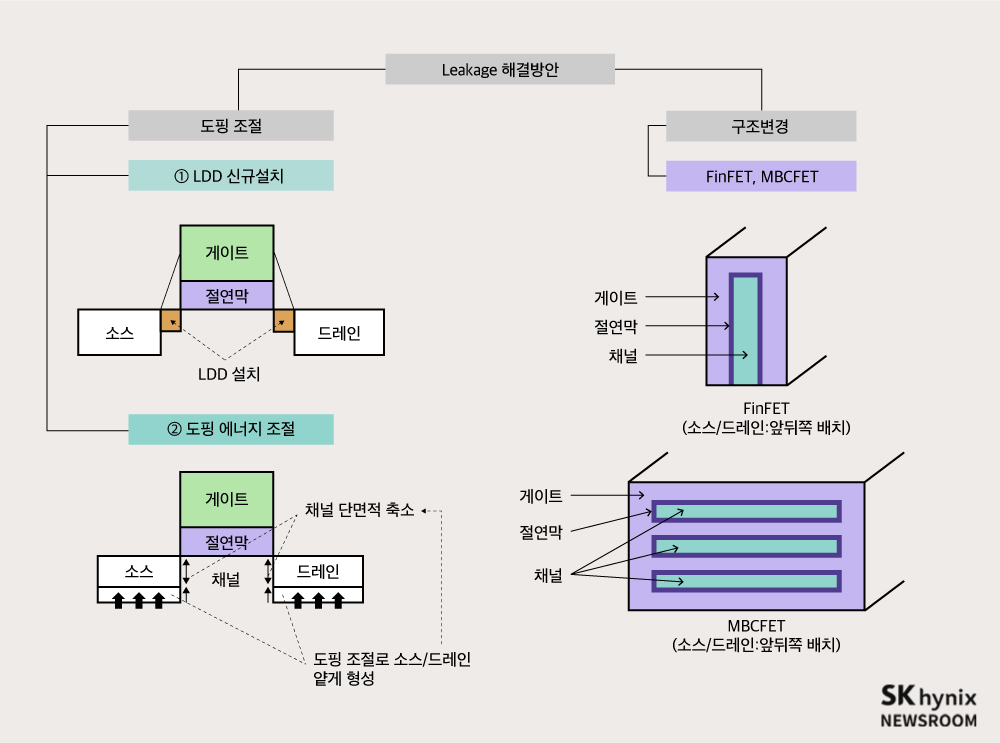

<그림7> 펀치 스루의 구조적 해결방안: FinFET, MBCFET

– 물리적 해결방안

먼저 구조로 인한 문제는 구조로 해결합니다. 앞서 설명한 SOI뿐 아니라 게이트 구조를 FinFET 구조로 변경하면, 게이트 영역이 대부분의 채널 영역을 ‘ㄷ’자 혹은 ‘ㅁ’자 형태로 감싸서, 드레인 전압으로 인한 결핍영역을 최소화합니다. 최근에 개발된 MBCFET(Multi-Bridge Channel Field Effect Transistor)는 x[nm] 폭의 채널을 4면으로 감싸는 형태로 발전하고 있어, 여러 누설전류를 방지하거나 줄이는 데 효과를 보입니다. 이는 평면 타입에서는 누설전류가 흘러도, 상기와 같이 입체적 구조가 발전한 Fin-Type과 MBC-Type에서는, 결핍영역이 발생할 공간을 허락하지 않습니다. 또한 평면 타입보다 채널 면적을 2배 이상 접촉하므로 그만큼 관리 능력도 높아지지요.

– 화학적 해결방안

도핑 방식으로는 LDD를 이용합니다. 소스/드레인 단자에 단자보다는 약간 약하게 이온주입(nMOS인 경우 n- 혹은 pMOS인 경우 p-)을 할 경우, 소스/드레인 정션에 발생하는 순방향/역방향의 결핍영역이 채널영역에서 차지하는 범위가 줄어들어 채널 길이를 길게 해주는 효과가 있습니다. 또한 소스/드레인 단자에 이온주입하는 경우, 주입 에너지를 약하게 하면 소스/드레인 단자의 물리적 깊이가 얕아집니다. 이러면 채널의 단면적을 줄이는 효과가 발생해 높은 드레인 전류의 흐름을 어느 정도 간접적으로 막아주는 역할을 합니다. 전체 구조가 축소되면 이온주입 에너지도 같이 줄어드는 방향입니다. 그러나 이때 저항성을 과도하게 높이지 않도록 주입 에너지를 단계별로 낮춰 가며 조절해야 합니다. 정상적인 드레인 전류 값마저 낮춰서는 안 되기 때문입니다.

※ 본 칼럼은 반도체/ICT에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.