트랜지스터 중에는 전류를 이용해 동작시키는 BJT와, 전압을 이용해 동작시키는 FET가 있습니다. 전류를 이용하려면 단자들 간에 전자가 잘 흐르도록 환경을 만들어 주어야 하지만, 전압을 이용하기 위해서는 단자와 단자 사이를 절연 시켜서 전자의 이동을 막아야 합니다. 대신 절연체의 양쪽 단자에 걸리는 전압을 조절해 절연체 양쪽 편에 있는 전자들을 이합집산 시킵니다. FET소자 계열의 절연막 중에서 제일 중요한 층은 단연 게이트 단자 밑에 있는 옥사이드(산화층)인데요, 게이트의 전압 민감도를 결정해주는 이 게이트 옥사이드가 어떤 역할을 하고, 반도체 테크놀로지가 발전해 감에 따라 이 절연층이 어떤 변화를 겪는지 알아봅시다.

게이트 옥사이드의 숙제

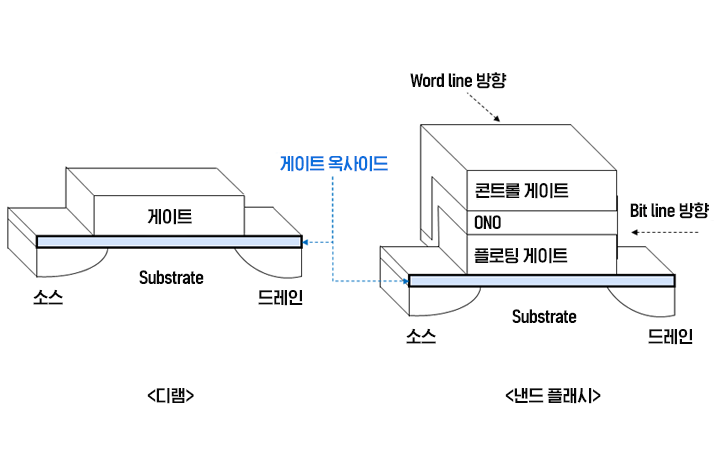

▲ 디램과 낸드 플래시에서의 게이트 옥사이드 위치 @ 출처 : NAND Flash 메모리

디램이나 다른 비메모리 제품에서의 게이트 옥사이드(Gate Oxide)는 전자의 이동을 차단하는 역할을 합니다. 절연 효과를 높이려면 절연층을 두껍게 해야 하죠. 하지만 게이트 옥사이드 층을 두껍게 하면 반대급부로 게이트에서 기판(Sub)으로의 전압에 대한 전달능력이 떨어집니다. 그래서 최종적으로 얻고자 하는 옥사이드 밑의 채널이 원하는 적절한 시간 내에 형성되지 않게 되죠. 절연과 전압의 민감도, 이 두 가지 요소가 상충되지만 디램이나 비메모리 제품에서의 게이트 옥사이드 관리는 비교적 쉬운 편이라고 할 수 있지요.

비휘발성 제품인 낸드 메모리에서는 상황이 좀 더 복잡합니다. 낸드 Tr이 스위칭 기능을 할 때는 디램과 동일한 역할을 합니다. 그런데 여기에 추가하여 낸드 Tr은 전자를 플로팅 게이트 내에 장기간 가두기도 합니다. 그럴려면 게이트 옥사이드 막을 두껍게 하는 것이 유리하죠. 반면 전자를 게이트 옥사이드 막을 통과시켜 플로팅 게이트로 넣거나 혹은 플로팅 게이트에서 채널쪽으로 전자를 빼내야 하는 경우에는 게이트 옥사이드 막이 얇아야 유리합니다. 두꺼우면 전자가 잘 통과하지 못하면서 낸드 메모리의 동작상 어려움이 발생됩니다. 이렇듯 게이트 옥사이드의 두께와 낸드 메모리 동작 사이에서는 서로 지향하는 바가 상충되어 낸드에겐 모순을 풀어야 하는 숙제가 디램보다 많아집니다.

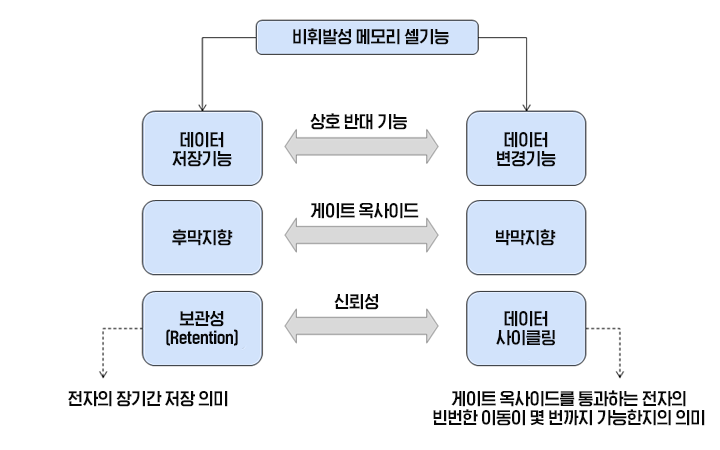

▲ 데이터의 저장기능과 변경기능의 대치 @ 비휘발성 메모리 셀

또한, 데이터의 저장기능과 변경기능이 대치한다는 문제가 있습니다. 세상에는 서로 상반된 입장을 동시에 함께 해결해야만 하는 경우가 종종 발생하는데요. 멀리 빨리 가고자 할 때 속도를 높이려면 적은량의 연료가 유리하지만, 멀리 이동하려면 연료량이 많아야 하는 경우라고 할 수 있습니다. 셀(Cell) 입장에서는 데이터의 저장기능과 데이터의 변경기능은 상호 반대되는 기능인데, 이러한 모순이 셀이라고 하는 무한히 작은 물리적 공간 내에서 부딪칩니다.

게이트 옥사이드의 신뢰성과 동작속도

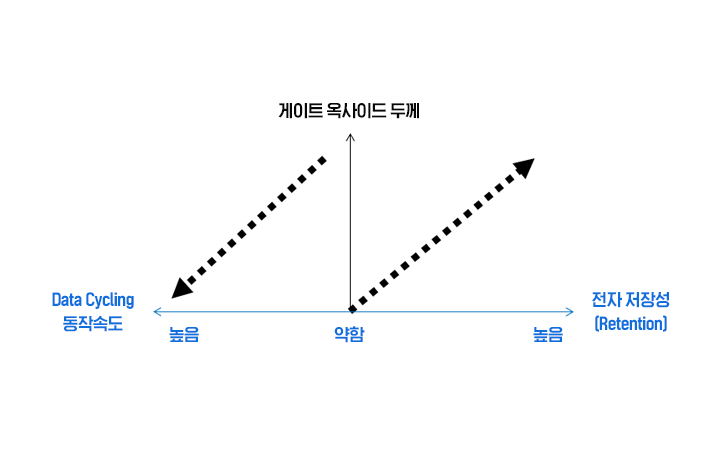

▲ 게이트 옥사이드 두께 대비 전자의 저장성과 동작속도 @ 비휘발성 메모리

비휘발성 메모리 셀의 신뢰성 측면을 보아도 마찬가지입니다. 게이트 옥사이드는 게이트 내에 전자를 잘 가둘 수 있어야 하고(데이터의 보관성 혹은 저장성 : Data Retention), 또 필요시 절연층을 통과시켜 전자를 게이트 단자 속으로 자주 넣고 빼내는 동작을 반복해야 합니다.(Data Cycling 동작) 전자가 게이트 옥사이드(절연막)를 관통해 빠져나간다는 것은, 낸드플래시의 경우 게이트 단자에 저장된 데이터를 삭제하는 동작(Erasure)을 의미합니다. 삭제 동작을 해야 새로운 데이터를 셀에 다시 저장할 수 있기 때문이죠. 전자를 게이트 단자 내에 잘 가둬 두려면 게이트 옥사이드가 두꺼워야 하고, 전자를 빠르게 넣고 빼내는 데이터 사이클링이 원할하게 되려면 절연층이 되도록 얇아야 쉽습니다.

게이트 옥사이드의 두께는?

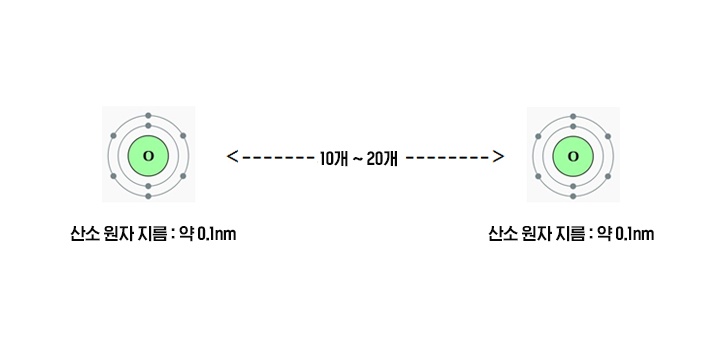

▲ 게이트 옥사이드 두께 : 산소 원자 10개 ~ 20개를 늘어놓은 두께 @ 그림 출처 위키피디아

그렇다면 게이트 옥사이드 막의 두께는 얼마로 해야 할까요? MOSFET 공정 중에서 가장 심혈을 기울여 만드는 절연층이 게이트 옥사이드입니다. 반도체에서는 게이트의 크기 혹은 채널 길이로 반도체의 테크놀로지를 가늠하는데요. 게이트 층을 형성시키는 것 보다 게이트 옥사이드를 형성하는 것이 더 어렵다고 볼 수 있습니다. MOSFET의 지상과제는 소비전력을 낮추고 MOS동작속도를 높이는 것입니다. 이를 위해서는 게이트 옥사이드의 두께를 최대한 얇게 해야 합니다. 게이트 옥사이드 두께는 약 2nm(나노미터) 정도로 유지 해왔는데, 최근에는 1nm가까이로 더욱 얇아지는 추세입니다. 1nm는 10의 –9제곱(10^-9) 미터인데, 산소 원자의 지름이 약 0.1nm이므로 게이트 옥사이드 두께는 약 10개에서 20개 정도의 산소원자가 늘어선 정도로 볼 수 있습니다.

게이트 옥사이드의 절연성을 높이기 위하여

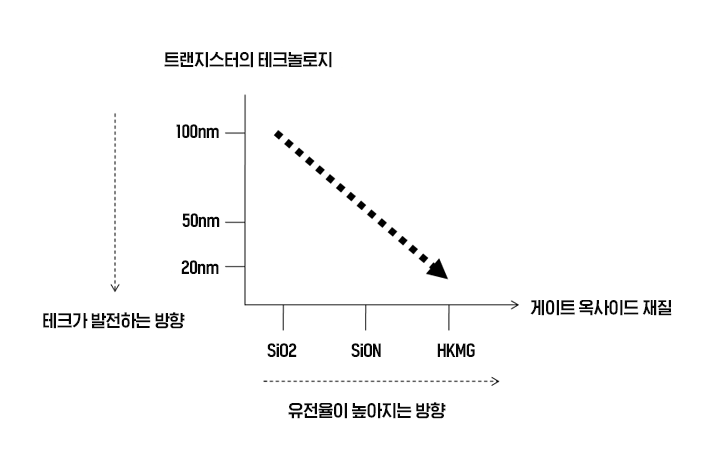

▲ 테크놀로지에 따른 게이트 옥사이드의 재질 변화 : SiO2 > SiON > HKMG

테크놀로지가 발전해갈 수록 게이트 옥사이드의 두께는 감소하지요. 그런데 게이트 옥사이드의 두께가 줄어도 Tr의 기본적인 기능이나 성능은 유지해야 하기 때문에 옥사이드의 절연성을 높이기 위해서는 게이트 옥사이드의 재질을 유전율이 높은 것으로 해야 합니다. 소스단자와 드레인단자 사이의 거리(Tr의 Technology)가 100nm까지는 게이트 옥사이드로 실리콘산화막(SiO2)이란 절연체를 사용했습니다. 하지만 Tr의 50nm 테크놀로지 전개 기간에서는 게이트 옥사이드의 두께가 반으로 줄어들었고 그에 따라 절연성이 높은 실리콘산질화막(SiON)을 사용했죠. 그러나 또 50nm의 절반인 25nm Tech에서는 게이트 옥사이드의 두께가 더욱 줄어들었고, 두께가 줄어든 만큼 절연성을 높이기 위해 유전율이 매우 높은 high-k 물질을 사용하기 시작 했습니다. (거꾸로 관점을 바꾸어 보자면, 유전율이 높은 물질이 개발되면서 게이트 옥사이드의 두께를 그에 맞는 만큼 줄일 수 있게 된 것이죠.) 이를 HKMG라고 하여 high-k, metal gate라 부릅니다. 게이트단자는 초창기에는 metal 재질로 했었지요.(1990년대 이전에 이미 게이트는 여러 가지 물질을 섞어서 poly게이트 단자를 만들었기 때문에 HKMG 보다는 HKPG라고 부르는 것이 더 나았을 듯 합니다.)

게이트 옥사이드 막의 두께에 따른 장단점

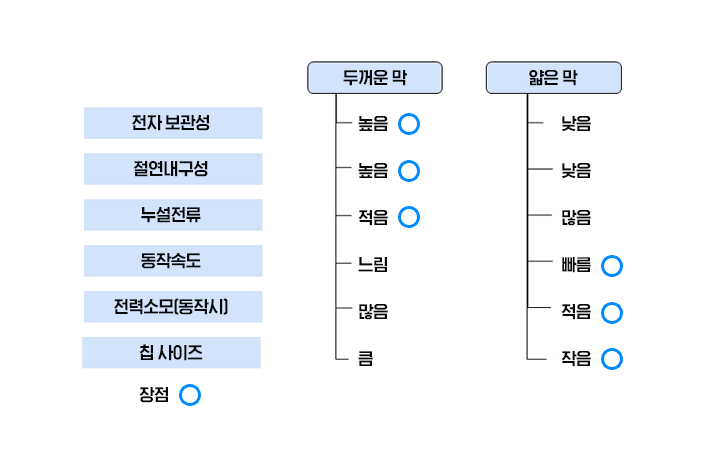

▲ 게이트 옥사이드 막의 두께에 따른 장단점

정리를 하자면, 게이트 옥사이드의 막이 후막인 경우에는 전반적으로 신뢰성이 높아집니다. 게이트 내에 전자를 보관한다거나, 게이트와 기판 사이에서 전자의 왕래로 인한 절연막의 파손이라던가 하는 데미지가 줄어들게 되지요. 그러나 낸드 메모리 같은 경우, 게이트 옥사이드가 두꺼워지면 전자가 두꺼운 막을 통과할 때 전자들이 게이트 옥사이드 막에 끼어 원치 않는 문제를 일으킬 확률이 높아집니다(Trapping 전자). 한편 두꺼운 만큼 누설전류는 덕분에 줄어들죠. 소자가 동작을 할 때는 드레인 전류가 크기 때문에 게이트 옥사이드를 통과하는 누설전류가 소자 동작에 크게 영향을 끼치지 않지만, 소자가 스탠바이(Standby) 상태에서는 두께가 너무 얇은 경우 누설전류가 과도하게 많아져 문제가 됩니다. 더군다나 한 개의 칩 내 셀(Cell)의 수가 10억개 이상 셀 수없이 많아지는 경우, 누설전류를 전부 합하면 이 또한 큰 부담이 됩니다.

반면 박막인 경우는 반대현상이 나타납니다. 막의 두께가 얇아지면 반비례하여 박막이 깨지기 쉬워지고 전자를 저장하기도 어려워지죠. 하지만 얇은 만큼 게이트의 전압이 채널로의 전달 속도가 빨라져서 트랜지스터의 ON/OFF 스위칭 성능이 높아집니다. 특히 낸드 셀 안에 데이터를 저장한다거나 저장된 데이터를 지우는 동작 속도가 급격히 향상됩니다. 즉 영화를 다운 받거나 사진을 변경하는 속도가 그만큼 빨라지게 됩니다. Fab 제조 시에도 얇은 만큼 기술적으로 어렵기는 하지만 공정에서 소모되는 시간도 자연적으로 단축되는 것입니다. 추가적으로 또 하나의 가장 중요한 변수인 칩 사이즈를 축소(Shrink)시키려면 당연히 게이트 옥사이드의 절연막은 얇게 또 얇게 가야 합니다.

지난 시간에는 산화막의 일반적인 용도와 특성에 대해 알아보았습니다. 이번 시간에는 약간 복잡했지만 산화막 중에서도 좀 더 특정한, 게이트 옥사이드라는 게이트 하단에 위치한 절연층을 살펴보았고요. 이와 연관된 소자의 동작 기능과 신뢰성, 그리고 게이트 옥사이드가 지향해가는 방향에 대하여 공유했습니다. 절연체들은 단순히 절연하는 층 자체로만 존재하는 것이 아니라, 반도체 소자의 Technology에서부터 성능 혹은 전압 소모 등 환경적인 변수까지를 결정하는 전략적이고 중요한 요소가 된답니다. 다음 시간에는 게이트 옥사이드를 Fab 공정적으로 어떻게 형성하는지를 알아보겠습니다.

※ 본 칼럼은 반도체/ICT에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.