세 개의 몸통으로 구성된 트랜지스터는 두 군데에서 경계면이 존재하게 됩니다. 마치 3개 영역으로 구성된 캐나다-미국-멕시코 간에 2개의 국경선이 설치되어 있는 것을 연상하면 되겠군요. 반도체 혹은 트랜지스터 내부에서 일어나는 일의 많은 부분은 경계면을 사이에 두고 발생되기 때문에 경계면(계면) 형성 과정과 계면 주변의 변화를 알고 나면 트랜지스터를 보다 더 쉽게 이해할 수 있답니다. 경계면을 형성하는 과정은 간단하게 이전 글 ‘점 접촉 트랜지스터’(▶해당글 보러가기)에서 살펴보았으니, 이번 시간에는 N형-P형 경계면 사이의 전자 혹은 정공의 움직임에 대하여 알아보도록 하겠습니다.

FET(Field Effect Transistor)에는 사막이 두 군데 있다?

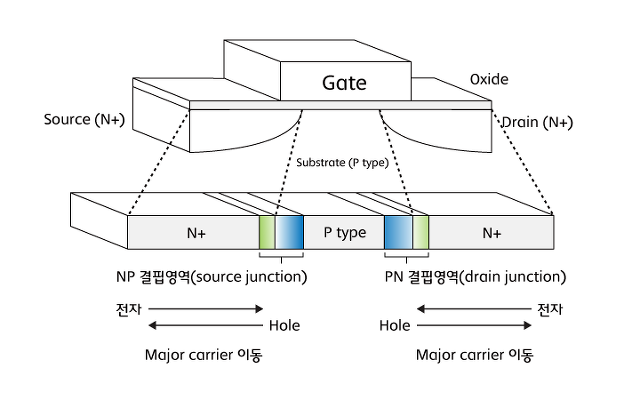

▲ MOSFET에 형성되는 결핍영역, 출처: “NAND Flash 메모리

FET에서는 Source단자와 기판(Substrate)이 서로 맞닿아 있는 부분인 Junction 양쪽으로 일정한 두께까지는 결핍영역이라는 비활성 영역이 생성됩니다. 이는 Drain단자와 기판 사이도 마찬가지이지요. 결핍(Depletion) 영역이 형성된 이후에는 결핍영역 내부에서는 더 이상 자생적으로 발생되는 이동자들은 없습니다.

거의 생명현상이 일어나지 않는 사막과 같이, 외부의 Input이 없는 한 더 이상 캐리어들이 활동하지 않는 조용한 지역이 됩니다. 그러나 결핍영역끼리는 서로에게 계속적으로 전계를 행사하면서 상대방을 주시하고 있는 긴장관계에 있답니다. (‘결핍영역’은 최근에 우리나라 표기 방식으로 정해졌습니다. ‘공핍층’은 일본에서 표기한 단어입니다. 학계/산업계에서는 오랫동안 광범위하게 공핍층이라고 사용되었으므로 이후부터는 혼돈을 방지하기 위하여 일단 공핍층이라 표현 하겠습니다.)

공핍층, 전자-정공의 전투 현장

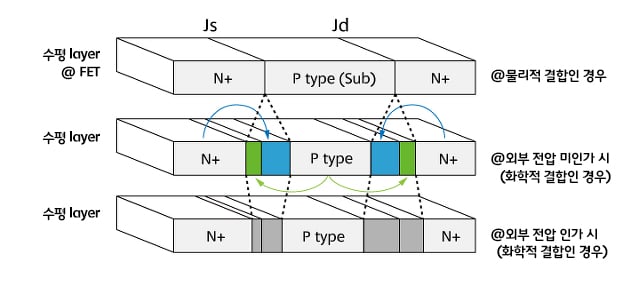

▲ 외부전압을 인가하지 않는 경우의 공핍층 형성 @ Js : Source Junction, Jd : Drain Junction

‘결핍’ 혹은 ‘공핍’이란 직설적으로는 활성화된 이동자들이 없을뿐더러, 상대방을 공격할만한 캐리어들이 모두 소진되었다는 의미이지요. 불순물반도체인 단자 내에는 이동자(Carrier)들이 많은데, 결핍영역에는 캐리어들이 왜 없을까요? 이미 Source단자의 전자캐리어와 기판의 정공캐리어가 서로 상대방 지역으로, 넘어갈 만한 캐리어들은 모두 넘어가서 전부 전사하였기 때문입니다. 단, 이 경우 전제 조건은 Source단자와 기판 사이는 화학적 결합이 되어있어야 가능합니다. 이제 그 캐리어들의 이동 과정과 이동 후에 주변에 끼친 영향에 대하여 단계별로 알아봅시다.

다수 캐리어의 원동력, 농도차이에 의한 확산에너지

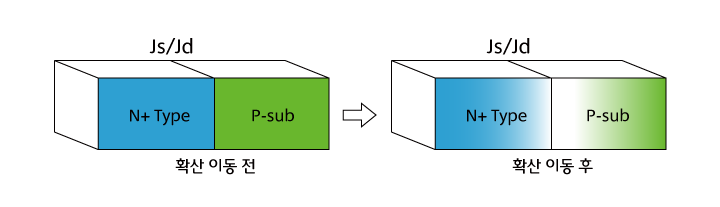

▲ 다수캐리어의 확산이동 전,후 비교

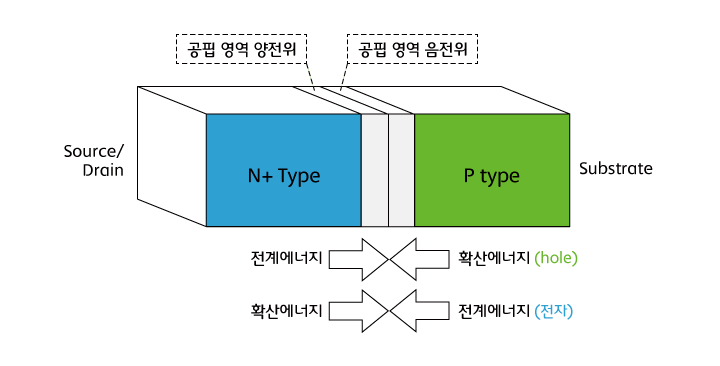

이러한 소멸이동은 외부에서 어떠한 전압도 FET단자로 인가되지 않고 자체적인 확산에너지만으로도 자생적으로 발생합니다. N+ Source단자, P-substrate(기판), N+ Drain단자가 화학결합이 되면 다수캐리어인 전자와 hole의 농도차이에 의하여 높은 농도 영역에서 낮은 농도 영역으로 캐리어들이 확산되어 나아가지요. 물속에서 잉크가 확산되듯이 말입니다.

그러나 엔탈피가 고체보다 높은 유체 속에서의 확산은 유체 전체 지역으로 확산하지만, 고체 내에서의 확산은 캐리어가 어느 정도 진격하다가 확산에너지가 떨어지면 상대방의 영역에서 더 이상 나아가지를 못하고 그 자리에서 멈춥니다.

공핍층을 만드는 다수 캐리어의 이동 메카니즘

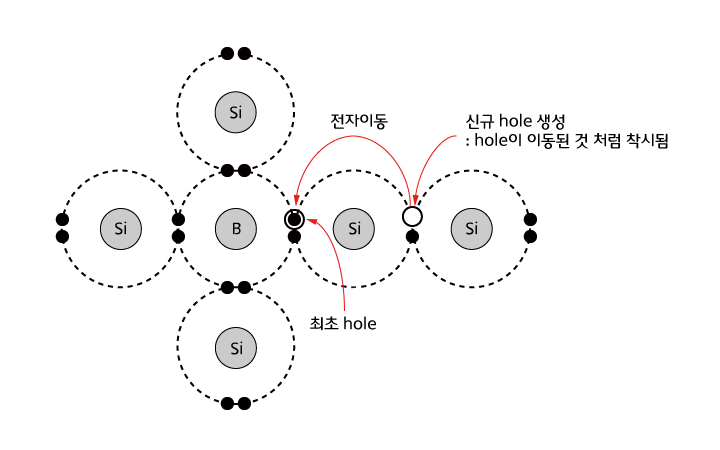

▲ 이웃 인접전자이동으로 인한 다수캐리어인 정공의 이동방식

Source Junction(Js)을 기준으로 좌우를 살펴보면, N+ Source단자의 Major Carrier인 전자 농도가 P-sub 내의 Minor Carrier인 전자 농도 보다 높기 때문에 전자가 Source단자에서 P-sub로 이동하고, P-sub의 Major Carrier인 hole농도가 N+ Source단자내의 Minor Carrier인 hole농도 보다 높기 때문에 hole이 P-sub에서 Source단자로 확산되어 들어갑니다. Drain Junction(Jd)에서도 동일한 이동 메카니즘이지요. 소수캐리어도 이동은 있습니다만, 소수캐리어의 영향은 다수캐리어에 비하여 미미하므로 여기서는 다루지 않습니다.

전자캐리어의 확산은 여기(에너지를 얻은 상태)되어 원자핵의 사정거리로부터 벗어난 자유전자가 직진형 랜덤(Random) 운동 형태로 이동합니다. 이동 경로와 방식이 간단하지요. 반면, 정공캐리어의 확산은 인접원자의 최외각전자가 옆에 있는 정공 속으로 뛰어 들어오는 동작형태입니다. 이는 Waiting-Jumping인 징검다리 이동으로 이동속도가 전자이동에 비하여 상대적으로 늦지요.

동일한 거리 조건이라면, hole을 채우는데 소요되는 에너지는 원자를 떠난 자유전자가 원자 내에 묶여 있는 인접최외각전자에 비하여 더 적기 때문에, 자유전자가 hole로 들어가기가 더 쉽습니다. 그러나 두 소립자(원자핵-전자)간의 서로 당기는 인력은 거리의 제곱에 반비례하지요. 따라서 자유전자와 hole간의 평균거리가 인접최외각전자와 hole간의 평균거리 보다 멀어서 인접최외각전자와 hole간의 인력이 더 큽니다. 결국 hole을 기준으로 볼 때, hole을 채우는 개체수는 자유전자 보다는 인접최외각전자가 더 많이 기여 하겠지요.

음의 Acceptor 이온, 양의 Donor 이온

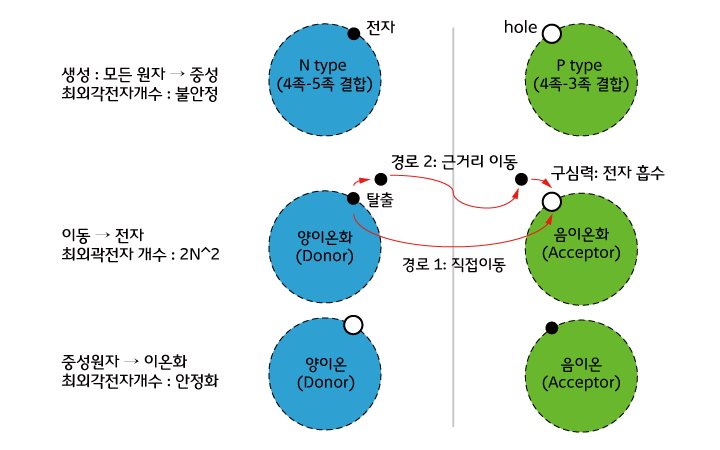

▲ 전자 이동에 의한 Donor와 Acceptor간의 조화(원자 level)

공핍영역에서의 원자 입장을 보면, 전자를 기준으로 ‘전자를 내준 원자는 Donor, 전자를 받은 원자는 Acceptor라 합니다. P-sub내의 Source Junction(Js)에 인접해 있는 원자는 처음에는 중성상태이었다가 전자를 받아서 1개 전자전하량만큼 증가된 음의 Acceptor이온으로 변하지요.

반면, N+ Source내의 Js에 인접해 있는 원자는 중성상태이었다가 전자를 내주어 Donor가 양이온으로 변합니다. 전자(중성원자에 소속)들이 hole(중성원자에 소속)을 메우면, 그 즉시 전자와 정공은 동시에 소멸하면서, 전기적으로 음성과 양성이 편을 갈라섭니다. 확산에너지가 전계 에너지로 변환된 것이지요.

이 경우에서는 극성에 의한 인력보다는 원자핵에 의한 인력이 더 크게 작용했습니다. 즉 1개 전자로 인한 인력보다는 최외각전자궤도를 2N^2(N=궤도순번)으로 안정화 시키는 힘이 더 크다고 할 수 있지요. 그리고 인접최외각전자의 이동로도 두 경로가 발생됩니다. 하나는 궤도간의 직접이동이고, 다른 하나는 인접최외각전자가 상온에서 여기되어 원자를 탈출하였다가 바로 인접된 원자핵의 인력에 이끌려서 hole로 들어가는 경로입니다.

확산에너지와 전계에너지

▲ 확산에너지와 전계에너지가 평형을 이룬 상태(단자 level)

지금까지는 원자 level에서 설명하였습니다만, 이제는 원자가 집단을 이룬 광대한 영역인 단자를 생각해 봅니다. N+ Source/Drain 단자는 불순물 반도체 일지라도 일단 반도체 공정에서 Termination으로 형성될 당시는 모두 중성 상태가 되겠지요. 다만 N+ 단자는 P-sub(정공이동)에 비하여 외부에서 작은 에너지만 인가해도 전자가 쉽게 여기할 수 있고, 순수반도체 재질로부터 전자를 뽑아내는 것에 비하여도 더더욱 쉽습니다. 에너지 상태로의 좀 더 상세한 설명을 원하면 관련된 전공 서적(NAND Flash 메모리)을 참고하면 되겠습니다.

다수의 전자가 N+ Source로부터 인해전술로 확산해오면, 계면에 접한 P-sub의 영역은 가까운 곳에서부터 음극(-)단자화 되고, N+단자의 Js 근방영역은 전자들이 빠져나가 양극(+)단자로 변합니다. 그러면 N+ type단자의 공핍영역(양극단자)과 P-sub의 공핍영역(음극단자) 사이에는 전계가 형성되지요. 이렇게 형성된 전계 방향은 확산에너지가 작용하는 방향과 정반대가 되겠습니다. 또한 확산현상이 지속될수록 캐리어가 많이 이동하여 전계가 강해지는 효과가 있습니다. 결국 확산에너지와 전계에너지가 평형을 이루는 시점에서 캐리어의 확산이동이 멈추지요.

콘덴서 기능을 하는 공간전하영역

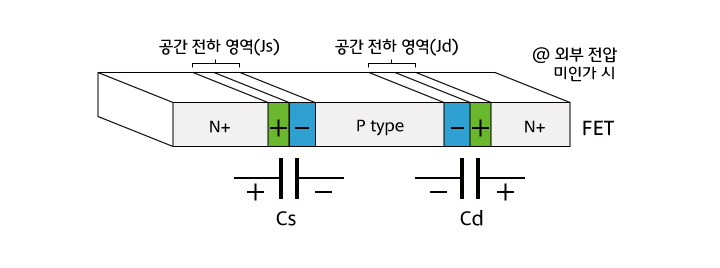

▲ Capacitor 역할을 하는 공간전하영역

공핍층을 공간전하영역 혹은 공간전하층이라고도 부릅니다. 이는 Junction 양 옆으로 인접된 2개의 공간전하영역이 콘덴서 역할을 수행하기 때문입니다. 서로 다른 캐리어들이 상대방 영역으로 들어가서 더 이상 움직이지도 않고 정체하고 있으면서 공간에 양/음전하를 쌓아 놓은 모양새인 것입니다.

따라서 이때에 영향을 미치는 Capacitance(C∝A/d)는 거리에 반비례하고 단면적에 비례 하므로 FET구조가 미세화 될수록 용량은 작아지겠지요. 물론 어떤 단자들의 재질을 사용하느냐에 따라 용량상수인 ε값이 변동하여 그에 따라 전체 용량값이 약간의 차이가 나지만 말입니다. 사실 공핍층에 의하여 전계가 형성되었다는 말이나 공간전하영역이 Capacitor 기능을 한다는 말은 같은 현상을 다르게 표현한 것이지요.

MOSFET 트랜지스터, 특히 MOSFET를 이용한 NAND Flash 메모리는 수직축, 수평축, 대각선축 등 사방팔방으로 전하들이 쌓이는 용량덩어리입니다. 메모리 기능을 기준으로 볼 때, 긍정적으로 작용하는 용량형태도 있지만 MOSFET의 미세화로 인하여 전체적으로는 용량값을 줄이는 방향이므로, 적절한 용량을 갖도록 재질과 구조를 선택하는 것이 아주 중요합니다. 공간전하층의 두께나 용량값이, 달성하고자 하는 목표값과 차이가 날 경우, 웨이퍼 몇 천장을 버려야 하는 상황이 되기도 하므로, 칩 설계 전후와 구조를 만드는 과정들의 단계별로 눈에 보이지 않는 공핍층을 눈에 보이는 숫자로 계산을 철저히 하여야 합니다.

공핍층 두께는 불순물 타입 별로 다르다

외부전압 미인가인 경우, 공핍층의 총 형성두께는 두 Junction Js와 Jd 모두 동일합니다. (Source와 Drain 단자의 N+농도가 같을 경우). 그런데 단자별로 나누어서 보면, 농도가 높은 N+ type Source단자의 전자군사가 상대적으로 농도가 적은 P-type기판의 정공군사보다도 개체수가 더 많이 발생됩니다. 그래서 정공들이 Source단자를 침투한 영역보다는 전자들이 P-sub를 더욱 깊이까지 들어갑니다. (물론 움직이는 속도로 인한 변수도 있습니다).

이는 단자들의 태생부터 농도 차이를 두었으니 어쩔 수가 없겠지요. 공핍층 두께는 대체적으로 단자 전체 영역에 비하여 매우 작게 형성되도록 사전에 계산하여 Ion Implantation 공정의 불순물농도라던가 FET구조 등등을 거꾸로 공핍층 두께에 맞추어 설정하는 Feedback설계를 합니다. 확산거리는 약간의 복잡한 식으로 나타내지지만 어쨌든 농도에 비례하지요.

점 접촉 트랜지스터에서는 공핍층의 형성 자체부터가 단자크기에 비하여 매우 작습니다. 때문에 면 접촉 트랜지스터가 개발되면서부터 공핍층이 제기능을 했다고 볼 수 있는데요. 결핍영역(공핍층)은 수평개념의 FET축 상에서 형성되고, 수직개념의 MOS축 상과는 별개입니다. 그러나 외부에서 전위에너지가 인가될 때는 수직축 Gate로부터도 전위차가 발생되므로 작용이 좀 더 복잡해집니다. 이번 장에서는 외부에서 전위에너지가 가해지지 않는 조건에서 결핍영역을 들여다보았는데요. 다음 장에서는 전위에너지가 외부에서 가해질 때 공핍층이 변화되는 모습을 알아보겠습니다.

* 본 칼럼은 반도체/ICT에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.