새로운 메모리를 개발하기 위해 반도체 기업들은 수많은 연구를 수행했다. 이는 메모리 계층*의 관점에서 CPU(Central Processing Unit, 중앙처리장치) 혹은 D램과 SSD(Solid State Drive) 스토리지를 이어주는 가교를 만들어, 성능을 향상시키고 비용을 절감하기 위한 것이었다. 이러한 연구 끝에 최근에는 CXL(Compute Express Link)*이 등장했으며, 각 작업량에 따라 성능과 용량을 최적화하기 위한 메모리 계층이 제안됐다. 이러한 면에서 지속성과 용량 확장성을 모두 갖춘 3DXP(3D XPoint)*는 D램과 스토리지 간 격차를 줄일 메모리 솔루션으로 주목받고 있다.

이번 기고문에서는 세계 3대 반도체 학회 중 하나인 ‘2023 VLSI(Very Large-Scale Integration) 심포지엄’에서 발표된 SK하이닉스의 ‘4-Deck 3DXP’ 솔루션을 살펴보겠다. 이와 함께, 3DXP의 확장성 한계와 더불어 SOM(Selector-Only Memory)이 SCM(Storage Class Memory)의 미래를 개척할 가능성도 함께 생각해 보자.

* CXL(Compute Express Link): 고성능 컴퓨팅 시스템의 기반이 되는 PCIe 기반 차세대 상호연결 프로토콜

* 3D XPoint(3DXP): 전원을 꺼도 정보가 지워지지 않는 플래시 메모리(Flash Memory) 장점과 처리 속도가 빠른 D램 장점을 모두 갖고 있는 PCM(Phase-Change Memory) 제품. 고용량, 짧은 읽기/쓰기 시간을 자랑하며, 셀(Cell) 주소를 바이트(byte) 단위로 찾아가는 것(Byte-addressability)이 가능하다.

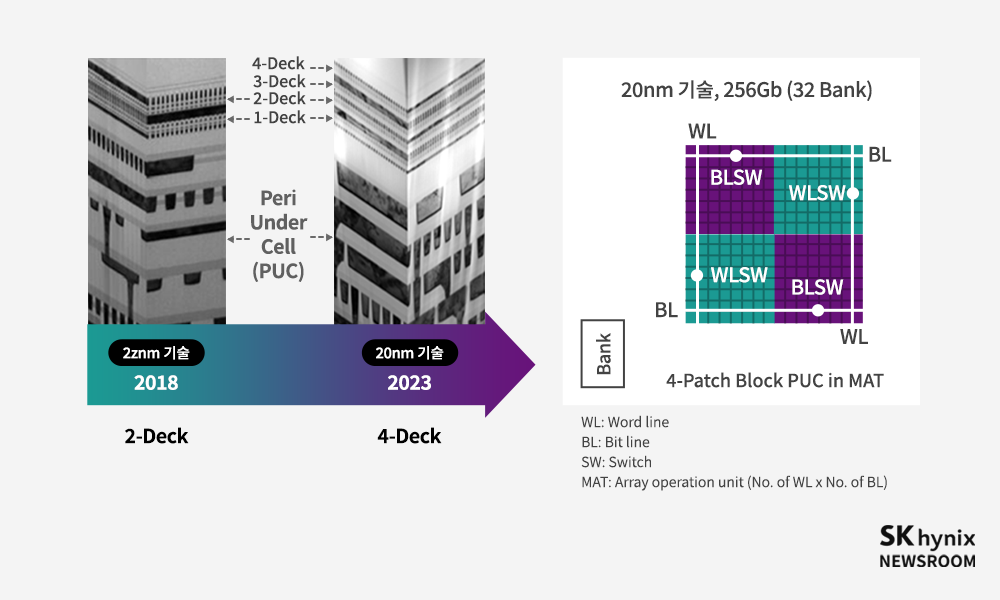

▲ 그림 1. 단면 투과 전자현미경(TEM)으로 본 다층 구리와 페리 언더 셀(Peri Under Cell, PUC)이 있는 2-Deck(2znm 기술 적용, 2018년)과 4-Deck(20nm 기술 적용, 2023년) 셀 배열(왼쪽)과 20nm(나노미터) 공정 기술을 적용한 256Gb(기가비트) 용량의 4-Deck 칩 평면도(오른쪽)

지난 몇 년간 SK하이닉스는 3DXP 메모리 솔루션 개발에 상당한 성과를 이뤄냈다. 회사는 2018년 개최된 ‘국제전자소자회의(International Electron Device Meeting, IEDM)’에서 2z*nm(나노미터) 기술을 적용한 2-Deck(데크) 64Mb(메가비트) 테스트 칩 구동 결과를 발표했고, 이어서 2019년에는 128Gb(기가비트) 칩 시연에 성공했다. 최근에는 2023 VLSI에서 20nm 기술을 적용해 향상된 4-Deck 256Gb 칩 개발 성과를 시연했다.

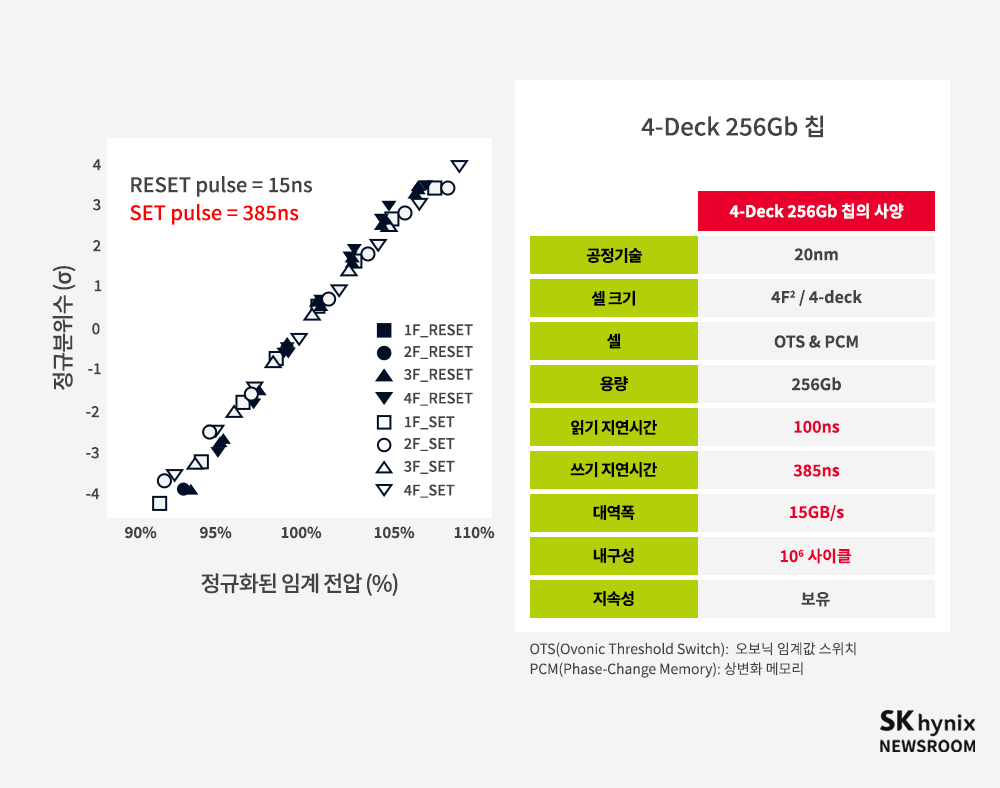

▲ 그림 2. 설정 및 재설정 동작 후, 각 Deck별 전압 분포(왼쪽), 4-Deck 칩의 구조와 동작 특성을 포함한 기본 칩 정보(오른쪽)

SK하이닉스는 최신 솔루션 개발을 위해 새로운 공정 통합 방식을 적용했는데, 여기에는 새로운 자체 정렬 식각, 세척, 화학 기계적 연마(CMP), 층간 유전체(ILD) 증착 등이 포함된다. 또한 상호연결 방식을 위해 저저항 도체 재료를 개발해 스파이크 전류를 최소화하면서 충분한 쓰기 전류의 흐름을 보장했다. 또한 20nm 기둥 패터닝 공정, 재료 설계 그리고 적절한 읽기/쓰기 작업 제어를 통해 충분한 너비의 읽기 창 마진*과 각 Deck별 1Gb 어레이의 촘촘한 전압 분배에 성공했다.

SOM으로 3DXP의 한계 극복

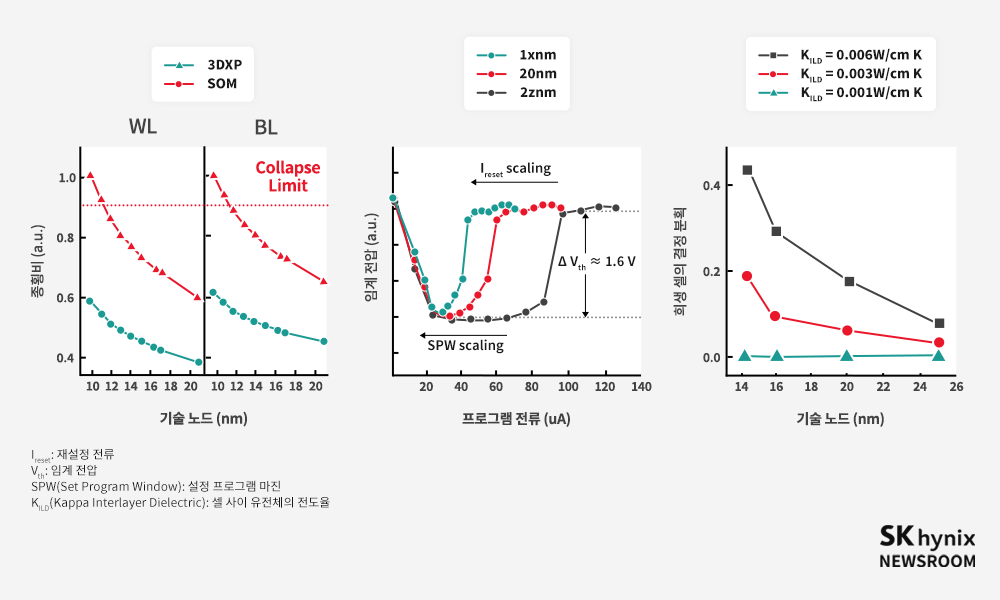

▲ 그림 3. 3DXP의 세 가지 미세화 문제: 높아진 종횡비(왼쪽) 설정 프로그램 마진(가운데) 열 교란(오른쪽)

SK하이닉스는 4-deck 256Gb 장치를 성공적으로 시연했으나, 20nm보다 더 미세화된 공정에 적용했을 때의 3DXP 확장성을 평가하면서 세 가지 문제점을 발견했다. 첫 번째 문제점은 3DXP의 구조는 상변화 메모리(PCM)*와 오보닉 임계값 스위치(OTS)*로 구성되는 데 미세화 공정 고도화로 인해 종횡비*가 훨씬 높아져 공정 통합이 복잡해진다는 것이다. 둘째, 미세화 공정 고도화에 따라 3DXP의 설정과 재설정 동작 사이에서 쓰기 프로그램 마진이 줄어드는 것이다. 셋째, 층간 유전체에서 달성하기 어려운 열 전도율 없이는 1ynm보다 더 미세화된 공정에서 열 교란에 의한 미세화의 한계가 발생할 것으로 예상된다.

* 오보닉 임계값 스위치(Ovonic Threshold Switch, OTS):2단자 대칭 전압 감지 스위칭 소자. 높은 저항 상태에서 전도 상태로 전환된 후, 전류가 유지, 전류값 아래로 떨어지면 다시 높은 저항 상태로 복귀한다.

* 종횡비(Aspect Ratio, AR): 가로와 세로의 비. 종횡비가 크다는 것은 형상이 좁지만 높다는 의미이다.

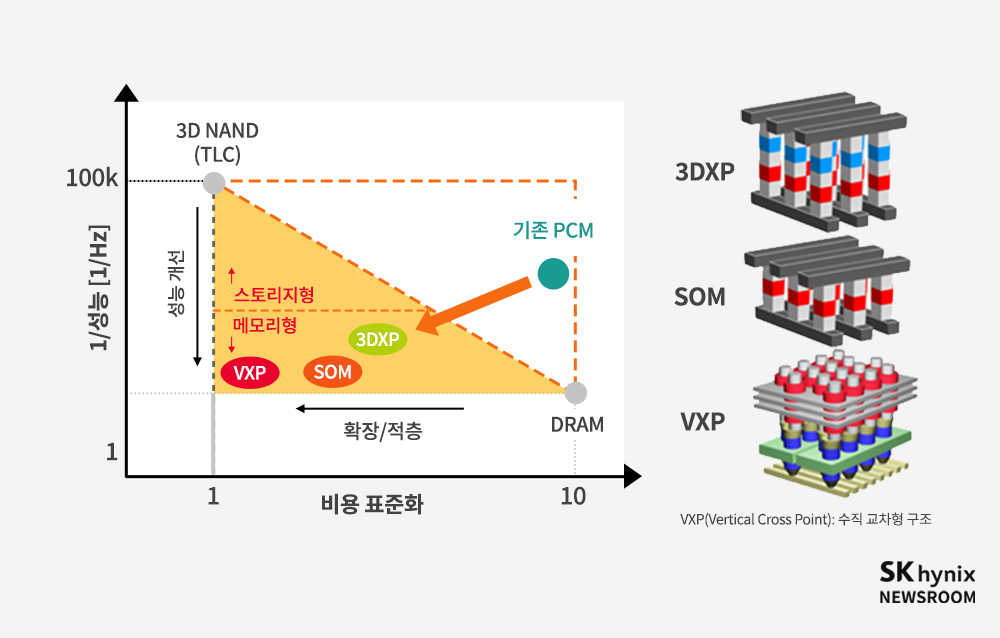

▲ 그림 4. 성능(대역폭)과 비용 간의 메모리 요구

SK하이닉스는 이러한 한계를 극복하기 위해 차세대 SCM의 대체 솔루션으로 SOM을 준비[관련기사]하고 있다. SOM은 메모리와 셀렉터(Selector, 선택 소자) 역할을 모두 수행할 수 있는 두 개의 전극과 듀얼 기능 재료(Dual Function Material, DFM)로 구성된다. 특히, SOM은 3DXP의 단점으로 지적됐던 설정 작업 시 결정화 시간이 지연되는 문제와 재설정 동작 시 높은 전류가 발생하는 문제가 개선돼, 쓰기 지연 시간과 셀 전력 소모를 줄여준다. 따라서 SOM은 1znm 기술보다 더 미세화된 공정에서도 적용 가능한 차세대 애플리케이션의 선도적인 솔루션이 될 것으로 기대된다.