CXL*(Compute eXpress Link)은 CPU, GPU, AI 가속기, 메모리 등을 보다 효율적으로 사용하기 위해 만들어진 새로운 표준화 인터페이스(Interface)다. 이는 2019년 표준 규격으로 처음 제안된 이후, CPU와 주변장치 간 안정된 인터페이스 환경을 유지하면서 고성능, 저전력으로 시스템 운영 비용을 절감할 수 있다는 장점 덕분에 주목받아 왔다.

메모리 반도체는 이 CXL 인터페이스 환경에서 성능과 용량을 최적화하기 위한 필수적인 요소다. 이에 SK하이닉스는 CXL 인터페이스 환경에 적합한 대역폭, 용량 확장 메모리 솔루션을 개발하고 있다.

이 글에서는 AI 시대를 이끌어 갈 CXL 메모리로 떠오른 제품, SK하이닉스의 SOM(Selector-Only Memory), 일명 SSM(Self Selecting Memory)을 소개한다. 특히, 2022년 국제전자소자학회(IEDM, International Electron Device Meeting)에서 처음 공개된 20나노미터(nm) SSM에 대한 연구 결과를 살펴보고자 한다.

* CXL(Compute eXpress Link) : 고성능 컴퓨팅 시스템을 효율적으로 구축하기 위한 PCIe 기반 차세대 인터커넥트 프로토콜

SK하이닉스의 SSM : 3DXP의 한계 극복

PCM(Phase-Change Memory)* 제품인 3DXPoint(이하 3DXP)는 고용량, 짧은 읽기/쓰기 시간을 자랑하며, 셀(Cell) 주소를 바이트(byte) 단위로 찾아가는 것(Byte-addressability)이 가능하다. 때문에 전원을 꺼도 정보가 지워지지 않는 낸드플래시(NAND Flash)의 장점과 처리 속도가 빠른 D램(DRAM)의 장점을 가지면서 용량 확장도 가능한 차세대 CXL 메모리로 큰 주목을 받았다.

그러나 3DXP는 크기와 두께를 더 작게 개발할 때 몇 가지 한계를 가진다. 예컨대, 3DXP는 4F2(4에프스퀘어)*의 작은 D램 셀의 크기(F)에 2z*nm 공정 기술을 적용하여 더 큰 용량의 제품으로 개발하는 것이 가능하지만, 셀 간 좁은 공간으로 인접 셀 간 열 간섭(Thermal Disturbance)*에 취약하여 1znm 미만으로 노드를 확장하는 데 제한적이다.

공정 집적도 측면에서 보면 셀 스택(Stack)은 두꺼운 PCM과 OTS(Ovonic Threshold Switch)* 및 다중 전극으로 구성되어 있어 종횡비(AR)*가 매우 높다.

또한 PCM과 OTS는 칼코제나이드*로 구성되어 있는데, 이 물질들은 공극(Void, 원소사이 빈 공간)이나 결함을 포함하고 있어 기울어짐이나 구부러지는 현상이 쉽게 발생할 수 있다. 이에 크기가 작아지고 종횡비가 커질수록 공정 난이도가 높아진다.

* PCM(Phase-Change Memory) : 특정 물질의 상(Phase) 변화를 이용해 데이터를 저장하는 방식의 메모리 반도체. 전원을 꺼도 정보가 지워지지 않는 플래시 메모리(Flash Memory) 장점과 처리 속도가 빠른 D램 장점을 모두 갖고 있음

* 4F2(4에프스퀘어) : F스퀘어(F-Square)는 셀의 단위 면적 비율로, 4F스퀘어는 1비트를 저장하게 되는 캐퍼시터의 면적 대비 유닛 셀(캐퍼시터를 제어하는 트랜지스터 포함)의 면적이 4배인 것을 의미

* 4F2(4에프스퀘어) : F스퀘어(F-Square)는 셀의 단위 면적 비율로, 4F스퀘어는 1비트를 저장하게 되는 캐퍼시터의 면적 대비 유닛 셀(캐퍼시터를 제어하는 트랜지스터 포함)의 면적이 4배인 것을 의미

* 2z : 3세대 20nm 공정기술에서 2x(20나노 후반)-2y(20nm 중반)- 2z(20nm 초반) 순으로 크기가 작아진다. 20z 나노급은 20nm 초반 크기를 뜻함

* 인접 셀 간 열 간섭(Thermal Disturbance) : 셀을 프로그래밍할 때 발생하는 열이 인접한 다른 셀의 온도를 변경하여 상태를 변경하는 행위

* OTS(Ovonic Threshold Switch) : 2단자 대칭 전압 감지 스위칭 소자. 높은 저항 상태에서 전도 상태로 전환된 후, 전류가 유지, 전류값 아래로 떨어지면 다시 높은 저항 상태로 복귀함

* 종횡비(Aspect Ratio, AR) : 가로와 세로의 비. 종횡비가 크다는 것은 형상이 좁지만 높다는 의미

* 칼코제나이드(Chalcogenide) : 최소한 하나의 16족(칼코젠) 원소와 하나 이상의 양전성 원소로 구성된 화합물

3DXP의 한계가 분명한 상황에서, SK하이닉스는 IEDM 2022를 통해 20nm SSM의 우수한 32Mb 어레이(Array) 동작 성능을 최초로 공개했다. 일반적으로 메모리는 Array를 이루고 있을 때, 0과 1을 저장하는 메모리와 이 메모리를 선택하는 셀렉터(Selector)*로 구성된다.

D램에서는 캐퍼시터가 메모리 역할을 하고, 트랜지스터가 셀렉터 역할을 한다. 3DXP에서는 PCM으로 메모리 역할을 OTS로 셀렉터 역할을 한다. SSM은 이런 메모리와 셀렉터 역할을 단일 소자에 구현하여 소자 구조의 혁신을 가져왔다.

SSM은 DFM(Dual Function Material, 듀얼 기능 재료)과 두 개의 전극으로 구성된 단일 셀 구조로 이루어져 있다. 칼코제나이드 기반 물질인 DFM은 PCM에서 셀렉터 역할을 하는 OTS처럼 문턱 전압(Vt)*을 갖는다. 이 물질(재료)은 문턱 전압이 변하지 않는 OTS와는 다르며, 양방향 쓰기 동작 시 문턱 전압이 변한다. 이 같은 변화는 메모리에 활용할 수 있는데, 따라서 DFM은 양방향 쓰기 작동을 통해 메모리와 셀렉터(Selector) 역할을 모두 수행할 수 있다. 덕분에 SSM은 간단한 셀 구조를 가질 수 있고, 이에 따라 기존 PCM의 스케일링 한계도 극복할 수 있다.

* 셀렉터(Selector) : 워드(Word) 라인과 비트(Bit) 라인 사이에 전압에 따라 반응하는 장치로, 양 끝에 걸리는 전압의 차이에 따라 메모리 셀에 데이터를 기록하거나 삭제할 수 있음

* 문턱 전압(Threshold voltage = Vth = Vt) : 방과 방 사이를 구분하는 문턱(Threshold)처럼, 문턱 전압은 전류의 흐름이 변하는 전압의 임계점을 의미. 즉, 게이트(gate) 단자에 가해지는 전압이 문턱 전압을 넘어야 Transistor가 켜진다.

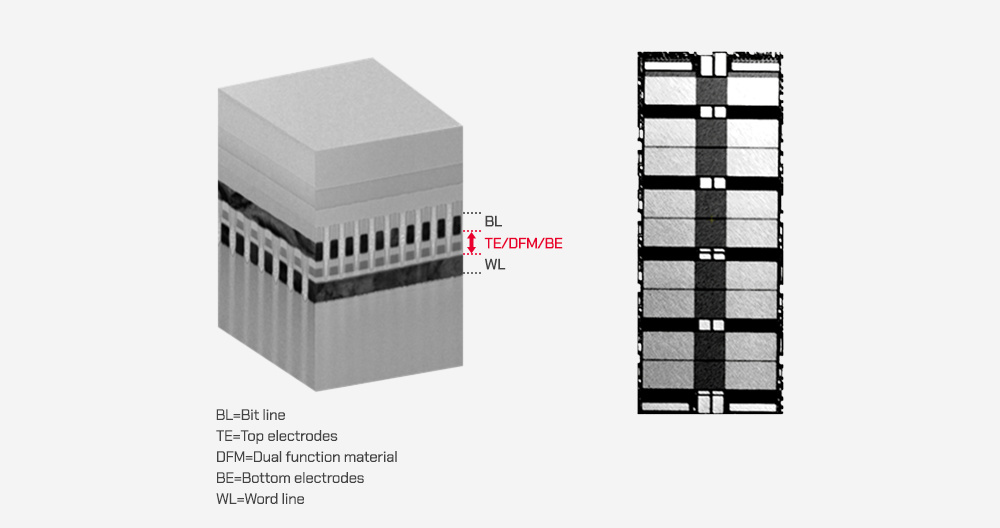

▲ 그림 1 : 투과형 전자현미경(Transmission Electron Microscopy, TEM)으로 본 SSM 셀 스택의 단면(왼쪽)과 주사 전자현미경(Scanning Electron Microscopy, SEM)으로 본 8개의 매트(Mat)로 이루어진 32Mb 어레이 구성(오른쪽)

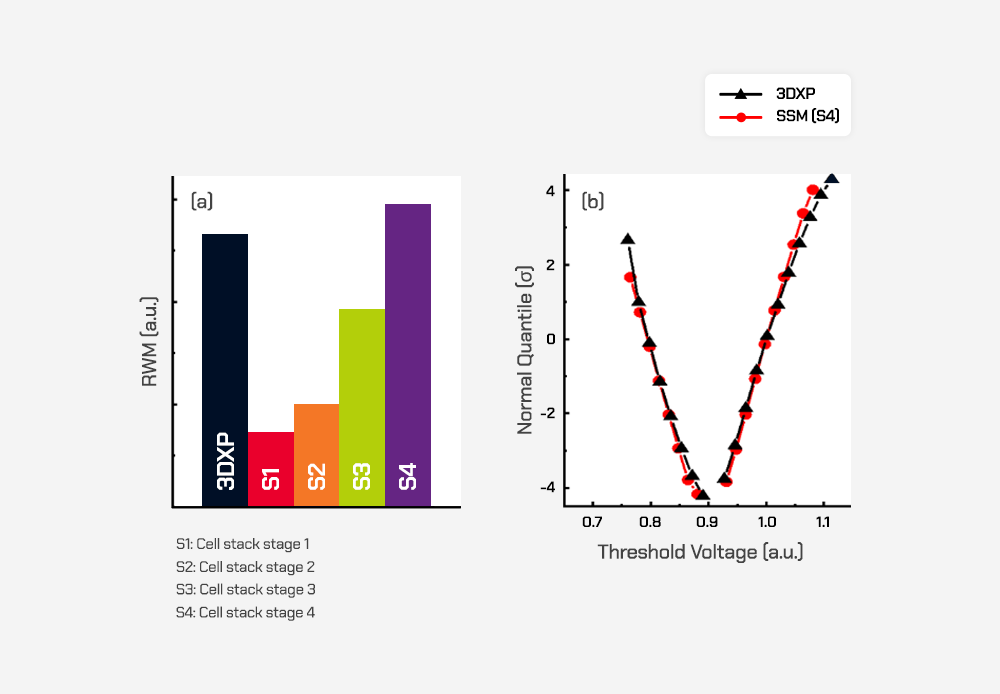

한편, DFM은 문턱 전압의 변화를 메모리로 사용하기에 0, 1과 같이 데이터를 구분하기 위해서는 문턱 전압 간 간격이 있어야 한다. 칼코제나이드 기반 소자는 문턱 전압의 산포가 크다고 널리 알려져 있으므로 0, 1의 문턱 전압 간격이 중요하다. SSM에서는 이를 RWM(Read Window Margin. RWM)*으로 정의했다.

[그림 2]는 SSM의 재료 개발(Cell Stack Material)을 통해 RWM을 기존 3DXP 수준만큼 확보 가능함을 보여준다. 또한, 표에 따르면 SSM은 쓰기 펄스*가 20ns(나노초) 미만에서도 충분한 RWM을 얻을 수 있으며, 기존 3DXP보다 훨씬 낮은 쓰기 전류에서 동작이 가능하다.

이는 SSM이 쓰기 시간과 전력 소비가 매우 낮다는 것을 의미한다. 또, SSM의 낮은 쓰기 전류와 짧은 쓰기 펄스는 3DXP보다 훨씬 적은 작동 스트레스를 받는 것을 말하며, 이에 따라 SSM은 최대 1,000만 회(1E7) 사이클의 우수한 쓰기 주기 내구성을 제공할 수 있다.

* RWM(Read Window Margin, RWM) : 0, 1과 같이 데이터를 구분하기 위한 문턱 전압 사이의 간격(ΔVt). 문턱 전압의 간격이 줄어들거나 겹치게 되면 저장된 Data를 읽을 때 에러 확률이 높아짐

* 쓰기 펄스(Write Pulse) : 소자에 정보를 기록하는 데 쓰이는 작동 펄스

▲ 그림 2 : (a) SSM은 단계적인 재료 혁신을 통해 3DXP보다 더 큰 RWM을 확보했음. (b) SSM의 Cell stack stage4 (S4)의 재료에서, 3DXP와 동일한 수준의 산포를 보여주고 있다.

SSM의 동작 원리

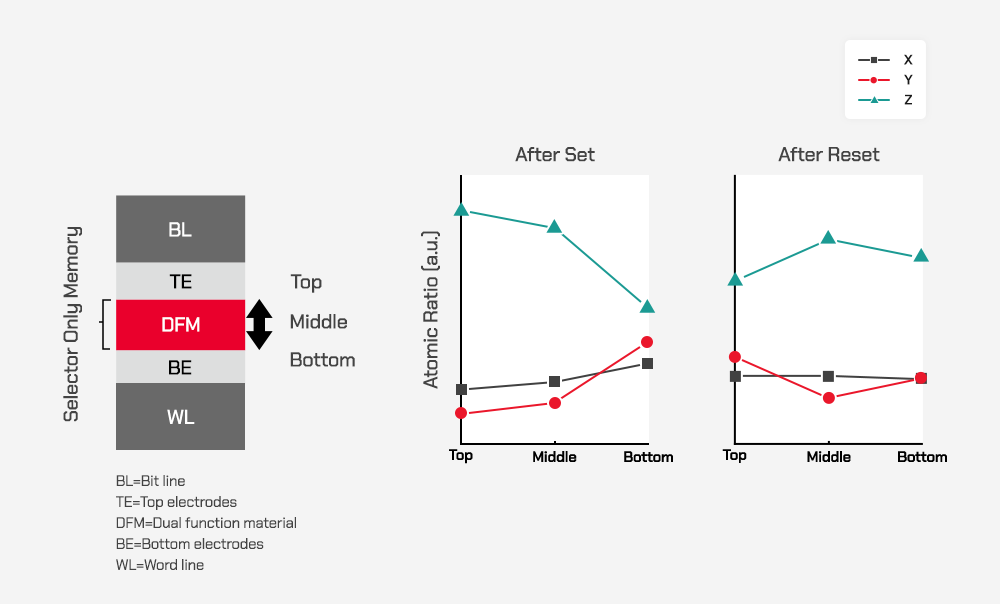

결정화와 비정질 간의 상변화가 보이는 것을 메모리로 사용하는 PCM과 달리, SSM의 기본 작동 메커니즘은 원자 마이그레이션 모델(Atomic Migration Model)과 관련 있다. 0, 1과 같이 데이터 쓰기 이후, SSM 셀 구조의 원자 성분 분포를 에너지 분산 분광법(EDS)*으로 분석해 보면, [그림 3]처럼 원자 성분 분포의 명확한 차이가 감지된다.

이 경우, 원자의 전기 음성도*가 더 높은 z 원소에서 스택 내 큰 이동을 보여준다. 그러나 기존의 전달 이론(Conventional Transport Theory)과 결합된 원자 마이그레이션 모델에서는 평균적인 밴드갭*이나 결함 밀도(Defect Density)가 바뀌지 않기 때문에 문턱 전압의 차이를 설명할 수 없었다. 따라서 이러한 현상을 이론적으로 설명하기 위해서는 추가 연구가 필요하다.

* 에너지 분산 분광법(Energy Dispersive Spectroscopy, EDS) : 시료에 전자빔으로 충격을 주고 방출된 X선을 검출하여 시료의 원소 조성을 확인하는 화학 미세 분석 기술

* 전기 음성도(Electronegativity) : 화학 결합을 형성할 때, 원자가 공 유전자를 끌어당기는 능력

* 밴드갭(Bandgap) : 여러 개의 원자가 모여 있을 때 전자가 활성화하고 이동하기까지 필요한 에너지 차이의 정도

▲ 그림 3 : EDS로 분석된 SSM 내 듀얼 기능 소재(DFM) 셀의 원자 성분 분포로 0, 1과 같이 Set과 Reset 쓰기 후에 DFM Cell 내에 수직 방향으로 x, y, z 원소의 성분 비율을 보여준다. (원소명 x, y, z는 암호코드)

SSM은 전류를 통해 열을 발생시켜 비정질에서 결정질로 바뀌는 상변화 물질을 포함하고 있지 않다. 때문에 인접 셀 간 열 간섭(Thermal Disturbace)이 발생하지 않으며, 이는 시스템의 전력 소비와 성능을 개선하는 데 도움을 준다. 또한 SSM을 2z에서 1ynm 급으로 감소해도 특성 변화가 작아, 3DXP보다 더 나은 확장성을 기대할 수 있다.

▲ 그림 4 : 3DXP와 SSM의 스펙 비교(출처: IEDM2018과 IEDM2022)

향후 SSM의 과제

SK하이닉스는 3DXP의 후속 제품으로서 20nm SSM를 입증했다. 특히 고용량 메모리 애플리케이션으로서 성공적으로 작동하는 것을 보여줬다.

SSM은 기존 PCM과는 다른 동작 원리를 가진다. 쓰기 시간, 셀 전력 소비 및 신뢰성 측면에서 3DXP보다 우수하다. 낮은 종횡비 덕분에 1z nm 미만의 노드 확장도 가능하여 용량 확장형 CXL 메모리의 가능성도 갖췄다.

SSM은 우수한 잠재력을 보여주었지만, CXL 메모리 솔루션으로 적용되기 위해서는 양방향 작동과 내구성 향상 등 몇 가지 기술적 과제를 추가로 해결해야 한다. 그 이후에는 3D 낸드와 유사한 구조를 가진 초고집적도 메모리 솔루션 VSOM(Vertical SOM)[관련기사]으로 확장될 것으로 보인다.