뉴스룸은 앞으로 총 11화에 걸쳐 <반도체 부가가치를 올리는 패키지와 테스트>라는 책을 근간으로 반도체 후공정 과정에 대해 살펴보고자 한다. 이번 연재가 업계에 입문하려는 학생들에게는 길잡이가 되는 지침서의 역할을, 유관 업무에 종사하는 분들에게는 이해도를 높이는 안내서의 역할을 할 수 있기를 바란다.(필자 주)

지난번 웨이퍼 레벨 패키지의 기본 공정 소개에 이어 이번에는 웨이퍼 레벨 패키지의 종류별 공정 순서에 대해 이야기할 차례다. ▲팬인(Fan in) WLCSP(Wafer Level Chip Scale Package), ▲팬아웃(Fan out) WLCSP ▲RDL(ReDistribution Layer) 패키지, ▲플립 칩(Flip Chip) 패키지, ▲TSV 패키지의 공정 순서를 설명한 뒤, 포토/스퍼터링/전해도금/습식공정 외에 각 패키지에서 추가로 사용되는 웨이퍼 레벨 공정을 이어서 설명하려 한다.

#1. 팬인(Fan in) WLCSP(Wafer Level Chip Scale Package) 공정

팬인 WLCSP는 웨이퍼 테스트가 끝난 웨이퍼가 패키지 라인에 입고되면, 먼저 스퍼터링(Sputtering) 공정으로 금속 박막층을 만든다. 그리고 그 위에 포토 레지스트(Photo Resist)를 두껍게 도포하는데(Thick PR Coating), 패키지용 금속 배선 형성을 위해서는 그 배선 두께보다 포토 레지스트가 두꺼워야 하기 때문이다. 포토 레지스트는 포토 공정으로 패턴을 만들고, 패턴이 되어 열린 부분에 전해도금으로 구리(Cu)를 도금하여 금속 배선을 형성한다(Cu Electro-plating). 배선이 형성되면 포토 레지스트를 벗겨주고(TPR Strip), 필요 없는 부분의 금속 박막층을 화학적 에칭으로 제거한다(Thin Film Etch). 그리고 이 위에 절연층(Dielectric Layer)을 형성한다. 절연층은 다시 솔더 볼이 올라갈 부분만 포토 공정으로 제거하는데, 이때 절연층은 SR(Solder Resist)이라고도 부른다. 절연층은 WLCSP의 최종 보호막(Passivation Layer)이자 솔더 볼이 붙는 영역을 제한하는 역할을 한다. 만약 이 절연층이 없으면 솔더 볼을 붙이고, 리플로우할 때 솔더 볼이 금속층 위로 계속 녹아내려 볼 형태를 유지할 수 없을 것이다.

절연층이 포토 공정으로 패턴화되면 그 위에 솔더 볼을 붙이는 솔더 볼 마운팅 공정을 진행한다. 솔더 볼 마운팅이 끝나면 패키지 공정이 완료되므로, 웨이퍼 절단을 통해서 팬인 WLCSP 단품으로 만든다.

◎ 솔더 볼 마운팅(Solder Ball Mounting) 공정

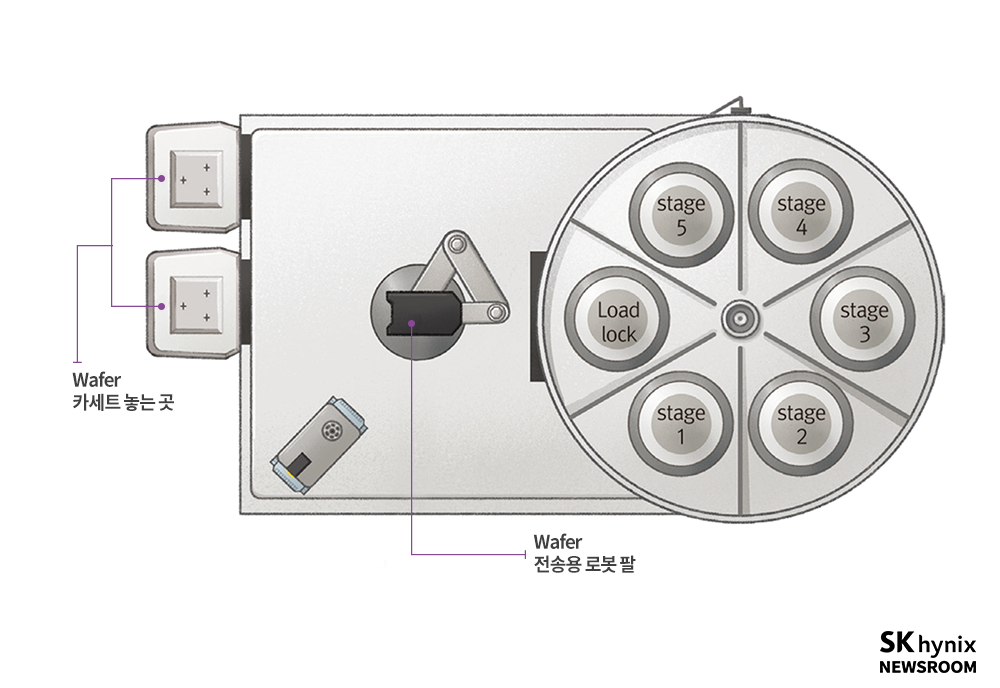

▲ 그림 1 : 웨이퍼 레벨 리플로우 장비(ⓒ한올출판사, photograph.PSK)

솔더 볼 마운팅 공정은 WLCSP 위에 패키지용 솔더 볼을 붙이는 공정이다. 이는 컨벤셔널 패키지에서 서브스트레이트 위에 솔더 볼을 붙이는 공정과도 유사한데, 웨이퍼 위에 솔더 볼을 올린다는 차이점이 있다. 이 때문에 플럭스 도포, 솔더 볼 마운팅, 리플로우 과정은 똑같지만, 플럭스 도포와 솔더 볼 마운팅 시 사용하는 스텐실이 웨이퍼와 같은 크기다. 또한, 리플로우 장비도 컨베이어로 이송하는 대류(Convection) 리플로우 방식이 아닌 <그림 1>과 같은 핫 플레이트(Hot Plate) 기반의 웨이퍼 리플로우 장비를 사용한다. 웨이퍼 레벨의 리플로우 장비는 스테이지별로 이동하는 웨이퍼에 각각 다른 온도를 인가한다. 이를 통해 웨이퍼는 리플로우를 위한 온도 프로파일을 가지며 공정이 진행된다.

#2. 플립 칩 범프(Flip Chip Bump) 공정

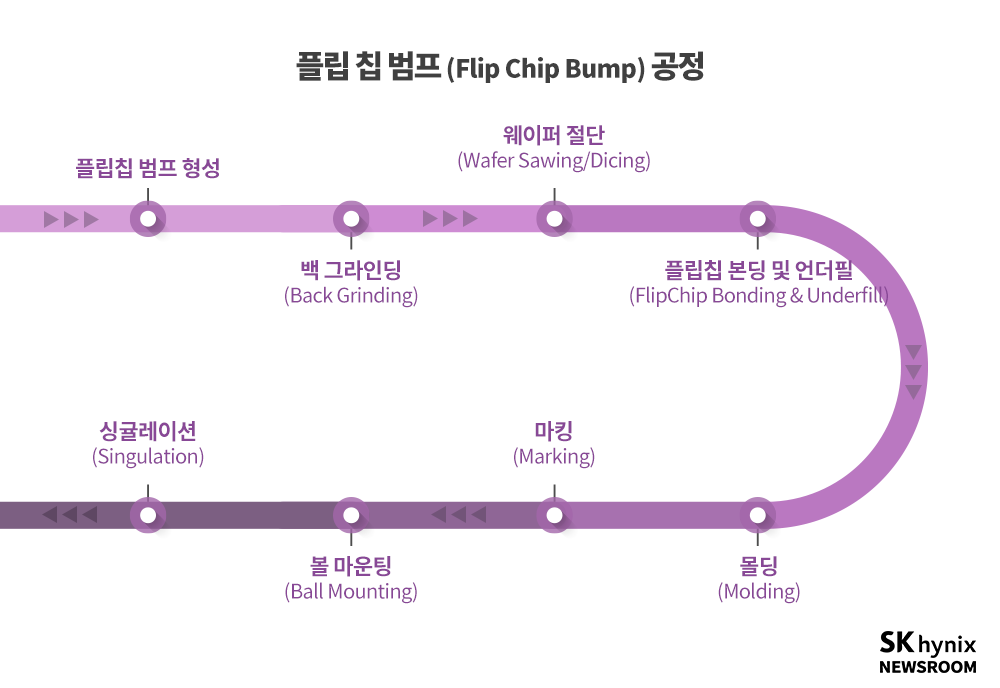

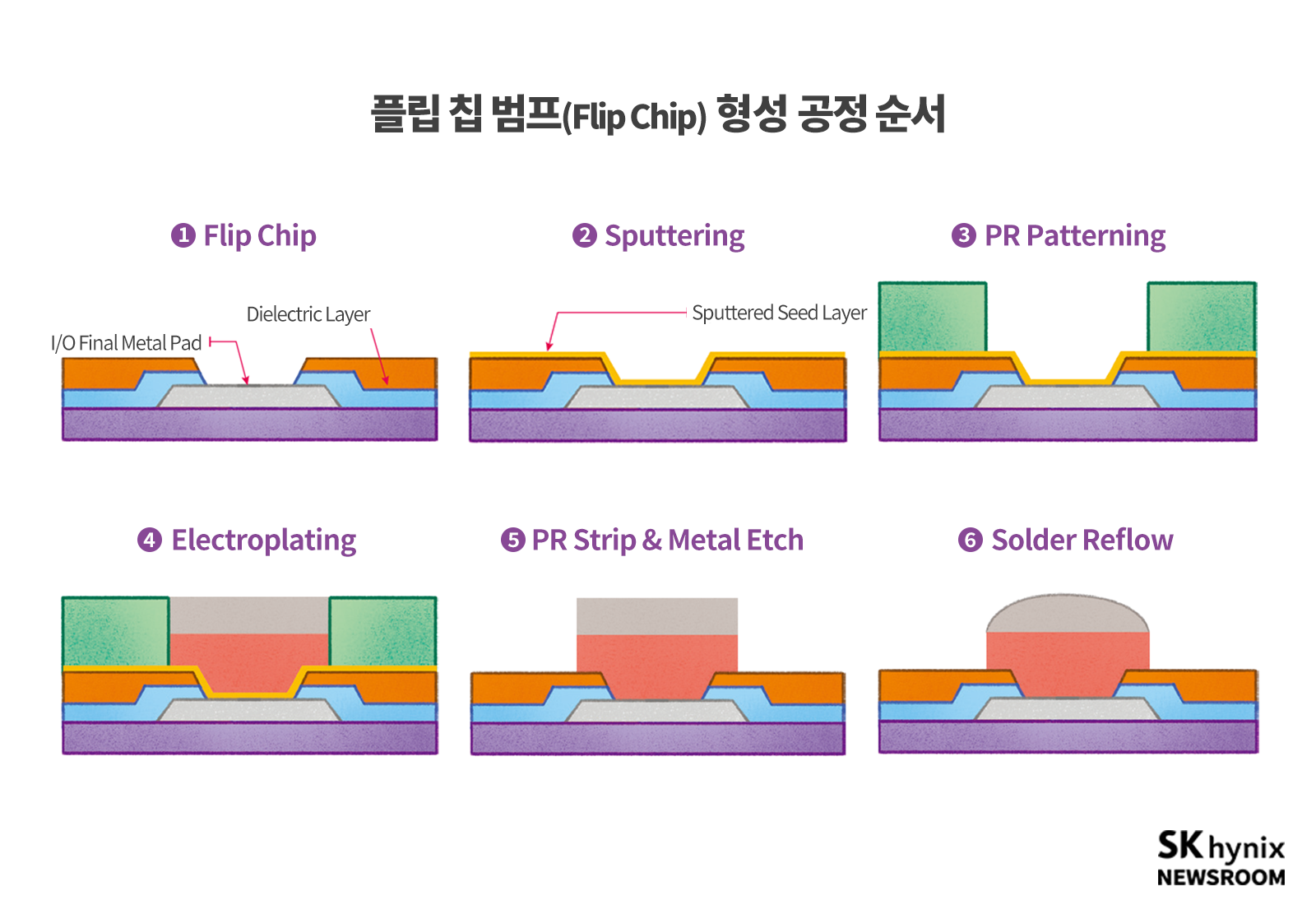

플립 칩 패키지에서 범프를 형성하는 공정은 웨이퍼 레벨 공정으로 진행하지만, 후속 공정은 다음과 같이 컨벤셔널 패키지 공정으로 진행한다.

▲ 그림 2 : 플립 칩 범프(Flip Chip Bump) 형성 공정 순서

그리고 포토 레지스트를 도포하여 패턴화하는데, 형성할 범프의 높이 때문에 웨이퍼 레벨 패키지에서 가장 두껍게 도포할 수 있는 쪽에 속하는 포토 레지스트를 사용한다. 그리고 전해도금으로 솔더 범프를 만드는데, CPB(Copper Post Bump/Copper Pillar Bump)*의 경우에는 Cu를 도금한 뒤 다시 솔더를 도금한다. 솔더는 보통 무연 솔더인 Sn-Ag 합금을 사용한다. 도금을 완료하면 PR을 벗겨주고, 스퍼터링으로 형성한 UBM(Under Bump Metallurgy)* 박막을 금속 에칭으로 제거한다. 이후에 웨이퍼 레벨 리플로우 장비를 사용해 범프를 구형으로 만든다. 이처럼 솔더 범프 리플로우 작업이 필요한 이유는 범프 간 높이 차이를 최소화하고, 솔더 범프의 거칠기를 줄이며, 솔더의 산화물을 제거하여 플립 칩 본딩 공정 시의 접합성을 높이기 위해서다.

* UBM(Under Bump Metallurgy) : 플립칩 범프 아래쪽에 형성된 금속 층을 통칭

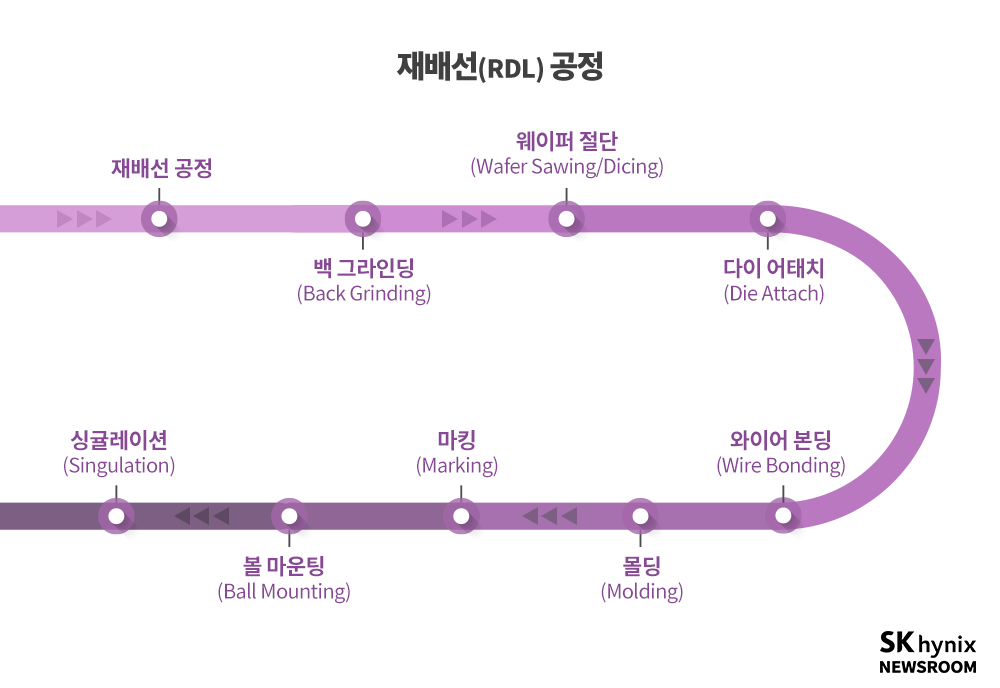

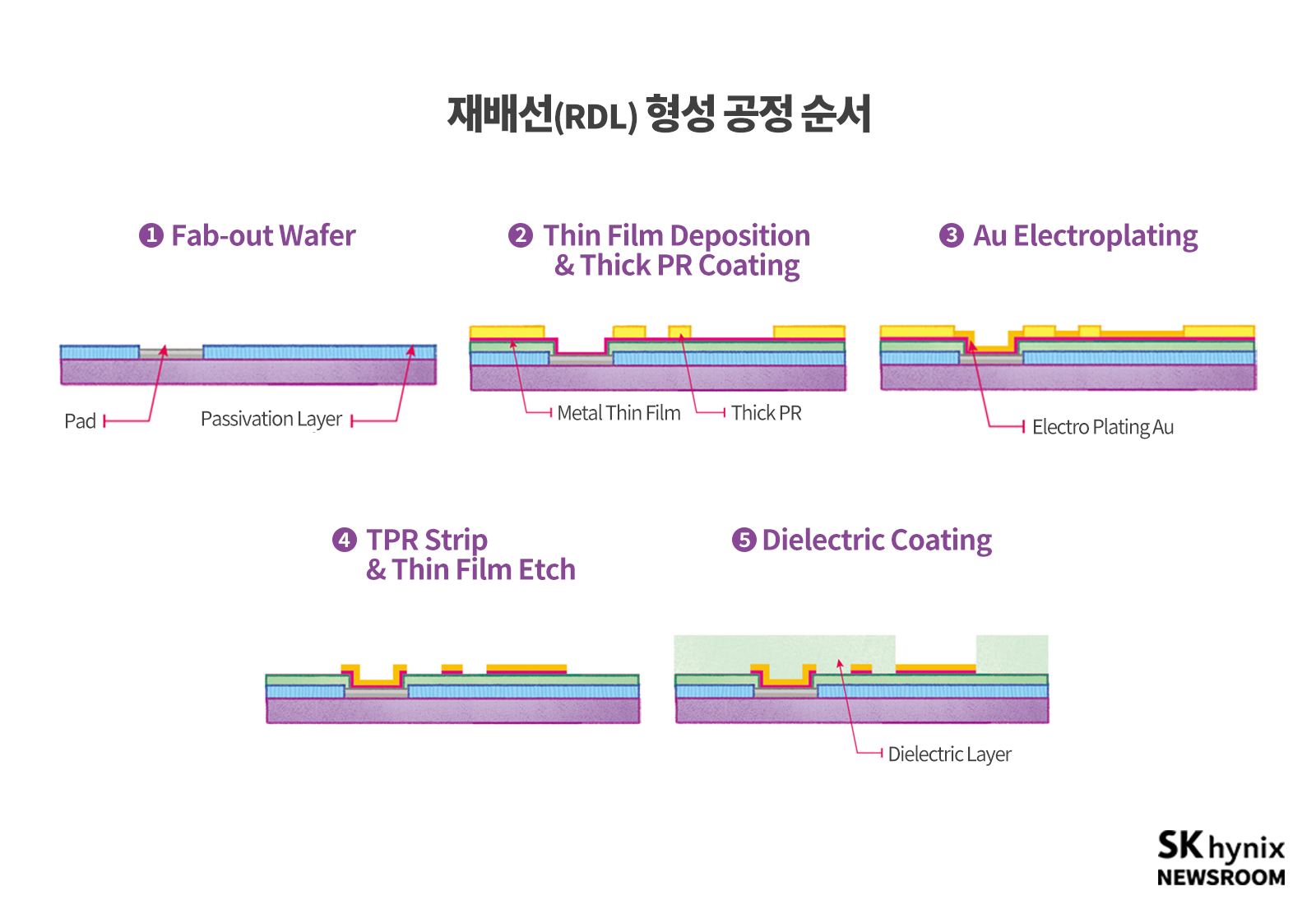

#3. 재배선(RDL, Redistribution Layer) 공정

▲ 그림 3 : 재배선(RDL, Redistribution Layer) 형성 공정 순서

재배선(RDL, Redistribution Layer) 공정은 칩 적층 등을 목적으로 사용되는데, 웨이퍼에 형성된 패드에 재배선용 금속층을 다시 만들어 새로운 패드를 형성하는 공정이다. 그래서 재배선 후의 패키지 공정은 그림 3과 같이 컨벤셔널 패키지 공정을 따른다. 이때, 칩을 적층할 경우에는 ‘다이 어태치→ 와이어 본딩’을 적층해야 하는 칩의 수만큼 반복한다.

RDL 공정은 웨이퍼 테스트가 끝난 웨이퍼가 패키지 라인에 입고되면 시작이다. 먼저, 스퍼터링공정으로 금속 박막층을 만든다. 그리고 그 위에 두꺼운 포토 레지스트를 도포한다. 그리고 포토 공정으로 패턴을 만들고, 패턴으로 열린 부분에 전해도금으로 금(Au)을 도금하여 금속 배선을 형성한다. 재배선 자체가 패드를 다시 만드는 공정이므로 와이어 본딩 시 접합성이 우수해야 한다. 때문에 와이어 본딩 재료인 Au와 같은 재료를 도금하는 것이다.

#4. 팬아웃(Fan out) WLCSP(Wafer Level Chip Scale Package) 공정

팬아웃 WLCSP를 만드는 공정은 먼저 웨이퍼 모양의 캐리어에 테이프를 붙이고, 그 위에 웨이퍼다이싱 공정이 완료된 칩 중에서 테스트에서 양품으로 판정 받은 칩들을 일정한 간격으로 붙이면서 시작된다. 그 다음에 웨이퍼 몰딩으로 칩과 칩 사이의 공간을 메워 새로운 웨이퍼 형태를 만든다. 웨이퍼 몰딩이 끝나면 캐리어와 테이프를 떼어낸다. 그리고 몰딩으로 형성된 새로운 웨이퍼에 웨이퍼 장비들을 이용해서 금속 배선을 만들고, 패키지용 솔더 볼을 붙인다. 마지막으로 패키지 단품으로 잘라주면 전체 공정이 완료된다.

◎ 웨이퍼 몰딩(Wafer Molding)

팬아웃 WLCSP를 만들기 위해서는 반드시 웨이퍼 몰딩을 해야 한다. 웨이퍼 몰딩 공정은 몰딩을 위한 성형틀에 웨이퍼(팬아웃 WLCSP의 경우엔 칩들이 붙여진 웨이퍼 형태의 캐리어)를 놓고 액상이나 가루(Powder) 또는 그래뉼(Granule) 타입의 에폭시 밀봉재(EMC)*를 몰드할 곳에 넣은 다음 압착(Compression)하고 열을 주어서 몰딩을 하는 공정이다. 웨이퍼 몰딩은 팬아웃 WLCSP뿐만 아니라 뒤에 설명할 TSV를 이용한 KGSD(Known Good Stacked Die)를 위한 필수 공정이기도 하다.

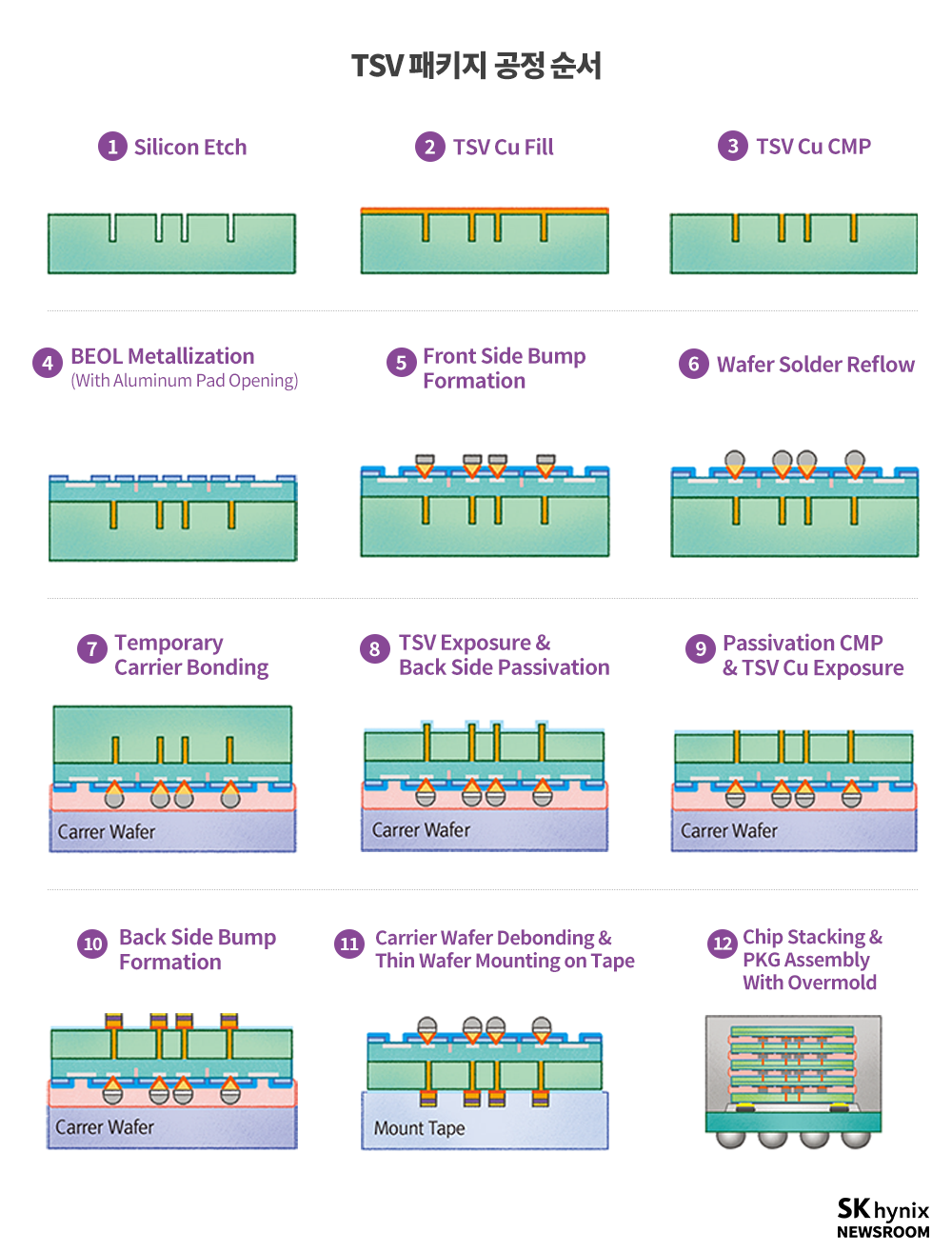

#5. 실리콘 관통 전극 TSV 패키지 공정

비아 미들(Via Middle)*로 만들어지는 TSV 패키지의 전체 공정 순서는 <그림 4>와 같다. 먼저, 웨이퍼 공정에서 비아를 형성하고 패키지 쪽에 와서 웨이퍼 앞면에 솔더 범프를 만든 후 캐리어 웨이퍼를 붙여서 백 그라인딩하고 웨이퍼 뒷면에 범프를 형성한 후 칩 단위로 잘라서 적층하는 순으로 공정을 진행한다.

웨이퍼 공정에서 TSV 비아를 비아 미들 타입으로 형성하는 공정을 개략적으로 보면, 먼저 웨이퍼에 CMOS 등의 트랜지스터를 형성한다(FEOL, Front End of Line). 그리고 TSV를 형성할 위치에 HM(Hard Mask)*을 이용하여 패턴을 만든다. 그다음은 실리콘(Si)를 에칭하는데, HM이 없는 부분을 드라이 에칭 공정으로 없애고 깊은 트렌치(Trench)를 만든다. 여기에 산화물(Oxide) 등의 절연막을 CVD(Chemical Vaporized Deposition, 화학 증착) 공정으로 형성한다. 이 절연막은 트렌치를 채울 Cu 같은 금속이 Si와 절연되게 함으로써, Cu로 인해 Si 오염을 방지한다. 절연막 위에는 금속 박막층(Seed/Barrier)을 만든다. 이 금속 박막층을 이용하여 Cu 등의 금속을 전해도금한다. 전해도금이 완료되면 CMP(Chemical-Mechanical Polishing) 공정으로 평탄화하며 동시에 웨이퍼 윗면에 있는 Cu를 모두 제거해 트렌치에만 Cu가 채워질 수 있게 한다. 이후에 후속 배선 공정(BEOL, Back End of Line)을 진행하여 웨이퍼 공정을 완료한다.

▲ 그림 4 : TSV 패키지 공정 순서(ⓒ한올출판사)

TSV를 이용한 칩 적층 패키지를 만들 때 크게 두 종류의 패키지를 만들 수 있다. 첫 번째는 3D 칩 적층으로 서브스트레이트를 이용한 패키지를 만드는 것이고, 두 번째는 KGSD(Known Good Stack Die)* 형태를 만들고 그것을 다시 2.5D 패키지나 3D 패키지로 만드는 것이다. 여기에서는 KGSD를 만드는 공정과 KGSD를 이용해 2.5D 패키지를 만드는 공정을 설명하겠다.

KGSD는 TSV로 칩 적층된 패키지로 이것을 이용해서 2.5D나 3D 패키지, 팬아웃 WLCSP 등의 추가적인 패키지 공정을 진행한다. KGSD의 대표적인 제품이 HBM(High Bandwidth Memory)이다. KGSD는 추가적인 패키지 공정을 진행해야 하므로 KGSD에 형성된 연결 핀(Pin)이 일반적인 솔더 볼이 아니라 미세 솔더 범프라는 특징이 있다. 이 때문에 칩들이 적층되어지는 곳이 3DS 패키지의 경우엔 서브스트레이트이지만, KGSD의 경우엔 웨이퍼이며 이 웨이퍼가 KGSD에서 가장 아랫부분의 칩(Bottom Chip)이 된다. HBM의 경우엔 이 것을 베이스 칩 또는 베이스 웨이퍼라고 부르고, 그 위에 적층되는 칩을 코어 칩이라고 부른다.

공정 순서를 설명하면, 베이스 웨이퍼와 코어 웨이퍼 모두 웨이퍼 앞면에 플립 칩 범프 형성 공정으로 범프를 만든다. 베이스 웨이퍼는 2.5D 패키지에서 인터포저에 붙일 수 있는 범프 배열을 가져야 한다. 반면에 코어 웨이퍼는 웨이퍼 앞면에 칩 적층을 위한 배열로 범프를 형성한다. 웨이퍼 앞면에 범프를 형성한 뒤에는 웨이퍼를 얇게 만들고 뒷면에도 범프를 만들어야 한다. 그런데 웨이퍼를 얇게 만들면 컨벤셔널 패키지 공정의 백 그라인딩 공정에서 설명한 것처럼 웨이퍼에 휨(Warpage)이 발생한다. 컨벤셔널 패키지의 경우엔 백 그라인딩 후에 웨이퍼를 원형틀(Ring Frame)에 테이프로 붙여야 휘어지지 않고 후속 공정을 진행할 수 있지만, 웨이퍼 뒷면에 범프를 만들어야 하는 TSV 패키지 공정에서는 불가능한 방법이다. 그래서 개발된 공정이 WSS(Wafer Support System) 공정이다. 캐리어 웨이퍼에 범프가 형성된 웨이퍼 앞면을 가접착용 접착제(Temporary Adhesive)로 붙이고, 뒷면을 그라인딩하여 웨이퍼를 얇게 만든다(Wafer Thinning). 캐리어 웨이퍼에 붙어있기 때문에, 얇아진 웨이퍼는 휘어지지 않는다.

또한, 캐리어 웨이퍼도 웨이퍼 형태이므로 그 상태로 웨이퍼 장비에서 공정이 가능하다. 이 구조를 이용하여 얇아진 웨이퍼 뒷면에 범프를 만든다. 코어 웨이퍼는 웨이퍼 앞뒤에 범프가 형성되었으면 캐리어를 떼어내고(Carrier Debonding) 컨벤셔널 패키지 공정처럼 원형틀에 테이프로 붙여주고, 웨이퍼 절단(Sawing/Dicing)을 한다. 베이스 웨이퍼는 계속 캐리어 웨이퍼에 붙인 상태로 코어 웨이퍼에서 절단한 칩을 떼어내고, 베이스 웨이퍼 위에 칩 적층을 한다. 적층이 완료되면 베이스 웨이퍼에 웨이퍼 몰딩을 하고, 캐리어 웨이퍼를 떼어낸다. 이렇게 되면 베이스 웨이퍼는 코어 칩들이 적층되어서 몰딩된 웨이퍼가 된다. 이 웨이퍼를 2.5D 패키지를 만들 수 있는 타깃 두께로 그라인딩해 주고, 칩 단위로 절단하면 KGSD가 완성된다. 이렇게 KGSD로 완성된 HBM을 포장(Packing)하여 2.5D 패키지를 만들 고객에 보내준다.

HBM과 로직 칩으로 SiP를 만드는 2.5D 패키지는 패키지 공정 순서에 따라 CoWoS(Chip on Wafer on Substrate)과 CoCoS(Chip on Chip on Substrate)로 구분할 수 있다.

CoWoS는 대만에 있는 파운드리 회사인 TSMC에서 개발하고 특허권을 갖고 있는 공정으로 인터포저(Interposer) 웨이퍼 위에 로직 칩과 HBM을 각각 붙이고, 웨이퍼 몰딩을 한 후 이 몰딩된 웨이퍼를 캐리어 웨이퍼와 본딩한다. 그리고 인터포저의 뒷면을 그라인딩하여 얇게 만들고, 서브스트레이트에 붙일 수 있는 솔더 범프를 형성한다. 캐리어 웨이퍼를 떼내고, 몰딩된 인터포저 웨이퍼를 단품 단위로 잘라서 서브스트레이트에 붙이고, 후속 패키지 공정을 진행한다. 마지막으로 열특성을 강화할 방열판(Heat Spreader)*을 부착하면 2.5D 패키지가 완성된다. CoCoS는 대부분의 OSAT(Out Sourced Assembly & Test) 회사에서 진행하고 있는 2.5D 패키지 공정이다. 앞면과 뒷면 모두에 범프가 형성된 인터포저를 칩 단위로 잘라서 서브스트레이트에 붙이고, 그 위에 HBM과 로직 칩을 각각 붙인다. 그리고 CoWoS처럼 후속 패키지 공정 및 방열판 부착을 완료한다.

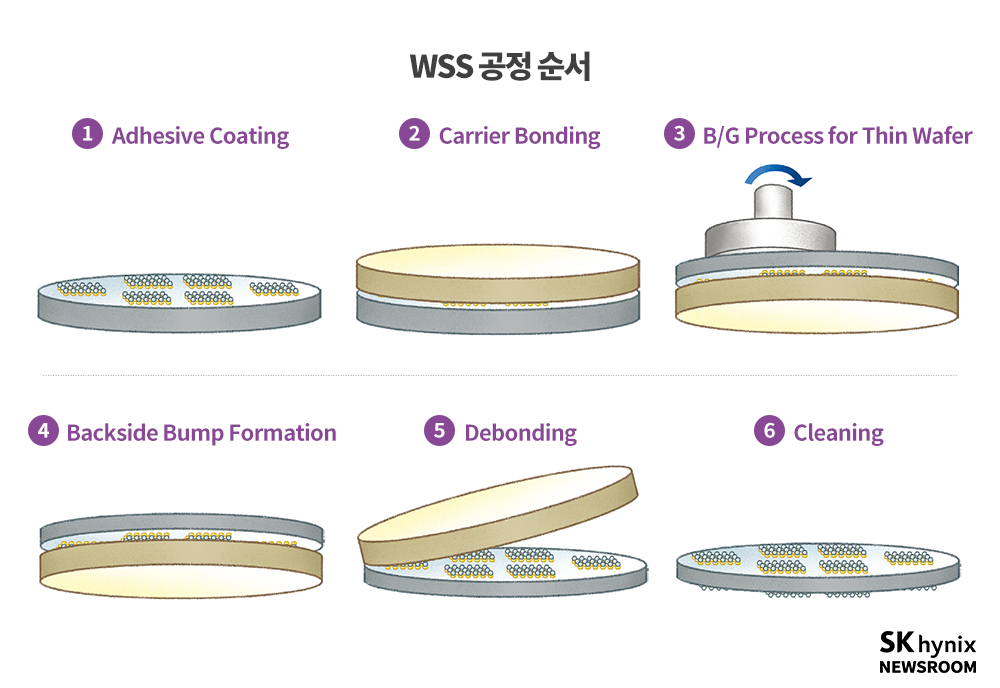

◎ WSS(Wafer Supporting System) 공정

WSS는 백 그라인딩 전에 캐리어 웨이퍼를 붙인 후 백 그라인딩 공정을 진행하여 얇아진 웨이퍼를 백 그라인딩 된 면에 추가 공정이 가능할 수 있게 핸들링하는 시스템을 의미한다. TSV 패키지를 위한 웨이퍼에 캐리어를 붙이는 캐리어 본딩(Carrier Bonding) 공정과 웨이퍼 뒷면에 범프 형성 등의 공정을 완료한 후에 다시 캐리어를 떼어내는 캐리어 디본딩(Carrier Debonding) 공정이 WSS를 위한 공정이다. <그림 5>는 WSS를 위한 공정 순서를 나타낸 것으로 캐리어 본딩은 가접착용 접착제를 웨이퍼에 도포한 뒤 캐리어에 붙이는 공정이다. 캐리어 디본딩은 뒷면의 공정이 완료된 후 캐리어를 떼어내고, 웨이퍼에 접착제 성분이 남아 있지 않도록 세정하는 공정으로 이루어진다.

▲ 그림 5 : WSS 공정 순서(ⓒ한올출판사)

캐리어 본딩 공정에서 고려할 점은 캐리어 본딩으로 붙은 웨이퍼들의 전체 두께가 균일해야 하고, 접합부에 보이드(Void)가 없어야 하며, 두 웨이퍼 간의 정렬이 잘 되어 있어야 하고, 웨이퍼 가장자리에 접착제로 인한 오염이 없어야 하며, 웨이퍼의 휨이 적게 공정이 진행되어야 한다는 것이다. 그리고 디본딩 공정에서 고려할 점은 캐리어를 떼어낸 웨이퍼에 칩핑(Chipping)*같은 깨짐·균열이 없어야 하고, 접착제 잔여물(Residue)도 남지 않아야 하며 웨이퍼의 범프 변형(Deformation)이 생기지 않도록 공정이 진행되어야 한다는 것이다.

WSS에서 상대적으로 난이도가 높고 중요한 공정은 디본딩이다. 그래서 다양한 디본딩 방법이 제안되고 개발되었으며, 각 방법에 맞는 가접착용 접착제도 개발되었다. 대표적으로 열(Thermal) 방식, 레이저(Laser) 조사 후 필름을 벗겨내는(Peel off) 방식, 화학적 용해(Chemical Dissolution) 방식, 기계적으로 들어 올린 후(Mechanical Lift Off) 화학적 세정(Chemical Cleaning)하는 방식 등이 있다.

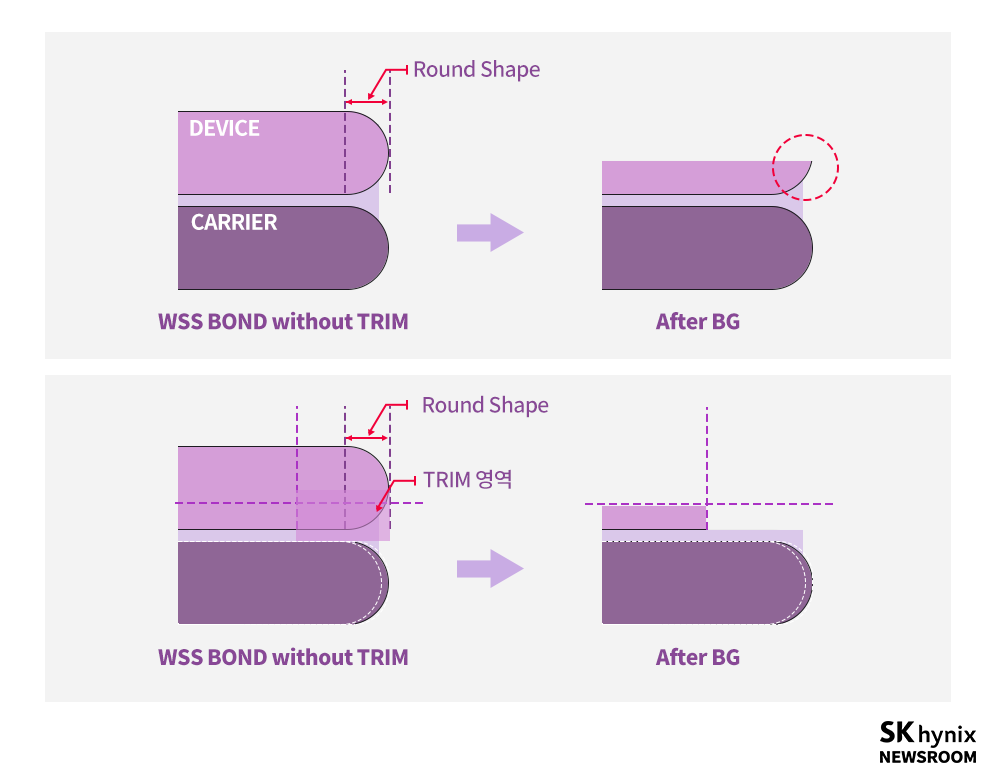

◎ 웨이퍼 에지 트리밍(Wafer Edge Trimming) 공정

▲ 그림 6 : 웨이퍼 에지 트리밍 (ⓒ한올출판사)

캐리어 웨이퍼와 본딩 후에 백 그라인딩 공정을 진행하면 TSV 패키지를 만들 웨이퍼는 오른쪽 빨간 원으로 표시한 것처럼 가장자리가 날카로워진다. 이 상태에서는 웨이퍼 뒷면에 범프를 형성하기 위한 포토 공정, 금속박막 형성 공정, 전해도금 공정 등 수많은 공정을 진행하며 웨이퍼 가장자리가 깨질 위험이 커진다. 웨이퍼 가장자리가 깨지면 그 균열이 내부까지 전파될 수 있고, 결국 추가 공정이 불가능한 상황까지 생긴다. 따라서 수율에서 엄청난 손실이 생기는 것이다. 이러한 문제를 해결하기 위해서 캐리어 웨이퍼와 본딩하기 전에 미리 TSV 패키지를 만들 웨이퍼의 앞면 가장자리를 트리밍해서 제거한다. 이렇게 가장자리 쪽이 제거된 웨이퍼로 캐리어 웨이퍼와 본딩한 후 백 그라인딩을 진행하면 <그림 6>의 아래 그림처럼 웨이퍼 가장자리의 날카로운 영역이 사라지고, 후속으로 여러 공정을 진행해도 가장자리가 깨질 위험도 사라진다. 일반적으로 트리밍 공정은 웨이퍼 절단용 블레이드가 회전하며 웨이퍼 가장자리를 따라 지나가면서 가장자리의 일정 부분을 제거하는 방식으로 진행된다.

◎ 적층(Stacking) 공정

TSV를 이용한 패키지에서는 웨이퍼 앞면과 뒷면에 각각 형성된 범프들을 본딩하여 적층한다. 본딩 방법은 플립 칩 본딩처럼 MR(Mass Reflow)*이나 열압착(Thermo-Compression)*방식 등을 이용한다. 그리고 적층 시 사용되는 형태에 따라 칩 투 칩(Chip to Chip), 칩 투 웨이퍼(Chip to Wafer), 웨이퍼 투 웨이퍼(Wafer to Wafer)로 적층 공정을 나눈다.

* 열압착(Thermo-Compression) : 붙이고자 하는 대상에 열과 압력을 주어서 접착하는 공정 방법이다.

TSV가 형성된 칩들을 적층할 때 범프는 미세 범프다. 따라서 범프 간 간격이 작고, 적층되는 칩과 칩 사이 간격도 작아서 본딩의 신뢰성이 높은 열압착 방식이 많이 사용되었다. 하지만 열압착 방식은 본딩할 때마다 일정 시간 동안 열과 압력을 주어야 해서 전체 공정 시간이 길고, 생산성이 낮다는 단점이 있다. 그래서 최근에는 MR로 본딩 방식을 바꾸는 추세이다.

적층 시 형태상의 분류로 보면 생산성은 칩 투 칩 방식이 가장 낮고, 웨이퍼 투 웨이퍼 방식이 가장 높다. 하지만 현재 칩 투 칩 방식이 가장 많이 사용되고, KGSD 같은 패키지 타입에서 칩 투 웨이퍼 방식이 적용되고 있다. 웨이퍼 투 웨이퍼 방식은 생산성은 높지만, 이 방식을 적용하기 위해선 우선 적층하는 웨이퍼들의 칩 크기와 배열이 같아야 한다. 이종 제품 적층 시 이 방식을 적용하려면 칩 크기가 가장 큰 제품에 맞춰야 하므로 일부 제품은 필요 없이 칩 크기가 커질 수 있다. 칩 크기가 같다고 하더라도 적층 후에 같은 위치의 칩은 모든 웨이퍼에서 양품이어야 적층 후의 제품도 양품이 된다. 만약 한 웨이퍼에서라도 칩이 불량이면 다른 웨이퍼 내 동일 위치의 칩이 모두 양품이어도 적층된 제품은 불량이 되기 때문이다. 이러한 어려움 때문에 현재는 웨이퍼 투 웨이퍼 적층은 CIS(CMOS Image Sensor) 등의 일부 2층 적층을 위한 제품에서만 한정적으로 사용하고 있다.