반도체 공정은 웨이퍼를 제조하고 회로를 새기는 전공정, 칩을 패키징하는 후공정으로 나뉜다. 이중 후공정은 반도체 미세화 기술이 한계점에 다다른 현시점에서 중요성이 점점 더 커지고 있다. 특히, 새로운 부가가치를 만들 수 있는 핵심 기술로 주목받고 있다.뉴스룸은 앞으로 총 11화에 걸쳐 <반도체 부가가치를 올리는 패키지와 테스트>라는 책을 근간으로 반도체 후공정 과정에 대해 살펴보고자 한다. 이번 연재가 업계에 입문하려는 학생들에게는 길잡이가 되는 지침서의 역할을, 유관 업무에 종사하는 분들에게는 이해도를 높이는 안내서의 역할을 할 수 있기를 바란다.(필자 주)

자연적, 화학적, 열적 환경으로부터 칩소자를 보호하기 위해서는 ‘반도체 패키지’ 환경 테스트에서 높은 신뢰성이 요구된다. 이는 ‘반도체 패키지’ 재료와 밀접히 관련 있는 부분이다. 또한, 하이스피드(High Speed)에 따라 패키지 내 서브스트레이트(Substrate)의 저유전율*, 저유전손실율* 등 패키지 재료의 전기적 특성의 요구가 높아지는 추세다. 그래서, 전력 반도체나 CPU, GPU 같은 로직 반도체에서뿐만 아니라, 최근에는 메모리 반도체에서도 열 방출 기능과 관련해서 열전도가 좋은 재료에 대한 요구가 이어지고 있다. 이와 같이 ‘반도체 패키지’ 재료는 반도체 산업 동향에 발맞추고 제품의 기능을 개선하기 위해 반드시 이해해야 한다. 따라서 앞으로 두 번에 걸쳐 패키지별 재료의 특성에 대해 알아보려 한다. 이번 시간에는 ‘컨벤셔널 패키지’ 재료에 관해 이야기하겠다.

* 유전손실 : 교류 전기장에 유전체를 넣었을 때 내부에서 전기에너지가 열로 변하는 현상

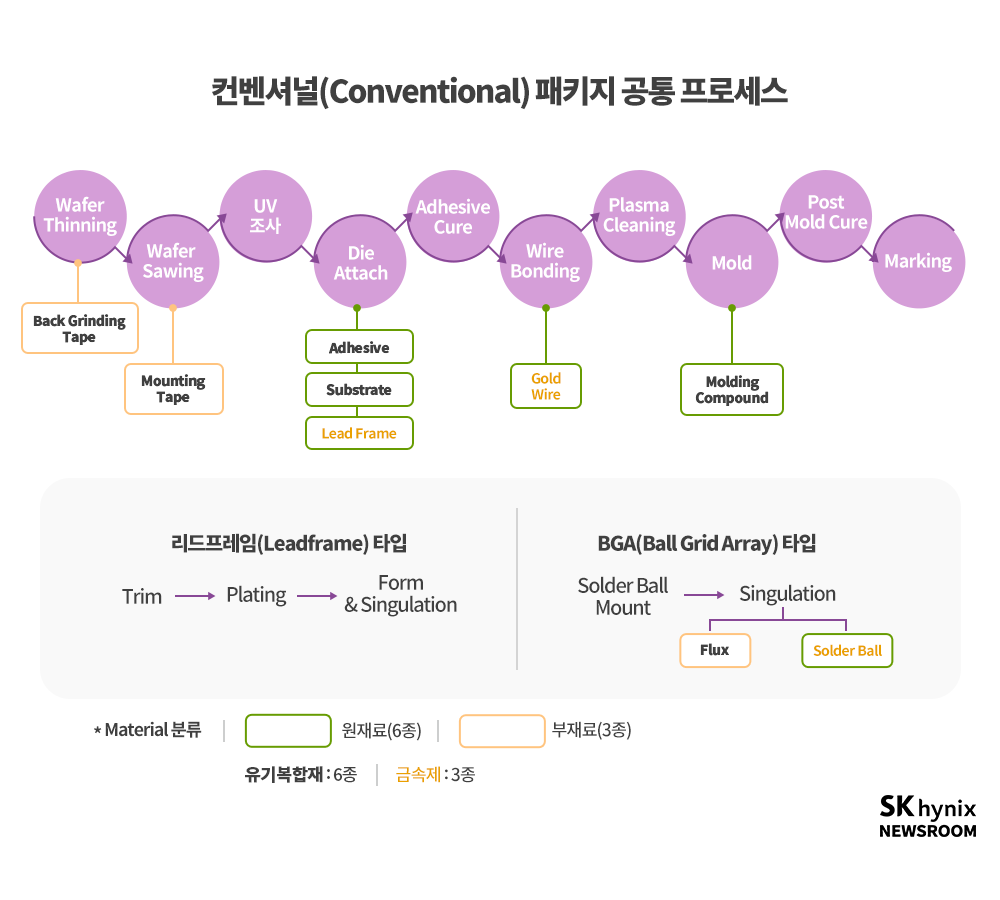

패키지 공정에서 사용되는 재료는 크게 원재료와 부재료로 구분할 수 있다. 원재료는 패키지를 구성하는 재료로서, 공정 품질 및 제품의 신뢰성에 직접적인 영향을 주는 재료다. 부재료는 패키지 공정 중에 사용된 후 제거되어, 제품 구조에는 포함되지 않는 재료이다.

패키지 공정에서 사용되는 재료는 크게 원재료와 부재료로 구분할 수 있다. 원재료는 패키지를 구성하는 재료로서, 공정 품질 및 제품의 신뢰성에 직접적인 영향을 주는 재료다. 부재료는 패키지 공정 중에 사용된 후 제거되어, 제품 구조에는 포함되지 않는 재료이다.

▲ 그림 1 : 컨벤셔널 패키지 공정별 사용 재료(ⓒ한올출판사)

<그림 1>은 일반적인 컨벤셔널 패키지에서 공정별로 사용하는 패키지 재료를 보여준다. 컨벤셔널 패키지에서 원재료로 사용되는 유기물 복합 재료는 총 6종으로 접착제(Adhesive), 서브스트레이트(Substrate), 에폭시 밀봉재(EMC, Epoxy Molding Compound)가 있고, 그 중 금속 재료는 리드프레임(Leadframe), 와이어(Wire), 솔더 볼(Solder Ball) 등이 있다. 그리고 부재료는 테이프(Tape)류 및 플럭스(Flux)가 있다.

#1. 리드프레임(Leadframe)

리드프레임은 리드프레임 타입 패키지에서 패키지 내부의 칩과 외부의 PCB 기판을 전기적으로 연결하는 역할을 하며, 반도체 칩을 지지해 주는 핵심 재료이다.

리드프레임을 만드는 금속판은 보통 열팽창계수를 Si칩과 유사하게 만든 Alloy 42*나 열전도 및 전기전도도가 우수한 구리를 사용한 합금이 사용된다. 금속판에서 리드프레임을 만드는 방법은 2가지인데, 에칭(Etching) 법과 스탬핑(Stamping) 법이 있다. 에칭법은 리드프레임의 패턴(Pattern)에 따라 포토 레지스트(Photo Resist, PR)를 금속판에 도포하고 에천트(Etchant)*에 노출해 포토 레지스트가 도포되지 않은 부분은 제거하고 리드프레임을 만든다. 주로 미세한 리드프레임 패턴이 필요할 때 에칭 방법을 사용한다. 스탬핑 법은 고속 프레스(Press)에 프로그레시브 금형(Progressive Die)*을 장착하여 리드프레임을 만드는 방법이다.

* 에천트(Etchant) : 에칭 공정에서 부식을 진행하는 화학 용액이나 가스 등의 물질을 통칭

* 프로그레시브 금형(Progressive Die) : 여러 단계의 공정을 하나의 공정으로 연속, 압축해 진행하는 금형 기술

#2. 서브스트레이트(Substrate)

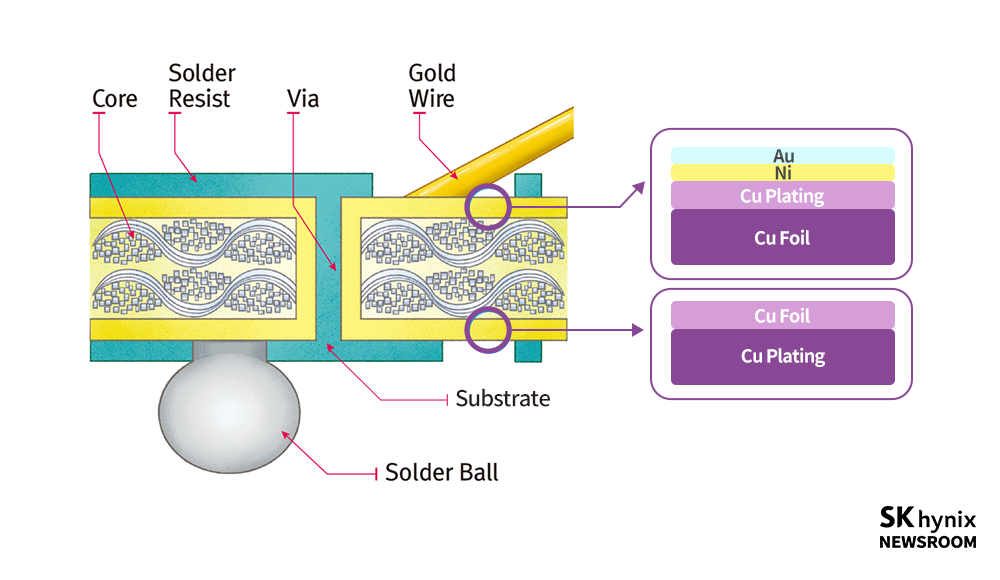

▲ 그림 2 : 서브스트레이트 패키지 공정 후 단면 구조(ⓒ한올출판사)

서브스트레이트는 리드프레임이 아닌 솔더 볼을 사용하는 BGA(Ball Grid Array) 패키지에서 패키지 내부의 칩과 외부의 PCB 기판을 전기적으로 연결하는 역할을 하며, 반도체 칩을 지지해 주는 핵심 재료다. <그림 2>는 패키지 공정 후에 서브스트레이트의 단면 구조로 아랫면에 솔더 볼이 붙어 있고, 윗면에 와이어가 연결되어 있다. 서브스트레이트의 가운데는 코어(Core)라는 재료로 형성되어 있는데, 코어는 열 안정성이 우수한 BT(Bismaleimide Triazine)* 레진(Resin)이 함침(含浸)*된 유리 섬유(Glass Fabric) 양면에 얇은 구리막인 동박(銅箔, Cu Foil)을 붙인 것이다. 동박에 금속 배선을 만들고, 그 위에 솔더 레지스트를 형성해 금속 패드를 노출하여 보호막 역할을 한다.

* 함침(含浸) : 형태를 만드는 주물공정에서 발생된 틈새를 메우는 것으로 도금공정에서 도장의 불량을 줄이기 위해 필요함

◎ 서브스트레이트(Substrate) 제조 공정

서브스트레이트는 패널(Panel) 형태로 제작되며, CCL(Copper Clad Lamination)부터 시작하여 패드 부분을 표면처리하고 최종 검사하는 공정으로 끝난다. 순서는 다음과 같다.

CCL은 BT 레진이 함침된 프리프레그(Prepreg)* 양면에 동박을 붙여 완전 경화한 것이다. CCL에 드릴링으로 구멍을 뚫는데, 절연체로 구성되는 층간의 전기적 연결을 위한 통로를 만드는 것이다. 그 후 서브스트레이트의 절연층 사이에서 전기적 연결의 매체로 사용되는 구리를 사용하여, 드릴링으로 형성한 구멍의 벽면을 도금하거나 구멍 전체를 채워 전기적 연결을 마무리한다. 그리고 동박과 도금으로 형성된 구리(Cu)층이 전기 배선 역할을 할 수 있도록, 에칭(Etching)을 통해 배선을 만든다. 배선 공정이 완료되면 검사 장비로 배선에 발생할 수 있는 불량을 자동 검사하는 AOI(Auto Optical Inspection)*를 진행한다.

* AOI(Auto Optical Inspection) : 자동 광학 검사

서브스트레이트는 금속층인 Cu층을 2층 레이어(Layer)로 적용하면 별도의 적층 공정이 필요 없다. 하지만 3층, 4층 등으로 늘리기 위해서는 적층 공정이 필요하다. 적층을 위해서는 먼저 코어에 형성된 동박(Cu Foil) 표면을 일부러 산화해 표면 거칠기(Surface Roughness)를 강화한다. 이는 적층 시 동박에 붙을 절연막인 프리프레그(Prepreg)와의 접착력을 높이기 위해서다. 프리프레그는 유리섬유에 BT 수지를 함침하여 반경화(半硬化)한 것이다. 프리프레그와 동박을 고온·진공 상태의 코어에서 가열, 가압하여 붙인 뒤 경화(硬化)하면, 절연층과 금속층이 쌓인다. 적층으로 추가된 금속층을 기존의 금속층과 전기적으로 연결하고, 금속 배선을 만들기 위해 ‘드릴링→ Cu 도금→ 금속 배선 형성’ 공정을 반복한다. 솔더 레지스트는 Cu 회로를 보호하고, 전기적 연결을 고려한 선택적 절연막을 형성하는 공정으로 외부의 열과 충격으로부터 서브스트레이트 전체를 보호하는 역할을 한다. 또한, 솔더 볼이 붙는 영역을 제한해, 서브스트레이트에 솔더 볼을 붙이는 리플로우 공정에서 금속과 젖음성(Wettability)*이 좋은 솔더가 금속층 전체로 녹아내리지 않게 한다. 덕분에 패키지에서 솔더 볼의 높이는 균일하게 유지될 수 있다.

솔더 레지스트(SR, Solder Resist)는 액상 타입은 도포하고, 드라이 필름(Dry Film) 타입은 필름 라미네이션 공정으로 붙인다. 패턴을 만들 때는 ‘SR 도포(Printing)→ SR 노광(Exposure) → 현상 → 에칭 → 박리(Stripping)’ 순으로 공정을 진행한다. 솔더 레지스트의 패턴 공정으로 노출된 동박은 와이어를 연결하거나 솔더 볼을 붙일 부분이다. 하지만 표면이 산화되거나 손상되면 패키지 공정에서 불량이 발생하므로 동박 표면의 산화를 방지하거나 패키지에서 칩과 서브스트레이트의 연결을 용이하게 하는 금속 표면 처리(Metal Surface Finish) 공정을 진행해야 한다. 표면 처리까지 완료하면, 패널로 제작된 서브스트레이트를 스트립(Strip) 단위로 자르는 공정을 한 후 최종적으로 검사를 진행한다. 검사에 통과된 제품은 포장하여 패키지 공정을 진행하는 곳에 납품한다.

#3. 접착제(Adhesive)

접착제는 페이스트(Paste) 타입의 액상이나 필름(Film) 타입의 고상 형태다. 주로 열경화성 에폭시 계열 고분자로 이루어졌으며, 리드프레임 또는 서브스트레이트의 면에 칩을 접착하거나, 칩 적층 시 칩과 칩을 접착하는 역할을 한다. 접착제가 패키지의 환경시험에서 높은 신뢰성을 확보하기 위해서는, 높은 접착력과 낮은 흡습률, 적정한 기계적 물성(Tg, CTE, Modulus) 및 낮은 이온 불순물이 필요하다. 또한 공정 품질 확보를 위해서는 고온·고압의 접착 공정 시 재료의 흐름성 및 접착계면의 젖음성이 높아야 하고, 보이드(Void)* 발생을 억제하여 높은 계면접착력을 발휘해야 한다. 이를 위해서는 유변물성인 점도, 요변성(Thixotropy)* 및 경화 특성의 최적화가 요구된다. 그리고 칩과 리드프레임 또는 서브스트레이트 표면에서의 접착력도 높아야 한다.

* 요변성(Thixotropy) : 액체 물질을 휘저어 주는 등의 전단력이 작용할 때는 점성도가 감소하고, 전단력의 작용이 없을 때에는 점성도가 증가하는 현상

액상 접착제는 ▲에폭시(Epoxy) 접착제와 ▲실리콘(Silicone) 접착제가 있으며, 고상 접착제는 ▲리드프레임에 사용되었던 LOC(Lead On Chip) 테이프가 있고, ▲같은 크기의 칩을 적층할 때 칩 간의 간격을 띄우기 위해서 사용하는 스페이서(Spacer) 테이프, ▲그리고 서브스트레이트에 칩을 붙일 때나 칩을 적층할 때 사용하는 DAF(Die Attach Film)가 있다. DAF는 웨이퍼 뒷면에 부착되기 때문에 WBL(Wafer Backside Laminate) 필름이라고 부르기도 한다.

#4. 에폭시 몰딩 컴파운드 (Epoxy Molding Compound, EMC)

EMC는 ‘반도체 패키지’ 공정에 사용되는 봉지재(Encapsulant)*로 열에 의해 3차원 연결구조를 형성하는 열경화성 에폭시 고분자 재료와 무기 실리카 재료를 혼합한 복합 재료다. EMC는 칩을 둘러싼 재료이므로 물리적·화학적 외부 환경으로부터 칩을 보호해야 하고, 칩이 동작할 때 발생하는 열을 효과적으로 방출할 수 있어야 한다. 그리고 원하는 패키지 형태가 되도록, EMC도 원하는 형상으로 쉽게 성형할 수 있어야 한다. 그리고 서브스트레이트, 칩 등의 다른 패키지 재료와 계면을 형성하고 있으므로, 그 재료와의 접착성이 좋아야 패키지 환경 신뢰성을 만족할 수 있다.

▲ 표 1 : EMC의 형태(ⓒ한올출판사, Photograph.KCC)

<표 1>은 EMC의 형태와 적용되는 공정 방식을 나타낸 것이다. 태블릿(Tablet) 형태로 만든 EMC는 트랜스퍼(Transfer) 몰딩 방식에 주로 사용되고, 가루(Powder/Granule) 형태의 EMC는 압축(Compression) 몰딩이나 몰딩할 크기가 큰 웨이퍼 몰딩에 주로 사용된다. 성형이 어려운 웨이퍼 몰딩에는 액체 형태의 EMC가 사용되기도 한다. 최근에는 팬아웃 WLCSP나 대면적의 PLP(Panel Level Package)의 경우는 EMC를 필름 형태로 만들어 진공 라미네이션하는 방법을 사용하기도 한다. 그 외, 플립 칩 공정 시에 언더필(Underfill)과 몰딩을 한번에 진행하는 MUF(Molded Underfill)[관련기사 보기]용 EMC도 있다.

#5. 솔더(Solder)

솔더는 낮은 온도에서 녹는 금속으로, 이 특성을 활용해 여러 구조체에서 전기적 연결과 기계적 연결을 함께 하는 재료로 널리 사용된다. ‘반도체 패키지’에서는 패키지와 PCB 기판을, 플립 칩에서는 칩과 서프스트레이트를 전기적·기계적으로 연결하는 역할도 한다. 패키지와 PCB 기판을 연결하는 솔더는 주로 볼(Ball)의 형태인데, 30㎛에서 760㎛까지 크기는 다양하다. 요즘은 전기적 특성을 높이기 위해 패키지와 PCB 기판의 연결 핀(Pin) 수를 늘리는 추세라, 사용하는 솔더 볼도 점점 더 작아지고 있다.

◎ 솔더 볼에 대한 요구사항

솔더 볼은 솔더 합금인 경우 합금 조성이 균일해야 한다. 균일성이 부족할 경우 온도 사이클 시험(TC, Thermal Cycle) 및 낙하(Drop) 충격에 대한 신뢰성이 취약해질 수 있다. 그리고 내산화성도 우수해야 한다. 원자재 혹은 리플로우 공정 중에 산화막이 과도하게 생성되는 경우 볼이 제대로 붙지 않는 논웨트(Non-wet)*로 미싱 볼(Missing Ball) 불량이 발생할 수 있다. 때문에 솔더 볼 공정 중 산화막 제거를 위해 플럭스(Flux)를 사용하며, 리플로우(Reflow) 시 질소(N2) 가스로 불활성 분위기 조성이 필요하다. 그리고 보이드(Void)가 없어야 한다. 보이드가 존재하면 솔더의 양이 부족하여 솔더 접합부에 대한 신뢰성이 떨어지기 때문이다. 그리고 솔더 볼의 크기도 중요하다. 크기가 균일해야 공정 효율이 높아지기 때문이다. 또한, 솔더 볼 표면은 오염이나 덴드라이트(Dendrite)* 성장물이 없어야 한다. 오염과 덴드라이트 성장물은 공정의 불량률을 높이고 솔더 접합부의 신뢰성을 떨어뜨린다.

* 덴드라이트(Dendrite) : 덴드라이트는 나무가지 같은 모양으로 발달하는 결정으로, 자연에서 발견되는 프랙탈의 한 가지

◎ 솔더 볼의 조성

예전에는 기계적 성질과 전기전도도가 좋은 주석 합금(Pb-Sn)을 많이 썼다. 하지만 납이 인체에 유해한 물질로 환경 규제(RoHS*)를 받으면서 지금은 납 함량이 700ppm 이하인 무연(Lead Free) 솔더를 주로 사용하고 있다.

#6. 테이프(Tape)

테이프는 ▲동종 또는 이종의 고체면과 면을 영구적으로 접착하는 접착용 테이프와 ▲일시적인 점착(접착의 일종)으로 응집력과 탄성을 가져 접착·박리가 가능한 절삭(Dicing) 테이프와 백 그라인딩(Back Grinding) 테이프가 있다. 이때 사용되는 재료를 PSA(Pressure Sensitive Adhesive)라고 한다.

백 그라인딩 테이프는 웨이퍼 백 그라인딩 공정을 진행할 때 웨이퍼 상에 구현된 소자를 보호하기 위해 웨이퍼의 앞면에 붙이는 테이프다. 백 그라인딩 공정이 완료되면 다시 박리해야 하며, 박리 후 점착제 성분이 웨이퍼에 남아 있지 않게 해야 한다.

절삭 테이프는 일명 마운팅(Mounting) 테이프라고도 부르며, 웨이퍼를 원형 틀(Ring-Frame)에 고정하고, 웨이퍼 절삭 공정 진행 시 칩들이 떨어지지 않도록 지지하는 역할을 한다. 웨이퍼 절삭 시에는 접착력이 좋아야 하지만, 절삭 테이프에서 칩을 떼어 서브스트레이트 등에 붙일 때는 잘 떨어져야만 한다. 그래서 절삭 테이프에는 자외선(UV)에 반응하는 PSA가 있어 칩을 떼어내기 전에 자외선을 조사하여 접착력을 약하게 만든 후에, 칩을 떼어낼 때 박리가 쉽게 한다. 기존에는 백 그라인딩 후에 절삭 테이프에 웨이퍼를 붙였지만, 접착제에서 설명한 WBL이 칩의 접착제로 널리 사용되면서 WBL 필름과 절삭 테이프가 함께 있는 테이프에 백 그라인딩된 웨이퍼를 붙인다.

#7. 와이어(Wire)

▲ 그림 3 : 금(Au) 와이어 (ⓒ한올출판사, Photograph.Heraeus)

칩과 서브스트레이트 또는 리드프레임, 칩과 칩을 전기적으로 연결하는 와이어는 주로 순도가 높은 금(Au)을 사용한다. 금이 전성(얇게 퍼지는 성질)과 연성(길게 늘어나는 성질)이 좋아 와이어 연결 공정에 유리하며 내산화성 등이 좋아서 신뢰성이 높고, 전기전도도가 우수하여 전기적 특성까지 좋기 때문이다. 하지만 금은 가격이 비싸므로 제조 비용이 커진다. 때문에 금 와이어(Gold Wire)의 굵기를 가늘게 줄인 것을 적용하기도 하지만, 과하면 와이어가 끊어지기 쉬워 한계가 있다. 그래서 은(Ag) 등의 다른 금속을 넣어서 합금을 만들기도 하고, 금 코팅한 은(Au Coated Ag), 구리(Cu), 팔라늄 코팅한 구리(Pd Coated Cu), 팔라늄합금 코팅한 구리(AuPd Coated Cu) 등을 사용하기도 한다. 가격 경쟁력 때문에 금 와이어 대신 구리 와이어를 적용한 제품이 늘어나고 있는데, 구리 와이어는 금에 비해 전성과 연성은 조금 떨어지지만, 전기전도도가 좋다. 하지만 산화가 잘 되는 특성 때문에 와이어 연결 후뿐만 아니라 공정 중에서 와이어가 산화되는 문제가 있다. 그래서 구리 와이어의 경우에는 금 와이어와 다르게 연결 장비를 밀폐하고, 장비 안은 N2 가스 등으로 채워 구리 와이어가 공기에 노출되어 산화되지 않게 관리하고 있다.

#8. 포장 재료

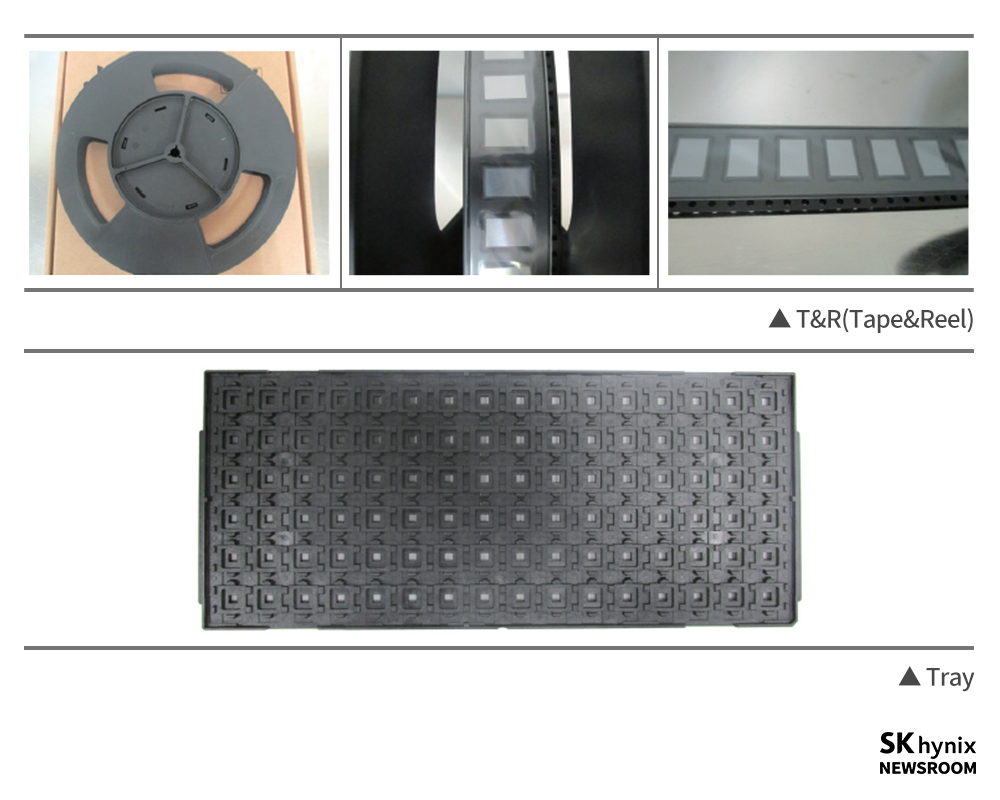

▲ 그림 4 : 위에서부터 T&R(Tape&Reel)와 Tray(ⓒ한올출판사, Photograph.SK hynix)

패키지 공정 후 패키지 테스트 공정까지 완료되면 고객에게 보낼 반도체 제품을 출하하는데, 이때 T&R(Tape & Reel)이나 트레이(Tray)를 사용한다. T&R은 패키지 크기에 맞춰 제작한 포켓이 있는 테이프에 패키지들을 넣고, 이 테이프를 릴(Reel)로 말아서 포장한 후 출하한다. 트레이는 패키지를 트레이에 넣고, 이 트레이를 적층하여 포장한 후 출하한다.