반도체 공정은 웨이퍼를 제조하고 회로를 새기는 전공정, 칩을 패키징하는 후공정으로 나뉜다. 이중 후공정은 반도체 미세화 기술이 한계점에 다다른 현시점에서 중요성이 점점 더 커지고 있다. 특히, 새로운 부가가치를 만들 수 있는 핵심 기술로 주목받고 있다.

뉴스룸은 앞으로 총 11화에 걸쳐 <반도체 부가가치를 올리는 패키지와 테스트>라는 책을 근간으로 반도체 후공정 과정에 대해 살펴보고자 한다. 이번 연재가 업계에 입문하려는 학생들에게는 길잡이가 되는 지침서의 역할을, 유관 업무에 종사하는 분들에게는 이해도를 높이는 안내서의 역할을 할 수 있기를 바란다.(필자 주)

#1. 반도체 패키지의 정의

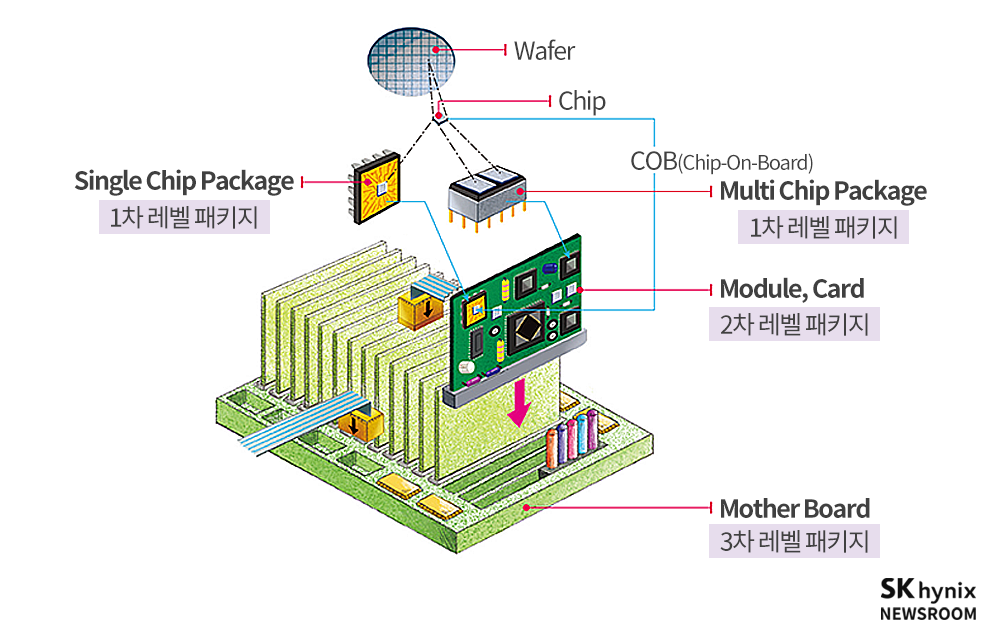

전자패키징 기술은 모든 전자제품의 하드웨어 구조물과 관련된 기술로서, 하드웨어 구조물은 반도체와 같은 능동소자*와 저항, 캐패시터(Capacitor)**와 같은 수동소자***로 구성된다. 이렇듯 전자패키징 기술은 매우 폭넓은 기술이며, 0차 레벨 패키지부터 3차 레벨 패키지까지의 체계로 구분할 수 있다. <그림 1>은 실리콘 웨이퍼에서 단일 칩을 잘라내고, 이를 단품화하여 모듈(Module)을 만들고, 모듈을 카드 또는 보드(Board)에 장착하여 시스템을 만드는 전체 과정을 모식도로 표현한 것이다. 이러한 과정 전체를 일반적으로 패키지 또는 조립(Assembly)이라고 광의적인 의미로 표현한다. 그리고, 웨이퍼에서 칩을 잘라내는 것을 0차 레벨 패키지, 칩을 단품화하는 것을 1차 레벨 패키지, 단품을 모듈 또는 카드에 실장하는 것을 2차 레벨 패키지라 표현한다. 그리고 단품과 모듈이 실장된 카드를 시스템 보드에 장착하는 것을 3차 레벨 패키지라고, 패키지의 체계를 분류한다. 하지만 반도체 업계에서 일반적으로 의미하는 반도체 패키지는 이 전체 과정 중에서 웨이퍼에서 칩을 잘라내고, 단품화하는 공정을 의미한다.

* 능동소자: 반도체에서 메모리 반도체, 로직 반도체와 같이 그 회로가 구현되어 역할을 하는 소자

** 캐패시터(Capacitor): 전자를 저장하여 결과적으로 전기용량을 갖게 하는 소자

*** 수동소자: 전자 소자 가운데, 증폭이나 전기 에너지의 변환과 같은 능동적 기능을 갖지 않은 소자

▲ 그림 1 : 반도체 조립의 과정(ⓒ한올출판사)/p>

출처 : D.P.Seraphim, R.C.Lasky, and C.-Y.Li, Ed., Principle of Electronic Packaging, New York ; McGraw-Hill Book Company, 1989, p.5

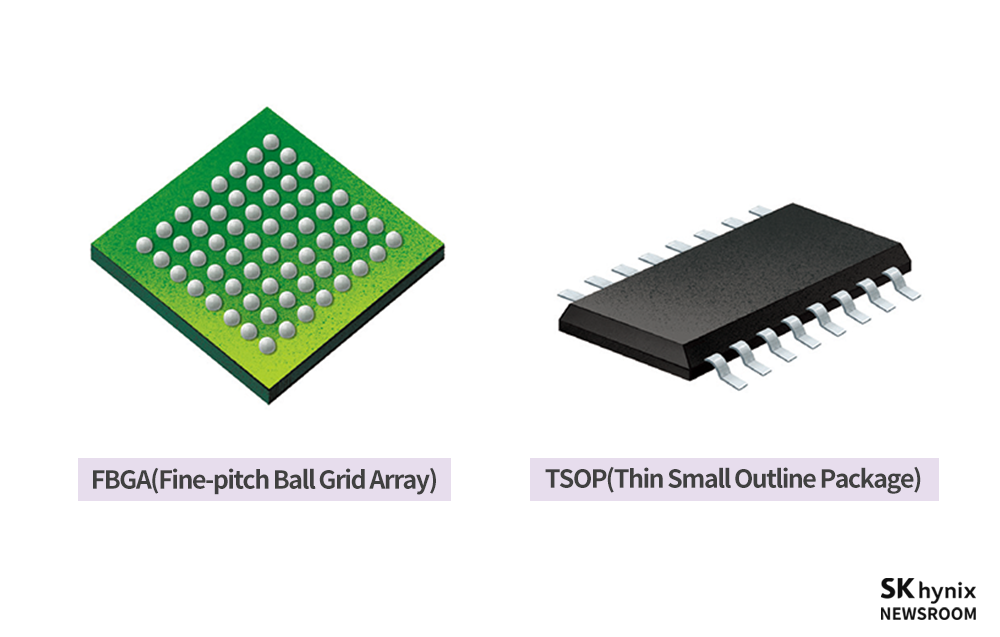

<그림 2>에서처럼 외부와 전기적/기계적 접속을 위해 솔더*낮은 온도에서 녹을 수 있으므로 전기/기계적 접합을 동시에 할 수 있게 하는 금속 볼(solder ball) 이나 리드(lead)**가 핀(pin)이 되어 있는 모양이 요즘 가장 일반적인 반도체 패키지 형태이다.

* 솔더: 낮은 온도에서 녹을 수 있으므로 전기/기계적 접합을 동시에 할 수 있게 하는 금속

** 리드(lead): 전자 회로 또는 전자 부품의 단자에서 나오는 선으로 전자 부품을 회로 기판에 연결하기 위해 사용

▲ 그림 2 : 반도체 패키지의 예(ⓒ한올출판사)

#2. 반도체 패키지의 역할

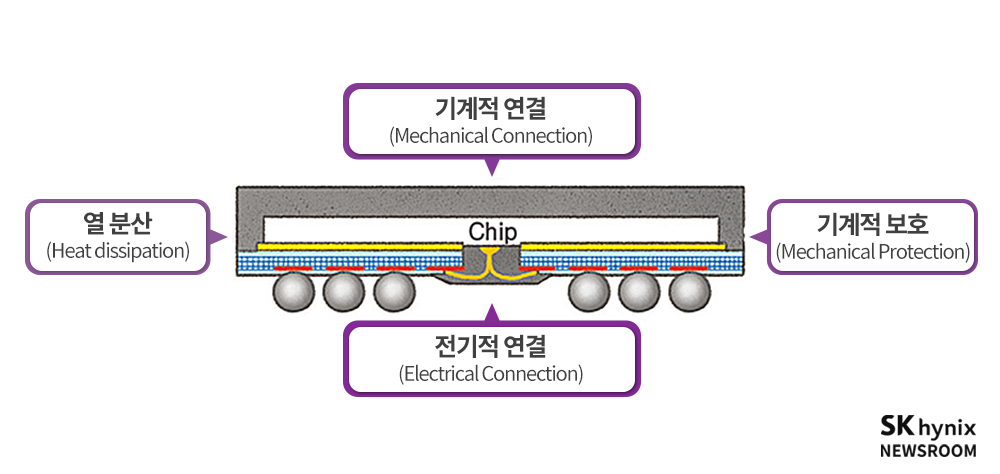

<그림 3>은 반도체 패키지의 역할을 모식도로 표현한 것으로 반도체 패키지는 기계적 보호(Protection), 전기적 연결(Electrical Connection), 기계적 연결(Mechanical Connection), 열 방출(Heat Dissipation) 등의 4가지 주요한 역할을 한다.

패키지의 사전적 의미는 포장된 물품이다. 우리는 왜 물건을 포장할까? 여러가지 이유가 있겠지만, 가장 큰 이유중의 하나는 내용물을 보호하기 위해서다.

반도체 패키지의 가장 큰 역할 또한 내용물을 보호하는 것이다. 여기서 내용물은 바로 반도체 칩/소자이며, <그림 3>의 가운데 하얀 부분이 될 것이다. 반도체 패키지는 반도체 칩/소자를 EMC(Epoxy Mold Compound)와 같은 패키지 재료로 감싸, 외부의 기계적 및 화학적 충격으로부터 보호하는 역할을 한다. 반도체 칩은 수백 단계의 웨이퍼 공정으로 메모리·로직 등의 기능을 할 수 있게 만들어졌지만, 기본적인 재료는 실리콘이다. 실리콘은 우리가 알고 있는 유리 조각처럼 쉽게 깨질 수 있다. 또한 웨이퍼 공정으로 형성된 구조체들은 기계적, 화학적 충격에도 취약하다. 그러므로 패키지 재료로 그 칩들을 보호해야 하는 것이다.

▲ 그림 3 : 반도체 패키지의 역할(ⓒ한올출판사)

그리고 패키지는 물리적/전기적으로 칩을 시스템에 연결하는 역할을 한다. 전기적으로는 칩과 시스템을 연결해 칩에 전원을 공급하고, 원하는 기능을 할 수 있도록 신호를 입력하거나 출력할 수 있는 통로를 만들어야 한다. 또한 기계적으로는 칩이 사용되는 동안 시스템에 잘 부착되어 있도록 잘 연결해야 한다. 동시에 칩/소자에서 발생하는 열을 빠르게 발산시켜 주어야 한다. 반도체 제품이 동작한다는 것은 전류가 흐른다는 것이다. 전류가 흐르면 필연적으로 저항이 생기며 그에 따른 열이 생긴다. <그림 3>과 같이, 반도체 패키지는 칩을 완전히 둘러싸고 있다. 이때 반도체 패키지가 열을 잘 발산하지 못하면 칩이 과열되고 내부 트랜지스터의 온도가 동작가능온도 이상으로 올라 결국 트랜지스터의 동작이 멈추는 상황이 생길 수도 있다. 그러므로 반도체 패키지는 효과적으로 열을 발산해주는 역할이 필수다. 반도체 제품의 속도가 빨라지고, 기능이 많아짐에 따라 패키지의 냉각 역할의 중요성은 점점 더 커지고 있다.

#3. 반도체 패키지의 개발 트렌드

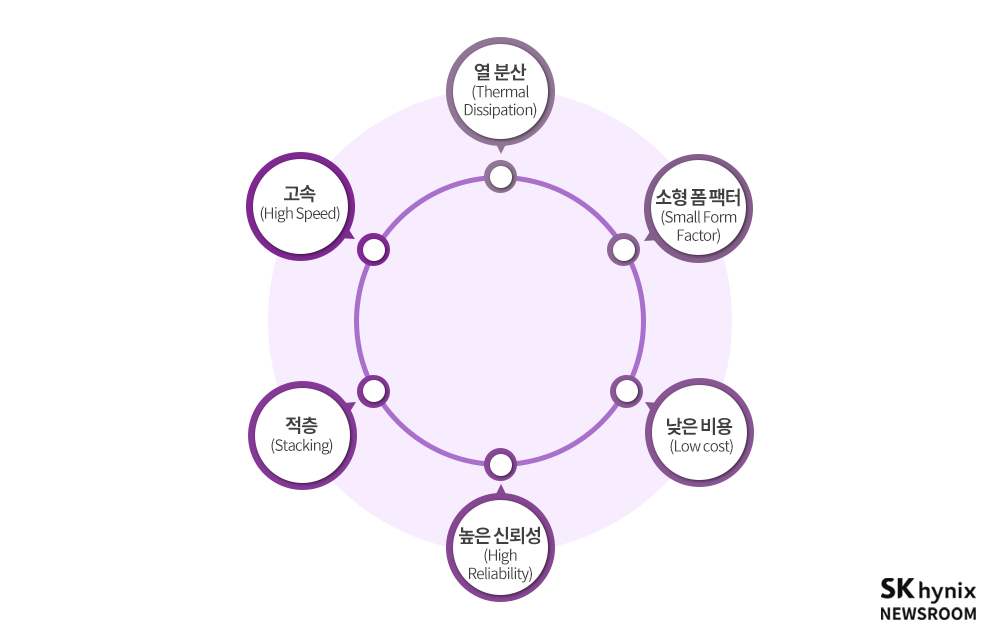

아래의 <그림 4>는 반도체 패키지 기술의 개발 트렌드를 6가지로 정리한 것이다.

반도체 패키지는 그 역할을 잘할 수 있도록 기술이 발전해왔다. 열 방출의 역할을 잘하기 위해서 열전도도*가 좋은 재료를 개발했고, 반도체 패키지 구조도 열 방출을 잘 할 수 있게 설계 및 제작되어 왔다.

* 열전도도: 물질 이동을 수반 없이 고온부에서 이것과 접하고 있는 저온부로 열이 전달되는 현상을 표현하는 척도

고속 전기 신호전달(High Speed) 특성을 만족시킬 수 있는 반도체 패키지 기술 개발도 중요한 트렌드다. 만약 20Gbps* 속도까지 나올 수 있는 칩/소자를 개발하였는데, 그것에 적용되는 반도체 패키지 기술이 2Gbps 속도만을 대응할 수 있다고 하면 결국 시스템에서 인지하는 반도체 제품의 속도는 20Gbps가 아닌 2Gbps이다. 칩이 아무리 속도가 빠르다고 해도 시스템으로 나가는 전기적 연결 통로는 패키지에서 만들어지기 때문에 반도체 제품의 속도는 패키지에 큰 영향을 받는다. 그러므로 칩의 속도가 빨라졌다면 그에 대응하는 반도체 패키지도 빠른 속도가 구현되는 기술로 개발되어야 하는 것이다. 이러한 경향은 최근 인공지능 및 5G 무선통신 기술에서 더욱 도드라진다. 플립 칩(flip chip) 패키지 기술, 실리콘 관통 전극(TSV)을 이용한 패키지 기술 등이 모두 고속 특성을 위해 개발된 패키지 기술이다.

* Gbps: Giga bit per second의 약자로 초당 이동하는 기가 비트 정보량을 의미

▲ 그림 4 : 반도체 패키지 기술 개발 트렌드(ⓒ한올출판사)

3차원 반도체 적층(stacking)기술은 반도체 패키지 기술 개발의 획기적으로 중요한 트렌드이다. 기존에 반도체 패키지는 하나의 칩 만을 패키지 하였지만, 이제는 한 패키지에 여러 개의 칩을 넣은 MCP(Multichip Package), SiP(System In Package)*기술들이 개발되었다.

* SiP(System In Package): System In Package의 약자로 여러 소자를 하나의 패키지로 만들어 시스템을 구현하게 하는 패키지의 일종

또 하나의 패키지 기술 개발 트렌드는 소형화이다. 반도체 제품들이 모바일뿐만 아니라 웨어러블(wearable)*로까지 적용 범위가 넓어지면서 소형화는 고객의 중요한 요구 사항이다. 그러므로 이를 만족시키기 위해서 패키지 크기를 줄이는 기술 개발이 많이 이루어져 왔다.

* 웨어러블(wearable): 반도체 제품들이 옷처럼 몸에 착용하고 사용하게 되는 적용 범위

반도체 제품들은 점점 더 다양한 환경에서 사용되고 있다. 일상적인 환경에서뿐만 아니라, 열대 우림, 극지방, 심해에서도 사용되고 있고, 우주에서도 사용된다. 패키지의 기본 역할이 칩/소자의 보호(protection)이므로 이런 다양한 환경에서도 반도체 제품이 정상 동작할 수 있도록 신뢰성(Reliability)이 높은 패키지 기술이 개발되어야 한다.

동시에 반도체 패키지는 곧 최종 제품이므로, 원하는 기능을 잘 발휘하면서도 제조 비용까지 낮출 수 있는 기술개발이 중요하다.

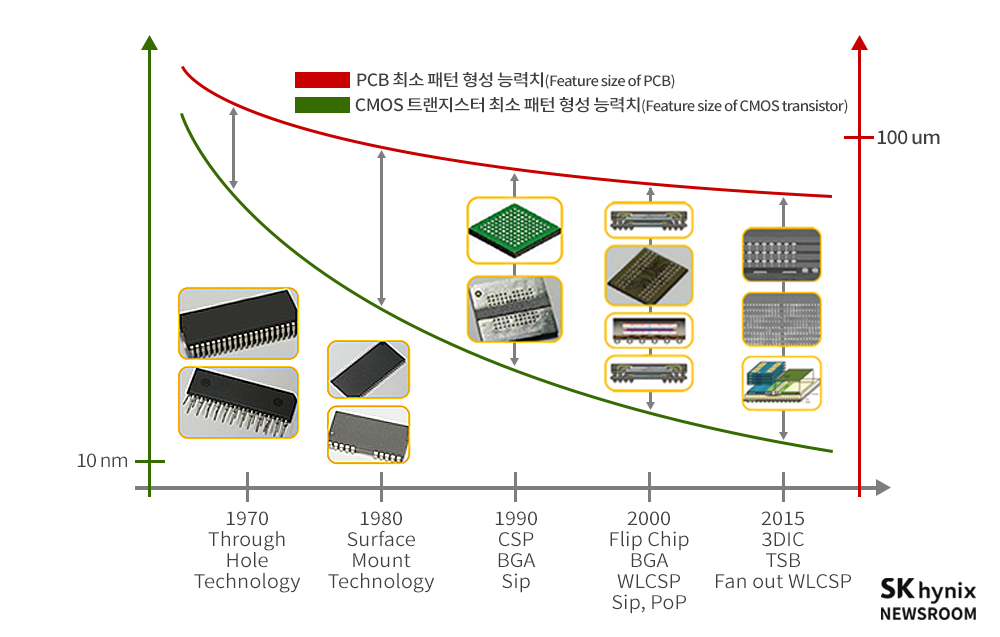

▲ 그림 5 : 연도에 따른 웨이퍼와 PCB기판의 최소 패턴 형성 능력치 변화(ⓒ한올출판사)

반도체 패키지 기술 개발 트렌드를 6가지로 정리하였는데, 이렇게 반도체 패키지 기술 개발을 하게 만든 또 다른 구동력은 반도체 업계 전체의 기술 개발 트렌드 때문이었다. <그림 5>는 그것을 표현한 것이다. 그림의 붉은색 선은 반도체 패키지가 조립 과정 중에 실장될 PCB 기판의 최소 패턴을 만들 수 있는 능력치(Feature size)를 나타낸 것이다. 초록색 선은 웨이퍼에서 최소 패턴을 만들 수 있는 능력치를 나타낸 것이다.

1970년대에는 PCB 기판과 웨이퍼의 최소 패턴을 만들 수 있는 능력치 차이가 크지 않았다. 그런데, 지금 웨이퍼의 경우에는 10nm 이하까지 양산, 개발하고 있는 단계이지만, PCB 기판은 100um대다. 차이가 크게 벌어진 것이다.

PCB 기판은 판넬(panel)형태로 제작되고, 원가 절감의 이슈 등으로 최소 패턴을 만드는 능력치가 많이 작아지지 않았다. 하지만 웨이퍼의 경우에는 포토 공정의 발달로 드라마틱하게 작아졌기 때문에 점점 차이가 벌어졌다. 문제는 반도체 패키지는 웨이퍼에서 잘린 칩을 단품화하여 PCB 기판에 실장하는 역할을 해야 하므로, PCB 기판과 웨이퍼의 차이를 보상해 주어야 한다는 것이다. 1970년대에는 능력치의 차이가 크지 않아서 DIP(Dual Inline Package), ZIP(Zigzag Inline Package) 등 PCB 기판에 있는 구멍에 반도체 패키지에 있는 리드(lead)를 삽입하여 실장하는 쓰루홀(Through hole) 기술을 반도체 패키지에 사용할 수 있었다. 하지만 차이가 점점 벌어져서 TSOP(Thin Small Outline Package) 같은 표면 실장형 패키지로 리드를 기판의 표면에 붙이는 표면 실장(Surface Mounting Technology:SMT) 기술을 사용해야 했다. 그 이후에도 솔더볼로 실장하는 BGA(Ball Grid Array), 플립 칩, 팬아웃(Fan out) WLCSP, 실리콘 관통 전극 같은 반도체 패키지 기술이 차례로 개발되어 벌어지는 웨이퍼와 기판의 차이를 보상해 주게 되었다.

#4. 반도체 패키지 개발 업무 과정

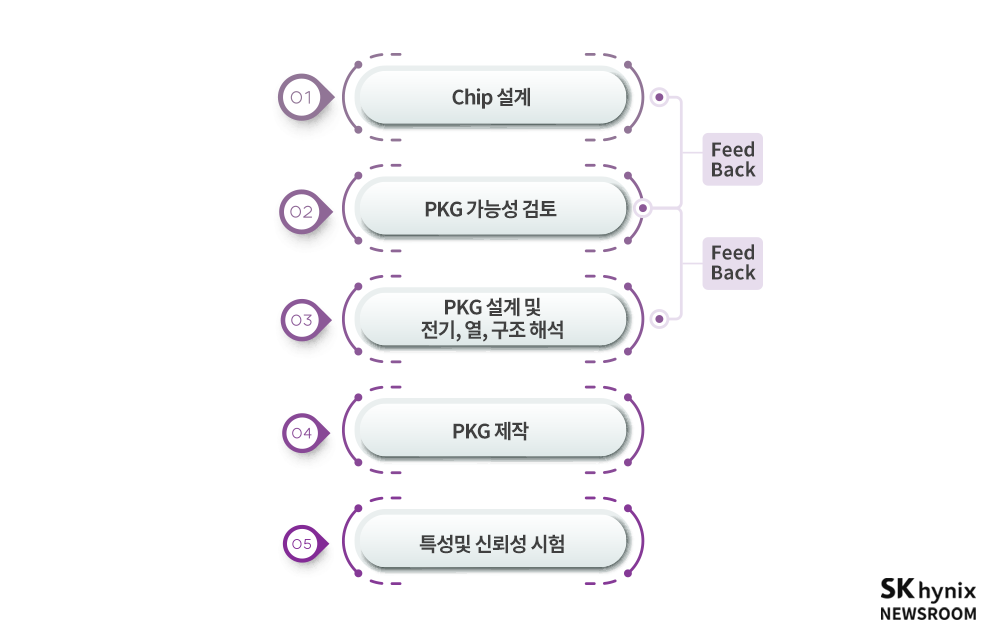

반도체 패키지 개발은 2가지 경우가 있다. 첫 번째는 반도체 칩이 새로 개발되어 그것을 반도체 패키지로 만들어 평가를 통해 개발을 완료하는 것이고, 두 번째는 새로운 반도체 패키지 기술을 개발하기 위해 기존의 칩을 새로운 패키지 기술로 검증/개발하는 것이다.

일반적으로 새로운 칩을 개발하면서 동시에 새로운 패키지 기술을 같이 적용하는 경우는 없다. 왜냐하면 칩도 새로운 기술이고, 패키지도 검증되지 않은 기술이면 패키지 후 불량이 발생했을 때 원인을 찾는 것이 너무 어렵기 때문이다. 그래서 새로운 반도체 패키지 기술은 불량이 거의 없는 기존 양산 칩에 적용해서 패키지 기술만을 검증한다. 그리고 이렇게 검증된 패키지 기술을 새로운 칩을 개발할 때 적용하여 반도체 제품을 개발하는 것이다.

<그림 6>은 첫 번째 경우의 개발 과정을 표현했다. 어떤 반도체 제품이 개발될 때 칩 설계와 패키지 설계가 따로 진행되지 않는다. 반드시 칩과 패키지가 결합하여 전체적으로 특성이 최적화될 수 있도록 설계되어야 한다. 그 때문에 칩이 설계되기 전에 이 칩이 실제 패키지가 가능한지를 패키지 부서에 검토 요청한다. 가능성 검토를 할 때는 실제 패키지 설계를 개략적으로 진행해 보고, 전기/열/구조 해석을 통해서 실제 양산시에 문제가 없는지도 검토한다. 여기서 반도체 패키지 설계는 칩이 기판에 실장 되기 위한 매개체가 되는 서브스트레이트(substrate) 또는 리드프레임(Leadframe)의 배선* 설계를 의미한다.

* 배선: 한 소자 안에 만들어진 전기적 신호가 지나가는 통로

패키지 부서에서는 패키지 가설계와 해석을 통한 검토 결과를 바탕으로 패키지 가능성에 대해서 칩 설계 담당자에게 피드백한다. 패키지가 가능하다고 가능성 검토가 완료되어야 비로소 칩 설계가 완료되고, 이어서 웨이퍼 제작을 하게 된다. 이렇게 웨이퍼가 제작되는 동안 패키지 부서에서는 패키지 제작에 필요한 서브스트레이트 또는 리드프레임을 설계하고, 제작 업체를 통해서 제작을 진행한다. 동시에 패키지 공정을 위한 툴(Tool) 등도 미리 준비하여 칩이 구현된 웨이퍼가 웨이퍼 테스트 후 패키지 부서에 인계되었을 때 바로 패키지 제작을 진행한다.

▲ 그림 6 : 반도체 패키지 개발 과정(ⓒ한올출판사)

반도체 제품은 패키지로 제작되어야 실제적인 특성을 측정 및 확인할 수 있다. 설계가 잘 되었는지, 공정이 잘 진행되었는지 확인할 수 있으며 신뢰성 시험 등을 진행할 수 있다. 특성 및 신뢰성을 만족 못하는 경우에는 그 원인을 분석하여, 원인을 해결할 수 있는 단계부터 앞의 과정을 다시 반복하고, 원하는 특성 및 신뢰성 기준을 만족해야 개발이 완료된다.