지난 장에서는 실리사이드(Silicide)의 목적(낮은 접촉 저항 확보)과 특성(쇼트키 특성 배제 및 접촉 저항성 특성 보유)에 대해 살펴봤다면, 이번 장에서는 실리사이드를 트랜지스터(Transistor, TR) 구조에서 구체화하는 방식을 알아보도록 하겠습니다. 금속배선 공정 중 가장 먼저 실시하는 ‘살리사이드(Salicide)’란 Self-Alignment(자체 정렬)와 Silicide(실리사이드)의 합성어로, 금속 입자가 실리콘 격자 속으로 확산해 실리사이드층을 자동으로 형성하는 공정을 뜻합니다. 결정격자를 이루는 실리콘과 금속원소의 혼합물인 실리사이드를 만들기 위해서는 먼저 PVD(Physical Vapor Deposition) 혹은 CVD(Chemical Vapor Deposition) 방식으로 금속막을 증착시킨 후, 어닐링(Annealing) 방식으로 높은 열에너지를 가해 금속원소가 실리콘 원자와 결합하도록 만들어 실리사이드라는 패턴을 만듭니다. 살리사이드의 경우 일반적인 방식과는 달리 절연막-증착, 포토, 절연막-식각 공정을 절약할 수 있다는 장점이 있습니다.

1. 실리사이드(Silicide)층 설치 준비

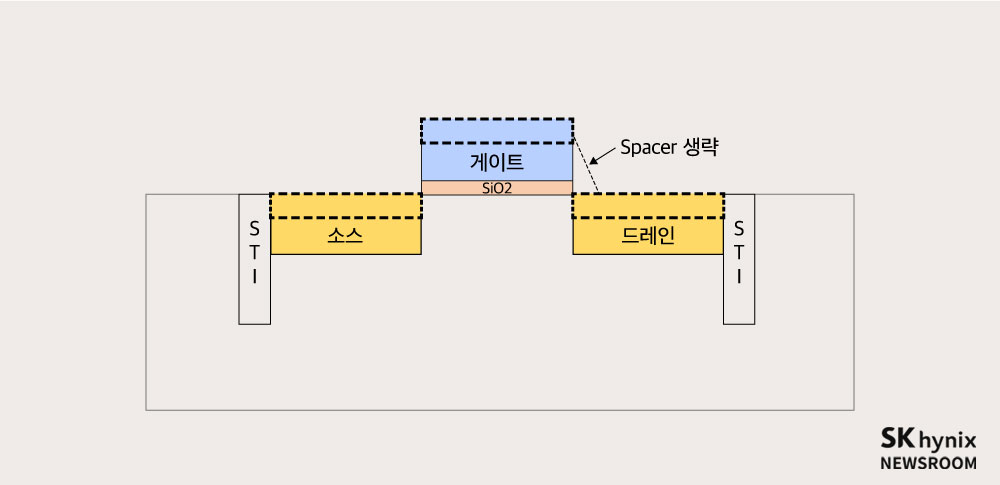

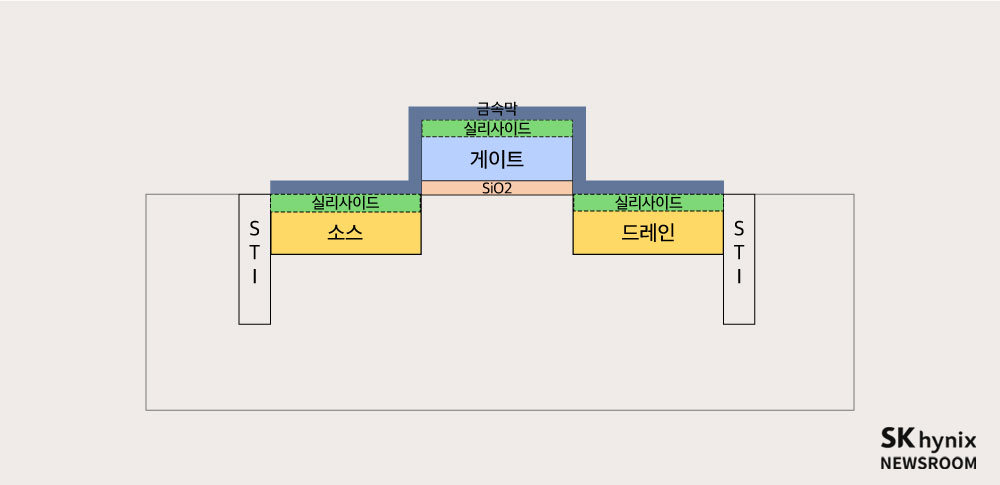

<그림1> 살리사이드(Salicide)를 적용하기 위한 준비

살리사이드(Salicide)를 적용하기 위해 FEOL(Front End Of Line, FAB 공정 중 앞부분 공정)이 완료된 트랜지스터(Transistor, TR)에 BEOL(Back End Of Line, FAB 공정 중 뒷부분 공정)의 첫 공정인 실리사이드(Silicide) 설치를 준비합니다. STI(Shallow Trench Isolation)가 TR 좌우에 구축돼 인접 트랜지스터와 상호 연결되는 누설전류가 차단됩니다. ▶<[반도체 특강] 소자분리막, 미세화 탈환을 위한 참호막(STI) 구축하기> 편 참고 (위 그림에서 게이트 단자를 둘러쌓고 있는 스페이서(Spacer)는 혼동을 방지하기 위해 미표기함) 먼저 웨이퍼 표면에 존재하는 자연 산화막과 파티클(Particle), 유기물 혹은 무기물로 오염된 부위를 세정합니다. 세정 시 강력한 산화막을 제거하려면, 웨이퍼 전체 표면을 타깃으로 선택비를 고려할 필요 없이 플라즈마 방식을 이용해 실시합니다. 실리사이드를 설치할 때 소스/드레인 단자의 표면은 단일 실리콘 격자 상태이지만, 게이트 단자 표면은 다결정 실리콘 격자로 약간 상이하므로 재질과 방식을 다르게 적용해야 합니다. 하지만, 동일한 재질과 방식으로 적용해도 저항치 등을 목표 영역(Criteria) 내로 조율(Meet)할 수 있어 공정 절약을 위해 일반적으로는 획일적으로 공정을 진행합니다. <그림1>에서 각 3개 단자의 상부에 위치한 점선은 실리사이드층을 형성시킬 자리입니다(실제적인 웨이퍼 두께는 단자들의 두께에 비해 그림보다는 몇십~몇백 배 두껍답니다).

2. 금속막 증착

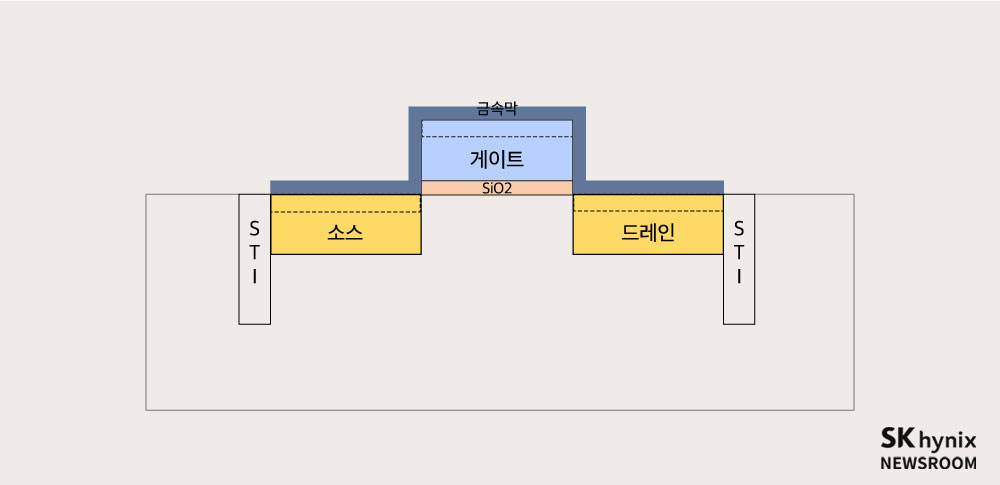

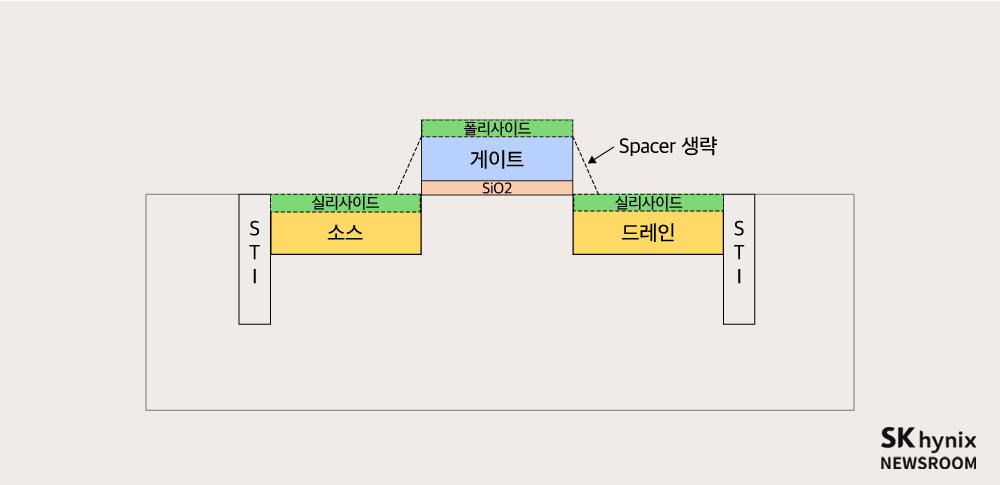

<그림2> 금속막 증착 @ PVD 혹은 CVD(Spacer 생략)

실리사이드층을 설치할 준비가 완료되면, PVD(Physical Vapor Deposition) 공정에서 스퍼터링(Sputtering) 방식을 이용해 웨이퍼 전면에 금속막을 증착시킵니다. ▶<[반도체 특강] PVD, 전자가 이동하는 도로를 만들다> 편 참고 이때 금속 재질로는 티타늄(Ti), 코발트(Co), 니켈(Ni) 등을 사용하는데, 각 재질에 따라 실리사이드층을 형성하는 최대 두께가 달라집니다. 또 분위기 온도에 따라 저항치가 변하므로, 어떠한 실리사이드로 형성시킬 것인지를 고려해 금속성 원소를 선택하지요.

금속막을 형성할 때에는 스퍼터링 방식이 아니어도 열 방식 혹은 전자빔을 이용해 금속 입자들을 증기(Vapor) 형태로 공간 속으로 퍼지게 해(증발) 웨이퍼 표면에 달라붙도록 합니다. 이때 측벽(Sidewall) 방향의 증착막은 사용하지 않는 막이므로, 단차피복성(Step Coverage)이 뛰어날 필요는 없습니다. 단, 단자별로 저항치를 동일하게 관리해야 하므로, 수평 표면 증착막의 두께를 일정하게 관리할 필요가 있지요.

3. 실리사이드(Silicide)층 형성

<그림3> 실리사이드(Silicide)층 형성 @ 초기 어닐링

금속막을 증착한 뒤 어닐링 방식으로 열에너지(섭씨 500~900도)를 인가하면, 금속 원소가 하부 막질로 확산해 격자를 구성하고 있는 실리콘 원자들과 결합합니다(금속(Ti, Co, Ni)+Silicon=TiSi2, CoSi2, NiSi). 그리고 금속이 실리콘과 결합해 실리사이드라는 층을 형성하지요. 이때 실리콘 격자는 단일 결정(게이트는 다결정)으로 되어 있어, 금속입자들이 확산하기에 수월합니다. ▶<[반도체 특강] 웨이퍼를 담금질하다: 파괴를 복원하는 어닐링(Annealing)> 편 참고

어닐링은 주로 RTA(Rapid Thermal Annealing) 방식을 사용하며, 온도는 재질에 따라서 변합니다. 티타늄(Ti)을 사용할 때 가장 높은 온도를 인가해야 하며 코발트(Co), 니켈(Ni) 순으로 온도를 낮춰 진행합니다. 하지만 같은 재질이라도 온도에 따라 저항값이 변하므로 온도-저항치를 적절하게 매칭해 소자의 기능과 공정상의 문제점을 Trade-Off 방식으로 타협해 결정해야 합니다.

예를 들어 니켈(NiSi)의 경우 일정하게 낮은 온도로 어닐링을 진행했다면, 낮은 저항값을 가질 수 있으며 매우 얇은 층을 형성할 수 있는 장점이 있습니다. 대신 그 다음 공정을 진행할 때 어닐링 당시의 온도보다 더 높은 온도를 적용하지 못한다는 문제가 발생하게 되지요. 따라서 금속막을 형성할 때 PVD보다는 금속 재질 선택에 있어 유연성이 떨어지지만, 적절히 방식과 재질이 매칭만 된다면 고온에서도 견딜 수 있도록 접착력이 좋은 CVD를 활용하는 것도 또 다른 방법이 된답니다. ▶<[반도체 특강] 화학적으로 막을 성장시키는 방법, CVD(Chemical Vapor Deposition) 편 참고

4. 금속막 제거(Strip)

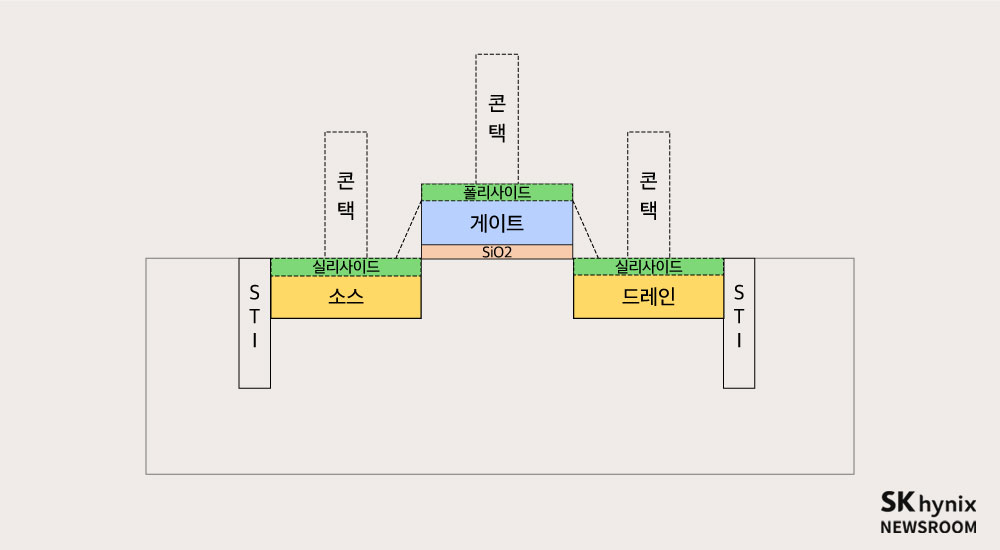

<그림4> 금속막 제거 @ 식각 방식(Spacer 생략)

살리사이드(Salicide, Self Alignment Silicide)는 실리사이드가 스스로 정렬됐다는 의미를 가집니다. 이는 금속막을 증착한 후 어닐링을 함으로써 하부막에 자동으로 실리사이드 막이 설치됐기 때문에 붙여진 명칭이지요. 게이트 단자에 실리사이드 막으로 형성된 폴리사이드(Polycide)는 폴리실리콘(Poly Silicon)과 실리사이드(Silicide)의 합성어로, 게이트 층이 폴리층이므로 이곳에 실리사이드를 만들었다는 의미입니다(소스나 드레인 단자에 생성된 실리사이드는 그냥 실리사이드층이라고 하지요). 실리사이드층이 형성되면 상부에 존재하는 금속층(PVD나 CVD로 증착)은 이제 쓸모가 없어지므로 식각을 통해 제거(Strip)합니다. 이때 식각은 스페이서 등 절연막에 손상 없이 금속막만을 제거할 수 있도록 선택비가 높은 습식식각 방식을 선택해 빠른 속도로 진행하지요.

5.실리사이드(Silicide)층 완성

<그림5> 실리사이드(Silicide)층 완성 @ 두 번째 어닐링

금속층 제거를 마치면 2차 RTA(1차와 유사한 온도 조건)를 진행해 실리사이드 및 폴리사이드가 확고하게 자리 잡을 수 있도록 합니다. 어닐링을 짧게 2번 실시하는 이유는 금속에 오랫동안 높은 온도를 가할 경우 모든 경계면(Junction)으로 금속 성분이 침투해 누설전류의 통로를 형성할 위험이 있어 이를 방지하기 위함입니다. 예를 들어 게이트(Gate)와 스페이서 사이의 접합면을 타고 금속이 침투하기도 하지요.

실리사이드층이 웨이퍼 표면에 드러나면, 그 상부에 금속성 재질로 연결되는 콘택(Contact)을 연결합니다. 이때 실리사이드의 재질에 따라 비저항 값이 정해져 소스/드레인/게이트 단자와 콘택 사이에는 쇼트키 다이오드(Schottky Diode) 특성이 없어지고 저항성 기능을 갖게 됩니다. 반도체의 숙명은 TR의 입체적인 크기가 축소되는 방향이므로 단자와 금속 사이의 접촉되는 면적이 줄어들 수밖에 없습니다. 그에 따라 면저항(Rs) 값도 당연히 상승하게 되지요. 그러나 실리사이드층을 통과하는 전자의 입장에서는 높은 저항은 허락되지 않으므로, 금속 재질을 변경하고 공정 온도를 조정해서라도 저항치를 낮춰줘야 합니다. 따라서 의도한 목적에 따라 소자가 올바르게 작동하고, 소자의 동작 속도가 늦춰지지 않도록 재질-구조-방식을 설정합니다.

실리콘과 금속성 재질을 연결하는 방식과 위치에 따라 달리 부르는 살리사이드와 실리사이드, 폴리사이드에 대해 두 개의 챕터에 걸쳐 알아보았습니다. 실리사이드 역시 재질, 온도, 방식을 변화시켜 비저항, 표면저항, 쇼트키 기능 제거, 실리사이드층 두께, 누설전류 유발, 확산 Barrier, RTA 온도 최대치 등을 조정하지요. 그렇게 하여 트랜지스터가 제 기능을 수행할 수 있도록 도와줍니다.

※ 본 칼럼은 반도체/ICT에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.