예부터 금속으로 무언가를 만들 땐 금속을 불에 달궈 재질을 연하게 한 후, 물리적 압력을 가해 모양을 잡습니다. 그리고 높은 온도로 장시간 담금질을 하여 원래의 금속 성질을 내도록 하거나 더욱 좋은 재질로 변질할 수 있도록 하죠. 웨이퍼도 열처리를 하는 담금질 공정이 있습니다. 이온-임플란테이션은 웨이퍼 안팎으로 상처를 내는 공정인데, 이런 물리적 행위를 진행한 후에는 상처가 아물도록 화학적 변화를 주는 ‘어닐링(Annealing)’ 을 진행합니다. 반도체 제조공정 중 이온-임플란테이션 후 공정 이외에도 불순물을 활성화할 때, 박막(CVD)을 형성할 때, Ohmic 접촉 합금 공정을 진행할 때 혹은 Glass(BPSG) Reflow를 진행할 때 어닐링과 같은 유사한 열처리를 진행합니다. 이번 시간에는 이온-임플란테이션 후에 진행하는 어닐링에 초점을 맞춰 알아보도록 하겠습니다.

어닐링이 필요한 이유: 공유결합의 파괴

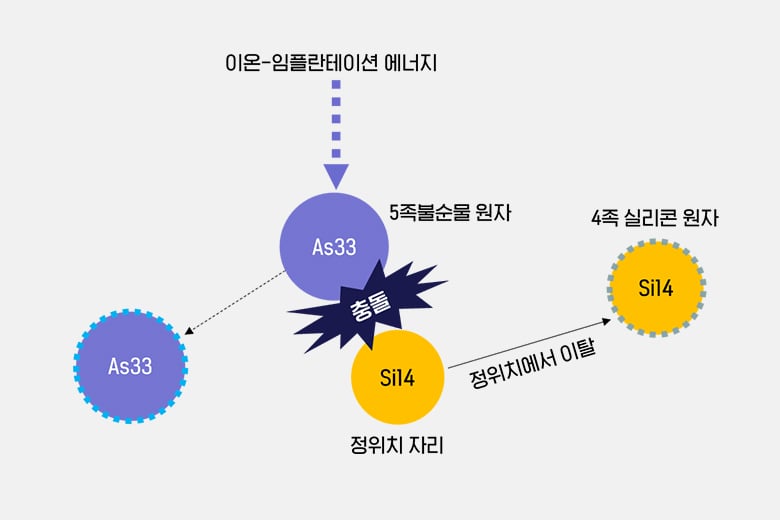

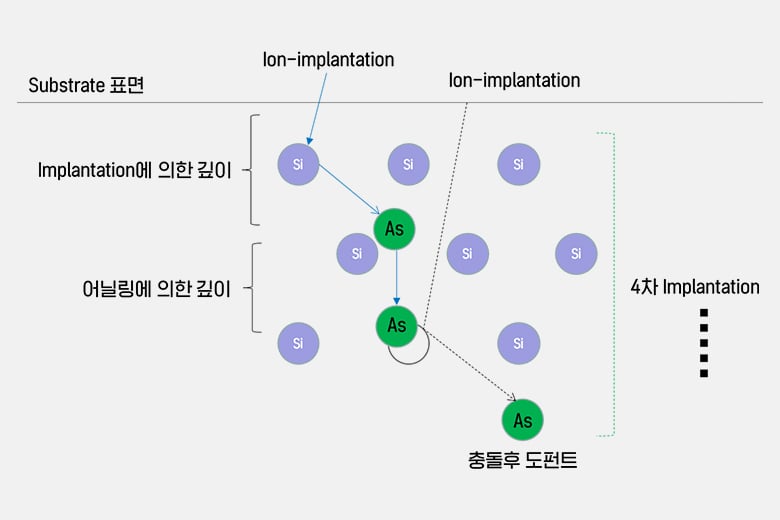

▲ 이온-임플란테이션시의 실리콘 원자와 불순물 원자(도펀트)의 충돌

이온-임플란테이션 할 때에는 높은 충돌 에너지로 인해 웨이퍼 표피조직이 파괴됩니다. 내부의 실리콘 격자는 불순물 원자(3족 혹은 5족)의 침투로 인해 공유결합하고 있던 실리콘의 일부 원자들이 본래의 정위치에서 일부 밀려나 있거나 멀리 떨어져 나가 있습니다. 도펀트(불순물 원자)들도 실리콘 원자들과의 충돌로 인한 충격으로 실리콘 원자의 정위치에 자리하지 못하고 근방에서 서성이게 되지요. 매우 드물지만, 어떤 도펀트는 실리콘 원자를 밀어내고 운 좋게 그 자리에 들어가 앉아 있는 경우도 있습니다. 그러나 대부분의 도펀트는 제자리를 찾지 못하므로 어닐링을 통해 실리콘 원자가 앉아있던 자리에 찾아 들어가도록 해야 합니다. ▶<이온-임플란테이션 방식을 이용한 소스와 드레인 단자> 편 참조

어닐링의 목적① 불순물원자와 실리콘 원자의 치환

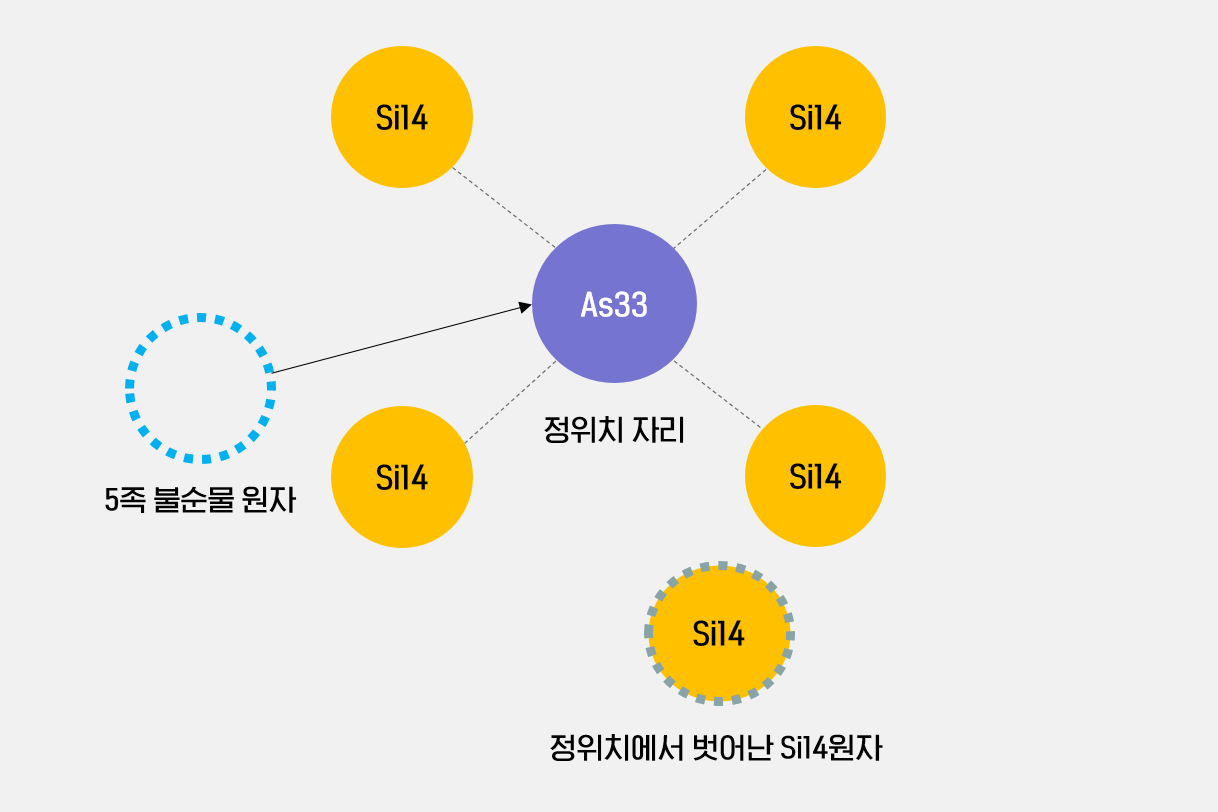

▲ 실리콘 원자와 도펀트(불순물 원자)의 치환

어닐링을 실시하는 목적 중 첫 번째는 4족 원소를 불순물(5족 혹은 3족) 원소로 화학적으로 치환(스위칭)하는 데 있습니다. 어닐링은 이온-임플란테이션을 시행 후, 튕겨져 나간 도펀트(불순물인 5족 혹은 3족의 원자)를 원래 실리콘 4족 원자가 들어서 있던 정위치로 가게 합니다. 이때 충돌로 인해 제자리에서 벗어난 실리콘 원자가 도펀트보다 먼저 제자리로 복귀할 수도 있으나, 정위치로부터 떨어진 위치가 도펀트보다 거리상 더 멀리 있어서 확률적으로 도펀트가 더 유리하지요. 그리고 실제 투입하는 도펀트 농도는 실리콘 입자농도(1×10^22개 /cm^3)에 비해 1,000분의 1 혹은 1,000만분의 1 정도의 수준(숫자: 1×10^15 ~ 1×10^19개/cm^3)으로 Si14 숫자에 비하면 매우 적은 농도이기 때문에 실리콘의 격자구조가 파괴되어도 실리콘 기반의 substrate가 문제 되지는 않습니다.

어닐링의 목적② 파괴된 격자구조 복원

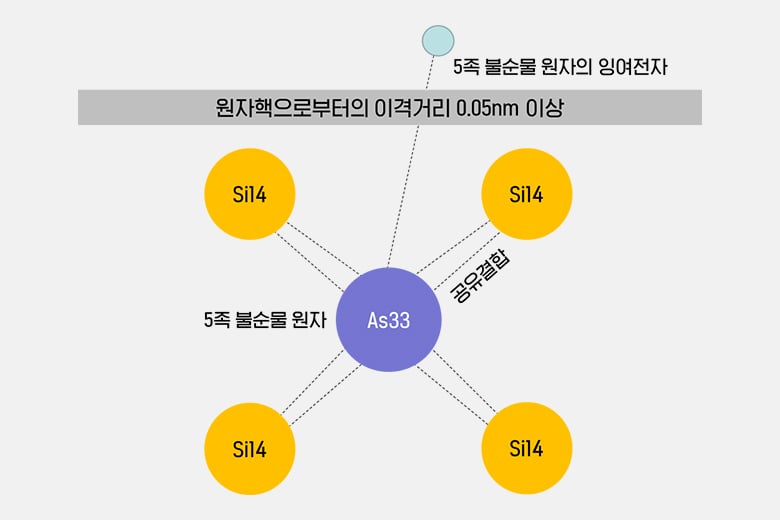

▲ 공유결합의 복원 : 5족 불순물 원자(도펀트) 1개와 실리콘 원자 4개

어닐링을 실시하는 두 번째 목적은 파괴된 공유결합을 화학적으로 다시 복원하는 데 있습니다. 실리콘 만으로 연결된 격자구조는 실리콘 1개가 주변의 4개 실리콘 원자와 연결되어 있습니다. 이러한 결합은 Si14 별로 모두 1개씩의 전자를 상대방에 내놓고, 양쪽 원자들이 2개의 전자를 공유하면서 결합하고 있는 형태인데요. 어닐링은 이온-임플란트 시에 끊어진 공유결합이라는 연결 다리를 도펀트와 실리콘 원자 사이에 다시 이어놓는 역할을 합니다. 5족 원자 입장에서는 어닐링 시에 받은 열에너지를 이용하여 주변 4개의 개별 실리콘 원자들과 각각 1개씩 내놓은 전자를 이용하여 총 4개의 전자쌍(electron pair)을 도펀트 1개와 실리콘 4개 원자가 공유하지요. 그렇게 되면 원자 간의 결합으로 도펀트와 각각의 Si14들은 총 8개 전자를 공유하고, 나머지 1개는 잉여전자로 5족 도펀트의 주변에 머물게 합니다.

즉, 구조적으로는 굴러들어온 도펀트를 원래의 격자구조 자리(Si14가 있었던 자리)로 이동시키거나, 혹은 도펀트가 다른 Si14들과 새롭게 격자구조(공유결합)를 생성합니다. 이때 잉여전자 1개는 구심력은 크지는 않지만 도펀트 원자핵으로부터 약간 먼 거리(Si14 최외각전자의 원자핵으로부터 이격거리인 0.05nm 이상)에 있으면서도 5족원자(도펀트)에 붙어 있기 때문에 떨어지지는 않습니다.

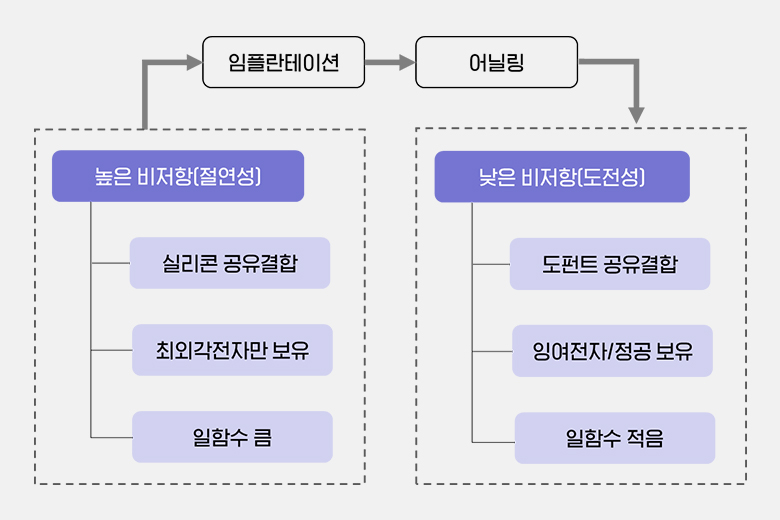

어닐링의 역할① 절연성 물질을 도전성 물질로 변신

▲ 이온-임플란테이션과 어닐링을 통하여 높은 비저항(절연성)를 낮은 비저항(도전성)으로 변신

순수실리콘 반도체는 거의 절연체 수준(OFF)입니다. 어닐링은 실리콘 원자를 도펀트로 치환시킴으로써 소스와 드레인 단자에 전압이 가해질 때 전자가 흐르는 도전성 물질(ON)이 되도록 만듭니다. 순수실리콘일 때는 Cubic cm 당 1.5×10^10개의 전자나 정공이 발생하지만, 이 정도의 전자 입자 개체수로는 전류가 흐른다고 보기 어렵습니다. 따라서 어닐링은 위치변경과 공유결합을 통해 도핑된 도펀트가 전자를 내주고(도너 역할: 5족 불순물 원자결합), 혹은 전자를 받을 수 있도록(억셉터 역할: 3족 불순물 원자결합) 준비시키는 공정이라고 할 수 있지요.

어닐링의 역할② 도펀트의 확산 깊이를 조절

▲ 어닐링에 의한 도펀트의 깊이 확산의 예

반도체 제조공정은 섭씨 500~1,000도까지 높은 온도를 사용하는 경우가 많습니다. 따라서 전(前)공정에서 진행한 여러 파라미터들이 후(後)공정의 높은 온도 조건에 의해 틀어지는 경우가 종종 발생하게 되는데요. 이때 열처리의 일종인 어닐링을 실시하면 파라미터들의 변경 요소가 줄어들게 됩니다. 또 임플란테이션이 완료된 원자들을 필요한 깊이까지 추가적으로 확산을 시킬 수 있답니다(그러나 도펀트들이 수직축뿐 아니라 수평축으로도 확산될 수 있다는 단점이 있습니다). 반대로 어닐링이 완료된 후에는 외부 조건(추가적인 높은 온도 공정)으로 인해 도펀트(특히 3족 B5)들이 불필요하게 확산되는 부분들을 많이 줄여 주지요.

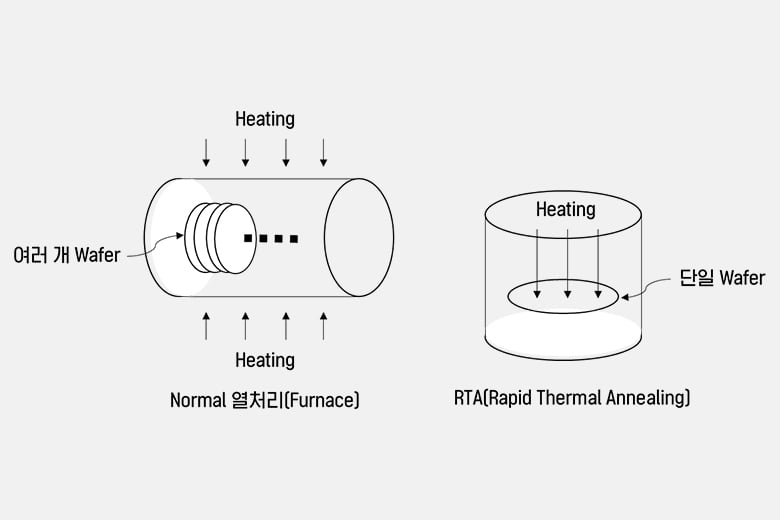

어닐링 방법 비교: 일반 열처리 vs RTA

▲ 어닐링 방법 : 일반 열처리 vs RTA(“NAND Flash 메모리”참조) 방식

고온열처리는 노(Furnace, 퍼니스)에서 진행하는데, 재질의 미세구조를 변화시키는 현상을 이용하는 목적으로는, 상온(실내 온도 25˚C)에서부터 온도를 서서히 상승시켜 가열한 후, 고온을 어느 일정 시간 동안 유지하고 나서 다시 일정 시간에 걸쳐서 온도를 고온에서 상온까지 냉각시킵니다. 그러나 높은 온도인 만큼 도펀트들이 기판(Substrate) 내부로 깊숙이 확산할 수 있기 때문에 시간조절이 중요합니다. 일반 담금질은 주로 서서히 온도를 올렸다가 급속히 냉각시키는 반면, 고온 열처리는 장시간에 걸쳐서 노에 200~300장의 여러 웨이퍼를 넣어 약 1,000˚C까지 온도를 올렸다가 서서히 냉각시키는 방식(동작시간 약 5시간)이 있습니다. 이온-임플란테이션 후에는 도펀트들의 확산을 최소화시킬 목적으로 일반적인 열처리에 비해 온도를 급속히 상승시키고 급속히 냉각시키는 급속 RTA(Rapid Thermal Annealing, 혹은 RTP라고 부르기도 함)방식을 선호합니다. 시간도 짧아서 선호도가 높습니다.

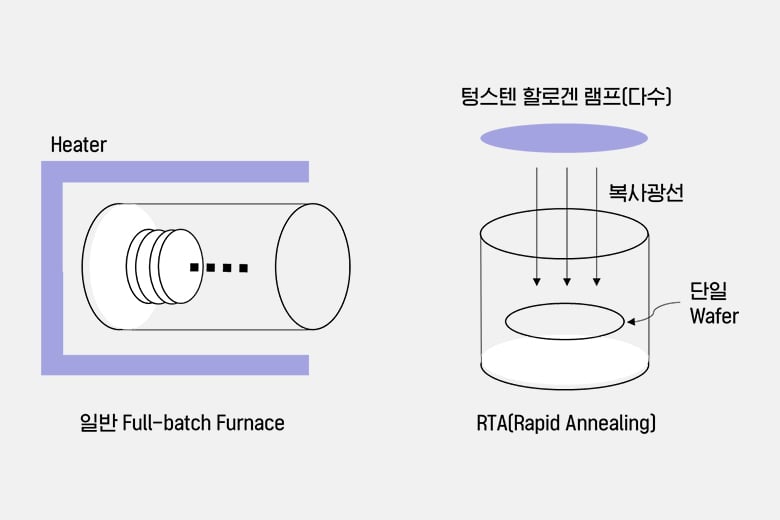

어닐링 장비 비교: Full-batch 타입의 노 vs RTA

▲ Full-batch type의 Furnace를 사용하는 방식과 RTA의 비교

일반적인 열처리를 진행하는 Full-batch type의 노는 히터를 이용해 열에너지를 공급합니다. 반면, RTA는 히터 대신 텅스텐 할로겐 램프로 적외선복사광선을 웨이퍼에 순간공급하여 열에너지를 공급합니다. 노(爐)의 분위기는 오랜 시간 동안 조금씩 온도(1분에 10˚C씩)를 올린 후, 고온의 열을 오래 유지할 수 있어서 수백 장의 웨이퍼를 노에 넣고 진행합니다. 반면, 어닐링은 1초에 100˚C씩 올려가면서 웨이퍼를 1장씩 진행합니다. 이때 가장 중요한 조건으로는 웨이퍼 전체에 온도가 균일하게 유지되어야 한다는 것인데, 이런 특성은 아무래도 노가 RTA보다 유리하겠지요. RTA의 적외선광선 보다는 자외선복사광선을 이용하는 RPP(Rapid Photo-thermal Process)가 보다 발전된 어닐링 장치로 이용되고 있습니다. 혹은 온도 차이로 인한 웨이퍼의 뒤플림을 방지하기 위해 Full batch type의 노 속에 웨이퍼를 1장씩 넣고 웨이퍼를 아래/위로 움직여 열처리를 하는 수직용 퍼니스 어닐링(Vertical Furnace RTA)을 사용하기도 합니다(이런 특별한 경우는 높은 품질을 요구하는 제품인데, 웨이퍼 처리량이 다른 공정에 비하여 최저로, 원가가 높아지는 단점이 있습니다). 그 외에도 퍼니스의 분위기와 웨이퍼 상의 패턴과 박막두께 등이 온도 변수로 작용하여 웨이퍼에 데미지를 줄 수 있습니다. 또한 웨이퍼의 국부적인 변수에 따른 온도를 정확하게 측정하는 기술이 매우 중요한 만큼, 이러한 기능들은 장비의 원가를 높이는 요소이기도 합니다.

어닐링은 완벽한 공정이 아니기 때문에 열에너지로부터 도펀트들의 추가확산을 모두 막을 수는 없습니다. 최소화시키는 작용만을 할 뿐이지요. 급속 어닐링(Rapid Annealing) 방식은 시간적 이득이 있는 반면, 웨이퍼가 장당 장비를 차지하는 면적이 커서 처리량(Throughput)에서 손해를 본답니다. 그러나 1장씩 RTA프로세싱을 진행해도 RTA시간이 워낙 빠르기 때문에 일반적인 열처리에 비해 전체 공정 진행 시의 웨이퍼 처리량은 손해 보지 않습니다. 웨이퍼에 온도가 가해질 때, 엣지 부분(원주)보다 웨이퍼 센터 부분(원심)이 온도가 더 높아 온도 차이에 의해 웨이퍼가 쉽게 뒤틀리거나(Warpage) 단층(Dislocation)이 생깁니다. 이런 현상은 베어(Bare) 실리콘 웨이퍼보다 공정이 진행된 패턴 웨이퍼가 더 취약하지요. 따라서 웨이퍼 상의 온도를 균일하게 유지하기 위해 복사광선 타입을 변경하거나, Full-batch type과 RTA의 복합형을 연구하는 등 개발이 이뤄지고 있습니다.

※ 본 칼럼은 반도체/ICT에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.