이 칼럼 시리즈는 『최리노의 한 권으로 끝내는 반도체 이야기』의 일부를 발췌하여 정리했다. 이 책은 반도체 역사부터 시스템과 소자의 발전까지 폭넓게 다루며 반도체 산업 및 시스템 전반을 소개하고 있다.

반도체는 부품이다. 부품은 그 자체로 쓰이지 못하고 어떤 제품(시스템 혹은 세트) 내에서 사용된다. 시스템이 추구하는 바가 그 부품인 반도체의 탄생과 발전을 가져왔고, 앞으로 나올 새로운 시스템은 반도체의 변화를 요구하고 있다. 본 연재에서는 반도체를 시스템과 연결해 설명하며 과거와 미래, 앞으로의 발전 방향에 관해 7편에 걸쳐 이야기하고자 한다.(필자 주)

지금까지 반도체의 탄생부터 소자의 발전 그리고 컴퓨팅 산업이 앞으로 어떤 방향으로 나아갈 것인지 6편에 걸쳐 살펴봤다. 이번 [반도체의 이해] 마지막 편에서는 다가오는 AI 시대에 반도체 산업은 어떤 방향으로 혁신이 이루어지고 있는지 소개하고자 한다.

모바일의 성장과 SoC의 한계

휴대전화, 디지털 TV 등의 전자제품은 제어 기능을 수행하는 컴퓨터 시스템이 필요하다. 이를 임베디드 시스템(Embedded System)*이라고 하는데, 범용 컴퓨터와는 다른 특정 목적의 컴퓨터 시스템이다. 임베디드 시스템은 반도체 칩으로 연산과 제어를 수행하는데, 단일 칩 시스템(System on Chip, SoC)으로 이루어진 경우가 많다.

* 임베디드 시스템(Embedded System): PC와 달리 미리 정해진 특수한 기능만을 수행하는 내장형 컴퓨팅 시스템. 시스템을 동작시키는 프로그램을 미리 하드웨어에 내장해 제어하는 데, 스마트폰으로 TV를 제어하는 것도 하나의 예이다.

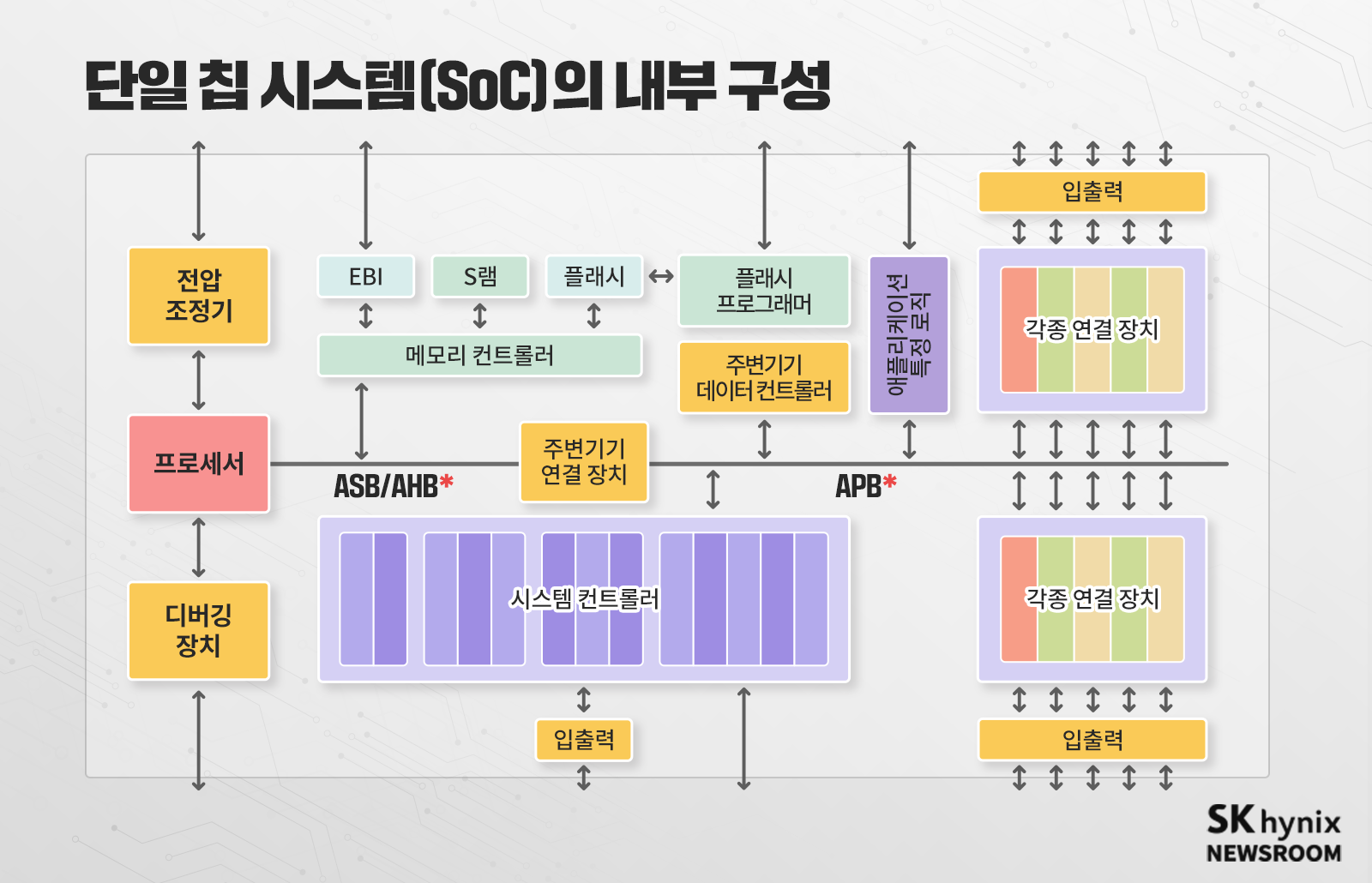

SoC는 여러 기능을 갖춘 블록 기반의 시스템을 하나의 칩으로 만든 것으로, 집적회로에 집약된 컴퓨터나 전자 시스템 부품을 말한다. 이는 CPU, GPU 같은 디지털 신호 처리기, 메모리 블록, 타이밍 발생기, 외부 인터페이스, 아날로그-디지털 변환 회로, 전원 관리 회로 등으로 구조화되어 있다.

* ASB/AHB/APB: SoC 내부 칩의 IP를 어떻게 연결해 데이터를 주고받을 것인가를 약속한 구조를 AMBA(Advanced Microcontroller Bus Architecture)라 한다. AMBA는 3가지 Bus interface로 이뤄진다. ▲ASB(Advanced System Bus)는 프로세서와 메모리 및 고성능 장치를 연결하는 버스 ▲AHB(Advanced High performance Bus)는 ASB 규격보다 더 고성능 프로세서와 메모리를 연결하는 버스 ▲APB(Advanced Peripheral Bus)는 Input/Output 등의 주변 장치를 연결하는 버스로 구성되어 있다.

SoC는 일반적으로 여러 패키지를 조립하는 멀티 칩 시스템보다 소비 전력이 적고 패키지가 단순하며 높은 신뢰성을 갖는다. 그러나 소자 테스트 비용과 초기 개발비가 많이 들어, 생산 물량이 적을 경우 더 비쌀 수밖에 없다.

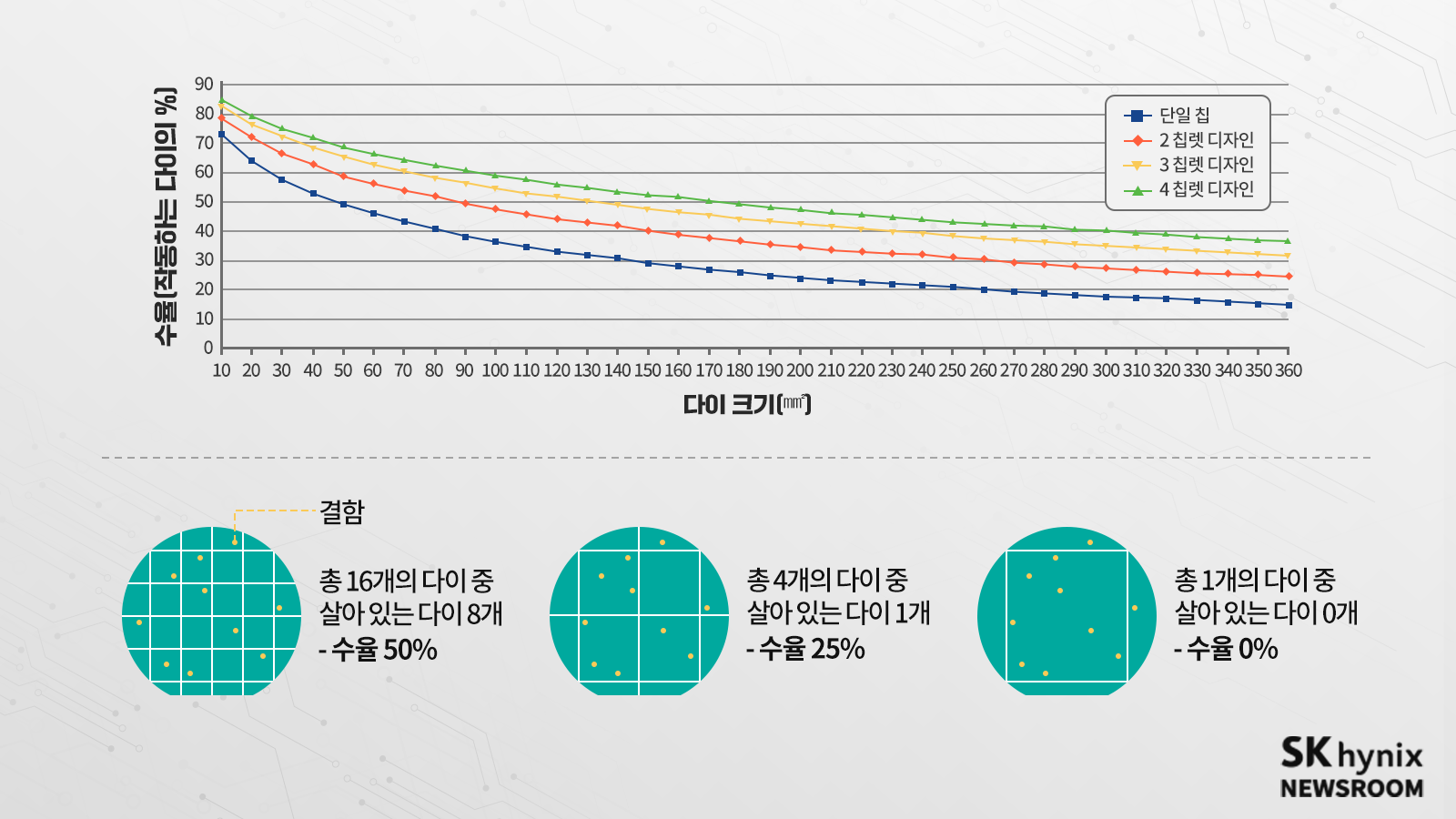

SoC 방식의 또 다른 문제는 칩을 형성하는 다이(Die)*의 크기가 커질 수밖에 없다는 것이다. 땅 넓이를 더 넓히고, 반도체 전공정을 통해 그 안에 모든 기능을 다 넣어서 만들기 때문이다. 반도체 제조에 있어 다이의 크기가 커지면 한 웨이퍼에 만들 수 있는 칩의 수가 줄어 수익성이 떨어진다. 또, 웨이퍼에 동일 수의 제조 결함이 생긴다는 가정하에 정상 작동하는 칩의 수가 현격히 준다. 수율이 감소하는 것이다. 즉, 수율은 다이의 크기에 반비례해 낮아진다.

* 다이(Die): 패키지 작업을 하기 전, 웨이퍼 상태에서 개별적인 패턴이 구현된 집적회로다. 이후 패키징 작업을 진행하거나, 성능/기능을 설명하는 경우에는 칩(Chip)으로 표현된다.

▲ 다이 크기에 따른 수율 변화

시대가 바뀌며 다양한 전자제품이 출현했다. 반도체 소자의 경우 개인용 컴퓨터가 거의 유일한 거대 시장이었던 과거에는 그 종류가 단순했다. 시장 대부분이 CPU와 메모리 소자 정도로 이루어졌다. 그러나 최근 스마트폰과 같은 모바일 통신 시장이 크게 성장하며, 스마트워치 등의 웨어러블 제품과 자율주행 자동차 등도 반도체 소자의 거대 사용처가 됐다.

이에 따라 소자의 종류도 메모리와 로직(CPU, GPU 등) 외에 통신, 전력 관리, 이미지 센서 등으로 다양해졌다. 이러한 시장의 변화는 반도체 생산에도 영향을 주고 있다. 모바일, 웨어러블 기기는 반도체 칩에 배분할 수 있는 면적이 작다. 때문에 공간적 제약 안에 여러 기능을 집어넣고, 성능을 높여야 하는 요구가 커지고 있는데, 이를 해결하기 위한 전통적인 방법 중 하나가 다양한 기능을 작은 면적 안에 집적하는 SoC였다.

그러나 SoC는 반도체 칩 자체로는 면적이 커지면 비용이 급격히 상승한다는 단점이 있다. 모바일에 맞춰 작아졌지만, 더욱 거세지는 미세화 및 고성능 요구를 모두 만족하는 데 어려움이 있는 것이다.

단일 칩의 한계를 극복하는 칩렛 그리고 FOWLP

SoC의 단점을 극복하는 방법으로 제시된 것이 칩렛(Chiplet) 기술이다. 칩렛은 기존 칩에서 필요한 각각의 기능을 분리해 작은 면적의 칩 조각(칩렛)으로 따로 제조한 후, 후공정 기술을 통해 하나의 패키지로 만드는 방식이다. 시스템을 하나의 큰 칩 안에서 만드는 것(SoC)이 아닌, 작은 칩들을 모아서 하나의 패키지로 만드는 것(System-in-Package, SiP)이다. 칩렛을 포함해 로직, 메모리, 센서 등 다양한 종류의 칩을 하나의 패키지 내에 만드는 기술을 통칭해 ‘이종집적(Heterogeneous Integration)’이라고 부른다.

이종집적은 최근 파운드리* 산업의 비즈니스 영역이 넓어지면서 더욱 주목받고 있다. 이전까지 파운드리의 경쟁력은 앞선 기술 노드*를 신속히 개발해 빠른 소자를 만들고 수율을 높여서 고객사인 팹리스*에 칩을 제때 공급하는 것이었다.

그러나 최근 파운드리의 역할은 단순히 칩을 만드는 것을 넘어 다양한 제품에 맞는 시스템 해법을 제공하는 것으로 넓어졌다. 다시 말해, 제품에 따른 제약(최종 크기, 모양, 실제 사양)을 만족하는 패키징된 시스템을 만들어 주는 것으로 진화하고 있다.

이러한 변화를 처음으로 이끈 것은 TSMC였다. TSMC는 2016년 상용화한 InFO WLP(Integrated Fan Out Wafer Level Package) 기술을 바탕으로 애플의 AP(Application Processor)를 단독으로 생산했다. 이종집적 패키징이 파운드리 사업의 강점이 될 수 있다는 것을 보여준 사례다.

* 파운드리(Foundry): 반도체 산업에서 외부 업체가 설계한 반도체 제품을 위탁받아 생산·공급하는 기업

* 기술 노드(Technology Node): 특정 반도체 공정의 기술 수준을 구분하는 용어로, 보통은 ‘구현 가능한 최소 두께의 회로 선폭 기술’을 의미

* 팹리스(Fabless): 반도체 제품을 직접 생산하지 않고 반도체 설계를 전문적으로 하는 기업

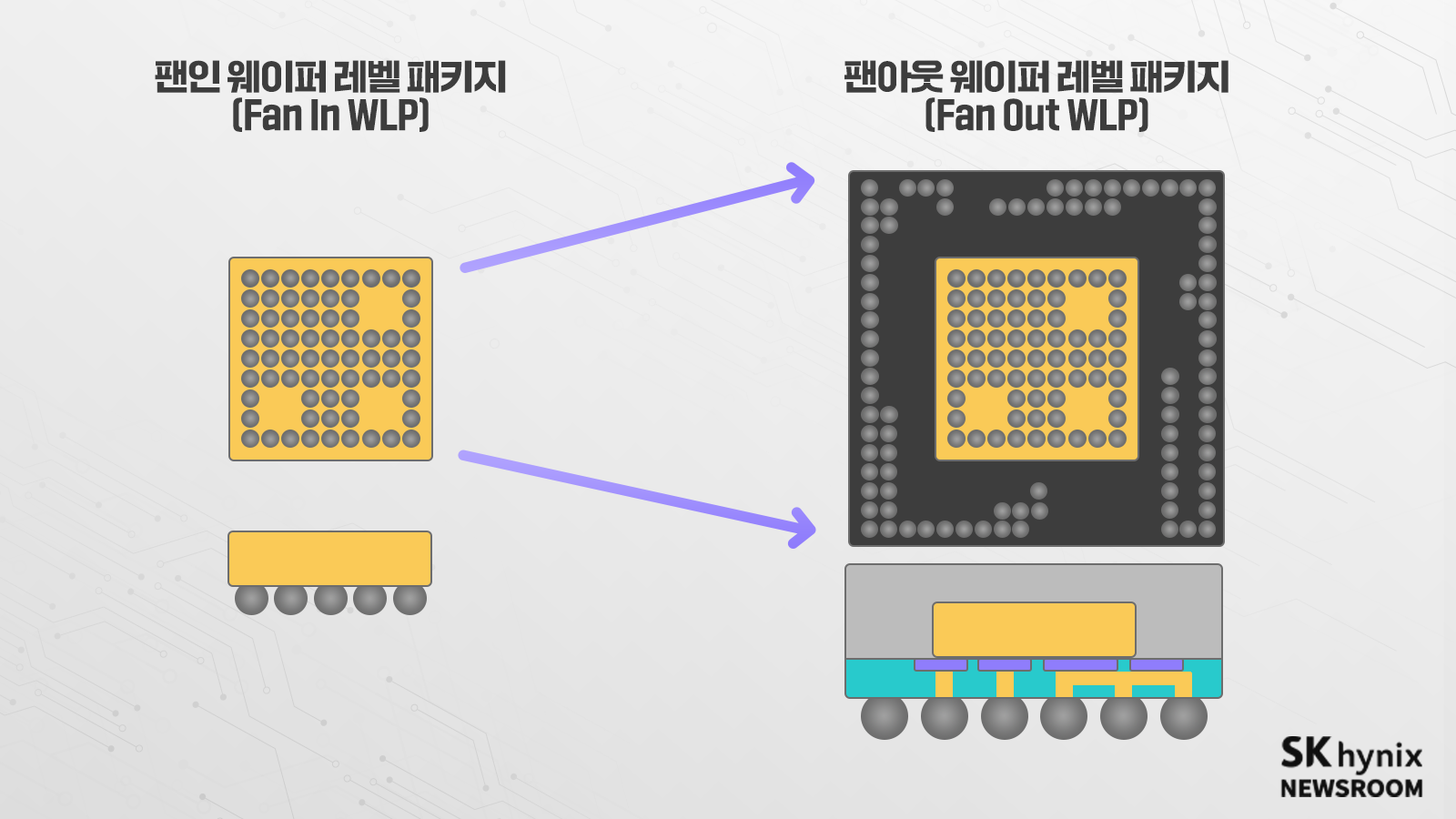

▲ 팬인/팬아웃 웨이퍼 레벨 패키지의 비교

WLP(Wafer Level Package)는 만들어진 웨이퍼를 자르지(Dicing) 않고, 칩 보호 및 방열 역할을 하는 소재로 몰딩(Molding)한 다음, 다이 외부로 전기 신호나 전력를 보내고 받는 배선과 범프(Bump)*를 만드는 패키지 기술이다. 와이어로 신호를 보내지 않아도 되므로 제품의 부피나 두께를 줄일 수 있을 뿐 아니라 증가하는 입출력(Input/Output, I/O) 단자에 대응할 수 있고, 지연 시간도 단축할 수 있는 매우 좋은 방법이다. 또, 패키징 이후 웨이퍼를 자르기에 다이와 패키지의 크기는 동일하게 된다.

반면 범프는 일정량의 금속이 필요하므로 부피와 면적이 클 수밖에 없고, 작은 다이 위에 만들어야 하기에 그 수를 증가하는 데 한계가 있다. 즉, WLP는 I/O 단자가 많아질 수 없어서 칩 간의 대역폭(Bandwidth)이 작다.

* 범프(Bump): 칩(Chip) 회로의 입출력 연결 단자 역할을 하며, 저온에서 녹는 금속으로 만들어진 작은 돌기로, 녹았다가 굳으면서 패키징된 칩을 기판 또는 다른 칩과 전기적으로 연결한다

이와 같이 장단점이 뚜렷한 기존의 WLP를 개량해 단점을 없애고 장점을 극대화한 것이 FOWLP (Fan Out Wafer Level Package) 기술이다. 팬아웃 기술은 I/O 단자 배선을 칩 밖으로 빼는 차세대 패키징 기술이다. 외부에 더 많은 I/O 단자를 배치할 수 있고, 반도체와 메인 기판 사이 배선 길이가 줄어들어 전기적 성능 및 열효율이 높아진다.

대표적인 팬아웃 기술인 TSMC의 InFO*는 다이를 먼저 자른 후 웨이퍼 모양의 틀에 다이를 재배치해 외곽 공간을 확보하고, 몰딩을 진행한 다음 넓어진 면적에 범프를 형성하는 기술이다. 다이에서 범프로 전기 신호를 전달해야 하므로 전기 신호가 갈 수 있는 길은 구리 재배선(ReDistribution Line, RDL)*으로 제조한다. 이렇게 전공정에서 사용하던 것과 비슷한 기술을 활용해 WLP의 작은 두께, 부피의 장점을 살리며 외부로 전기 신호가 나갈 수 있는 길을 많이 만들어 준 것이다.

* InFO(Integrated Fan Out Wafer Level Package): TSMC가 명명한 FOWLP의 기술. RDL 패키징 기법을 적용, 입출력 단자 확대로 칩의 성능/기능을 높였다.

* 재배선(ReDistribution Line, RDL): 웨이퍼 위에 얇은 폴리머층을 깔고 배선을 형성하는 기술. 기판을 쓰지 않아 칩 두께를 줄일 수 있다.

이 패키징 기술로 애플은 얇은 두께와 높은 전기 신호 밀도, 발열 문제를 해결한 최종 반도체 칩을 구현해 아이폰에 적용했다.

InFO 기술의 성공은 파운드리의 사업 영역이 전공정 다이를 생산하여 패키지 회사로 넘기는 것이 아닌 최종 패키지 제품의 문제를 해결해 주는 데까지 넓어졌다는 것을 보여주는 상징적 사건이다. 성능 좋은 반도체 소자를 만들기 위한 기술 노드의 속도가 더뎌지는 상황에서 파운드리 회사의 경쟁력을 나타내는 또 다른 무기가 된 셈이다.

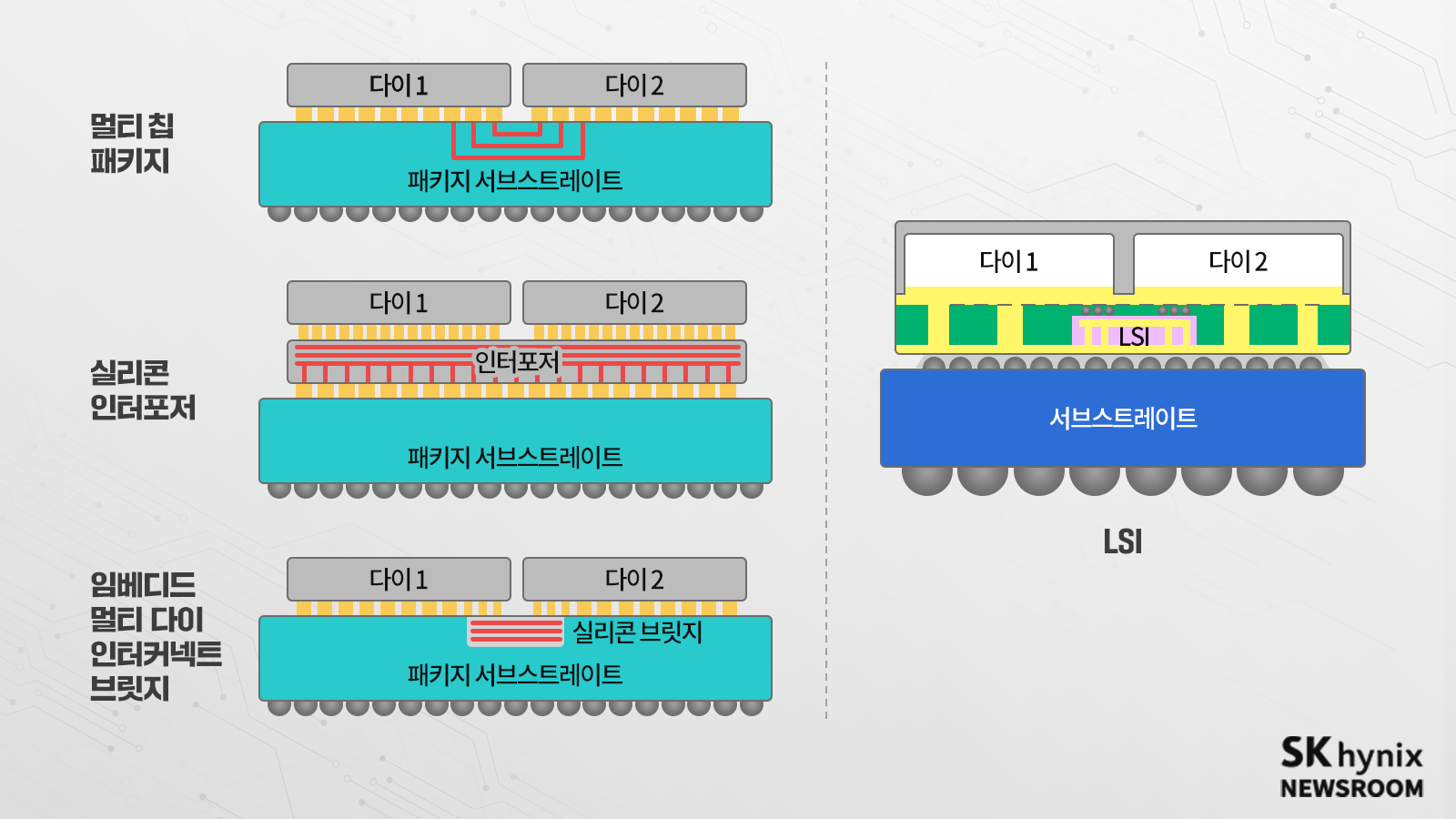

▲ 이종집적 기술의 다양한 예시

현재 이종집적의 경우, 최종 제품에 대한 다양한 고객의 요구를 만족할 수 있는 도구로 많은 후보 기술이 제안되고 있다. ▲2개 이상 다이를 하나의 패키지로 연결한 멀티 칩 패키지 ▲다층 배선의 고분자 기판(Substrate)을 실리콘 기판으로 대체해 여러 개의 다이를 붙이는 실리콘 인터포저(Silicon Interposer)* ▲더 작게 배선된 실리콘 기판을 사용하는 방법인 TSMC의 LSI(Local Silicon Interconnect) ▲인텔의 EMIB(Embedded Multi-die Interconnect Bridge)를 예로 들 수 있다.

* 실리콘 인터포저(Silicon Interposer): 반도체 패키징 기술의 한 부분으로, 고성능 반도체에서 로직 다이와 고대역폭 메모리(HBM)를 연결하는 역할을 한다.

칩렛도 SoC와 같은 하나의 칩으로… 3D SoC

챗GPT로 대표되는 생성형 AI는 반도체 시스템에 또 다른 숙제를 던져줬다. 이와 같은 거대 언어 모델(Large Language Model, LLM)을 다루기 위해서는 엄청난 양의 데이터 학습이 필요하다.

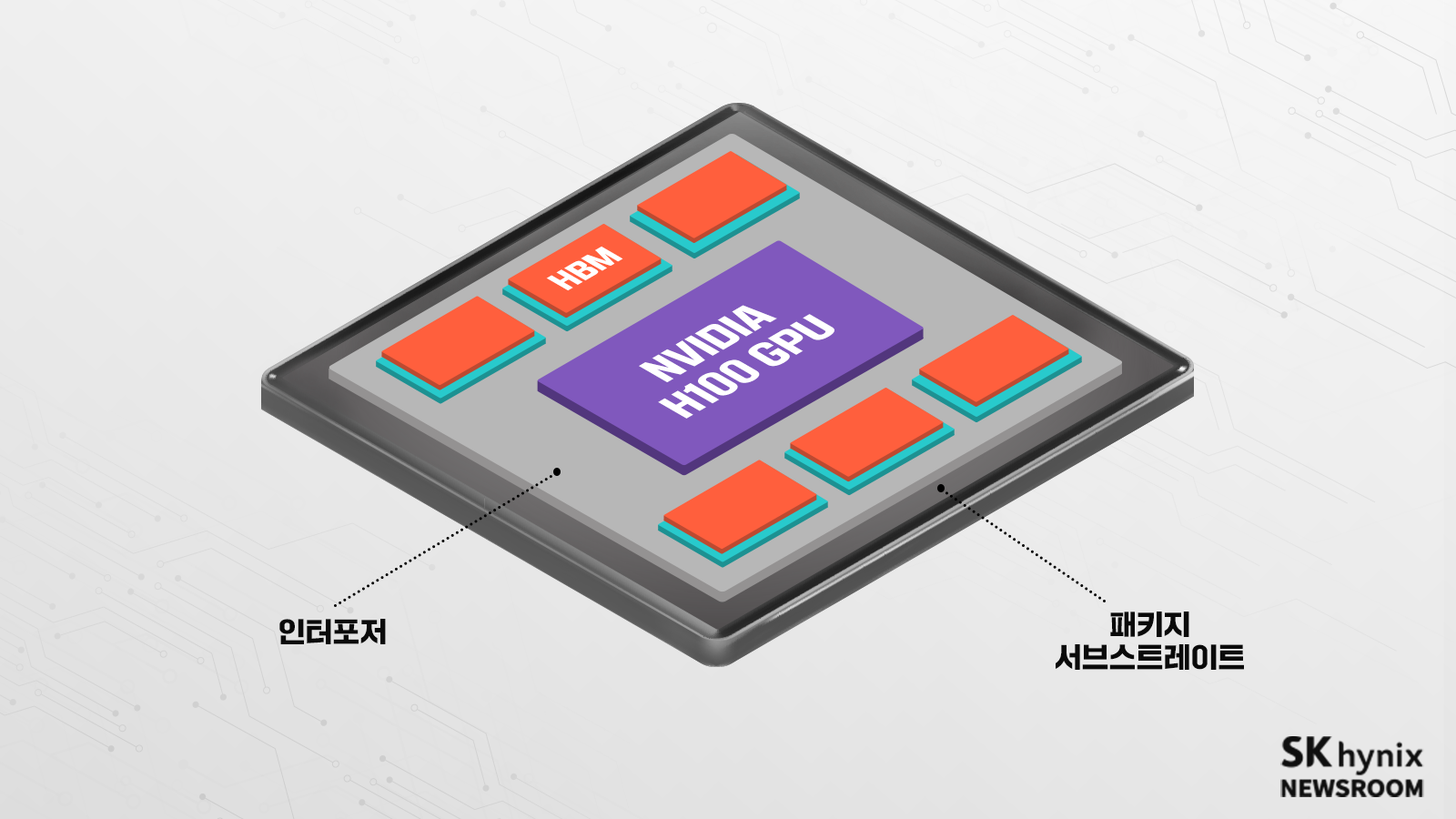

▲ 인터포저를 활용해 GPU와 HBM을 연결한 엔비디아 H100

이를 위해 D램은 대용량 데이터를 큰 대역폭으로 빠르게 GPU에 전달해야 한다. 그래서 D램의 경우, 칩을 쌓고 TSV(Through Silicon Via)로 연결해 대역폭을 늘린 HBM(High Bandwidth Memory)을 사용한다. TSV는 집적회로 칩을 제조하면서 웨이퍼에 구멍을 뚫고 구리 금속 선을 넣어 놓은 뒤 다른 칩 위에 붙이는 공정이다. HBM과 GPU는 큰 대역폭으로 연결하고자 실리콘 인터포저를 이용해 붙인다. 생성형 AI 시대 최대 수혜 제품인 엔비디아(NVIDIA)의 H100은 이와 같은 방법으로 만들어지고 있다.

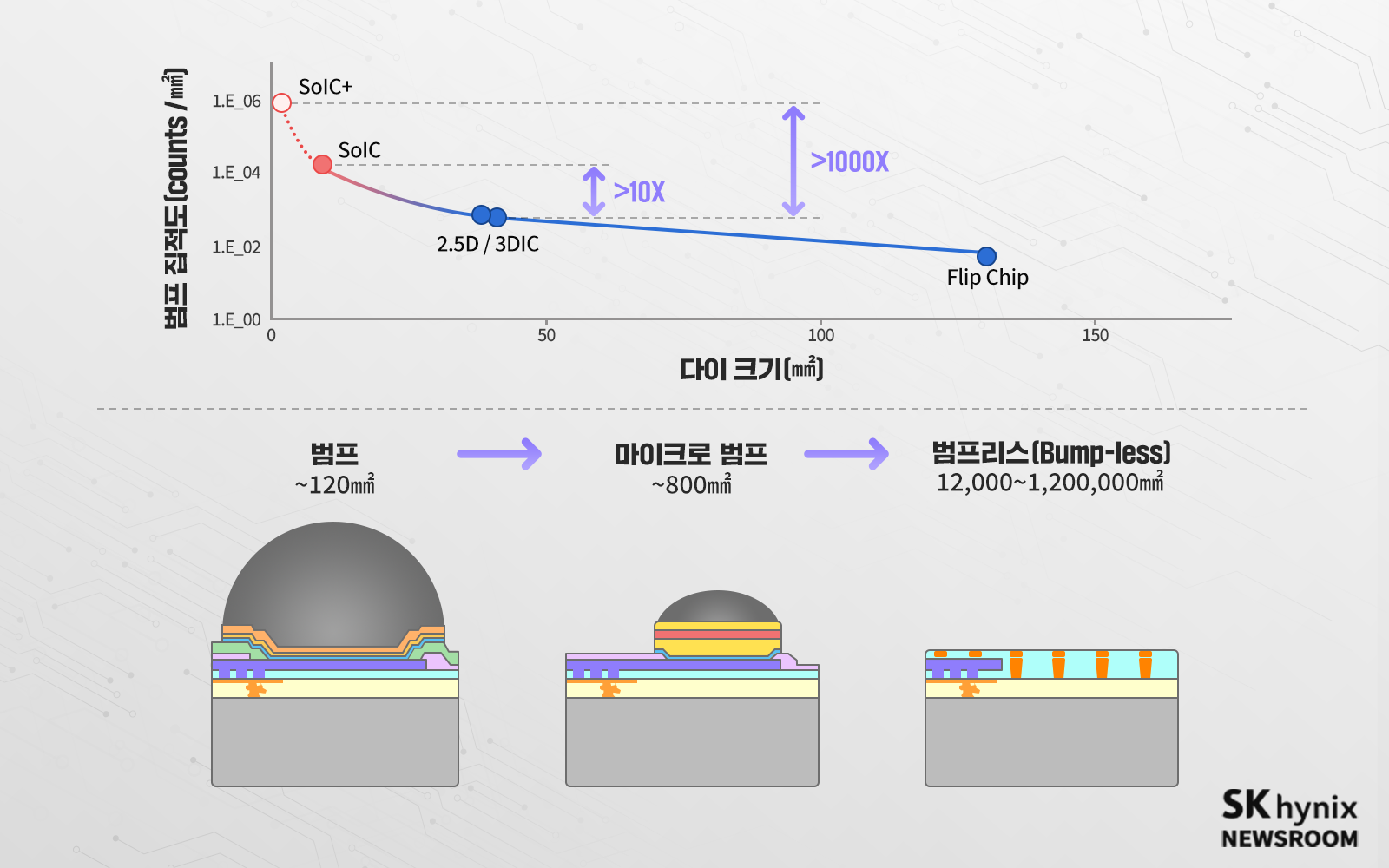

그러나 이러한 칩렛과 같은 후공정 패키지 기술을 통한 결합은 TSV, RDL 등 웨이퍼 레벨에서 진행된 전공정 SoC 방법에 비해 대역폭이 작을 수밖에 없다. 전공정으로 제조한 집적회로는 실리콘(Si) 웨이퍼 내에서 Si를 채널로 이용해 만들어진 한 층의 소자들을 여러 층의 금속 배선으로 연결하는 방법으로 제조되어 왔다. 금속 배선은 포토리소그래피*와 에칭*으로 패터닝*되므로 매우 높은 밀도의 작은 Via*와 배선을 통해 각각의 기능이 연결된다. I/O를 ㎟당 수백만 개 이상 형성할 수 있다. 그러나 후공정 패키지는 각 칩을 연결하기 위한 I/O의 숫자가 ㎟당 수백 개 정도에 불과하다. 결국 적은 수의 I/O는 칩 간 소통하는 대역폭이 작다는 것을 의미한다.

* 포토리소그래피(Photolithography): 빛을 사용해 웨이퍼 위에 적합한 재료의 미세 패턴 박막을 생성하는 기술

* 에칭(Etching): 식각이라고도 하며, 웨이퍼 위에 새겨진 회로 외부의 불필요한 부분을 깎아내는 공정

* 패터닝(Patterning): 박막을 반복적으로 식각하여 집적회로를 구현하는 패턴을 형성하는 것

* Via: 서로 다른 두 개 이상의 금속층을 연결하는 공정

그런데 만약 칩렛의 많은 I/O 단자가 전공정 칩의 구리(Cu) 배선의 밀도와 비슷해진다면 여러 개의 칩렛을 만들어 붙여도 전공정 패키지와 같은 효과를 얻을 수 있을 것이다. 즉, 3D 적층으로 칩렛을 구성하고, 많은 I/O 단자를 이용해 3차원으로 칩(3D SoC)을 만들 수 있다면 반도체 집적 공정의 기존 틀을 바꿔 놓는 거대한 혁명이 될 것이다.

3D SoC 완성의 핵심은 하이브리드 본딩

전기 신호 밀도를 이처럼 높이기 위해서는 두 다이를 잇는 접점의 밀도가 높아야 한다. 그러나 접점으로 사용하는 범프의 면적은 이 목표를 달성하기에는 너무 크다. 기존 범프의 크기를 줄인 마이크로 범프(Micro Bump)도 나왔으나 아직 갈 길이 멀다.

▲ 하이브리드 본딩은 전기 신호 밀도를 크게 올릴 수 있는 기술이다.

그래서 주목을 받는 기술이 하이브리드 본딩(Hybrid Bonding)이다. 이는 범프 없이 구리 배선의 패드끼리 직접 붙이는 기술이다. 다이를 만드는 배선 공정이 마무리되면 표면은 전기 신호가 나오는 구리 패드와 전기가 흐르지 않도록 막는 절연 물질로 구성된다. 붙이고자 하는 다른 다이도 거울로 보는 것과 같이 동일한 구성과 모양일 것이다. 이 두 다이를 절연 물질끼리, 구리 패드끼리 각각 접합하므로, 두 물질을 붙인다 하여 하이브리드 본딩이라 부른다.

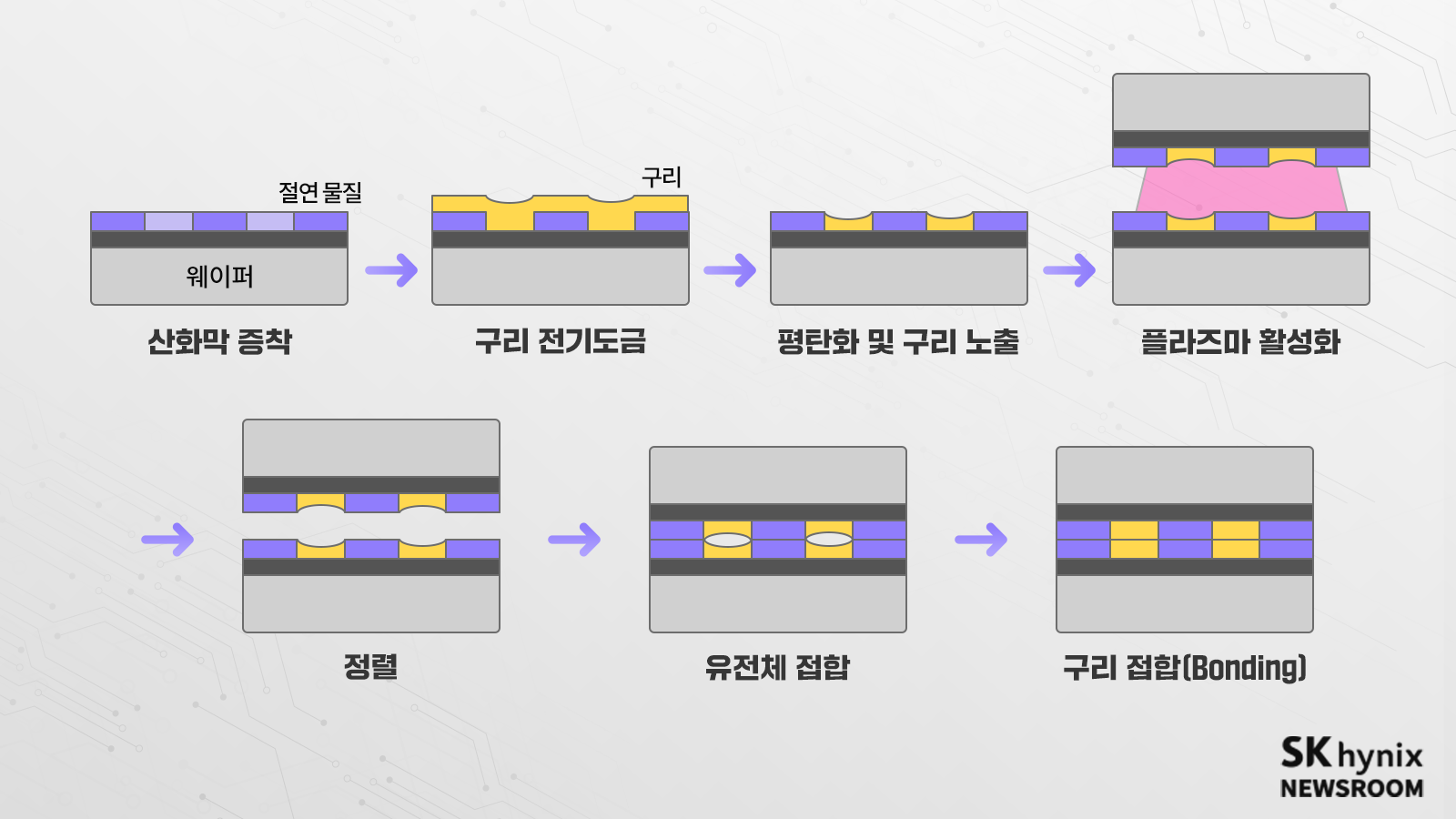

▲ 집트로닉스(Ziptronix)가 개발한 하이브리드 본딩 순서도

이것도 세부적으로는 여러 방법이 제안되었으나, 최근 주목을 받는 것은 집트로닉스*가 공개한 방법이다. 먼저 절연 물질을 플라즈마로 접합이 잘되는 상태로 바꾼 뒤 정렬하여 붙이고, 그 후 온도를 높여서 구리 패드를 붙이는 식이다. 구리의 열팽창률이 절연 물질(SiO2)보다 높은 점을 이용한 것이다.

* 집트로닉스(Ziptronix): SoC 디바이스, 웨이퍼 레벨 3D 적층 공정을 개발하는 미국 벤처 회사

CPU에서 인텔의 경쟁자인 AMD는 2021년 1월 TSMC의 하이브리드 본딩 기술로 S램을 접합한 제품(AMD 3D V-cache)을 만들었다고 발표했다. 다시 파운드리 사업을 시작한 인텔도 2021년 7월 자사 이종집적 기술인 포베로스 다이렉트(Foveros Direct)*를 통해 하이브리드 본딩이 가능하다고 발표했다. 이처럼 하이브리드 본딩은 전기 신호 밀도를 높일 수 있는 궁극의 기술로 치열한 기술 경쟁이 벌어지고 있다.

* 포베로스 다이렉트(Foveros Direct): 인텔의 첫 번째 3D 적층 솔루션 기술로, WLP 수준의 칩렛 패키지를 구현했다.

하이브리드 본딩 방법은 웨이퍼-to-웨이퍼(W2W) 접합, 다이-to-다이(D2D) 또는 다이-to-웨이퍼(D2W) 접합이 있다.

W2W는 HBM이나 플래시 메모리에서 셀(Cell)과 주변회로(Peri.)를 붙이는 것과 같은 메모리 소자 적층에 적용할 수 있다. 이종집적에도 적용할 수 있으나 제약 조건이 있다. 소자 크기가 같아야 하며 수율이 높아야 한다. 수율 낮은 다이를 생산하는 웨이퍼를 W2W로 붙이면, 작동하지 않은 다이가 작동하는 다이까지 영향을 줄 수 있다. 이 경우 최종 제품은 불량품이 되므로 수율은 더욱 떨어진다.

이에 이종집적은 전기적 테스트로 작동하는 다이를 찾은 후 접합하는 D2D 또는 D2W로 구현하는 것이 바람직하다. 장비 측면에서 W2W 접합 장비는 이미 양산 수준의 개발이 이뤄졌고, D2D 또는 D2W 접합은 최근 장비 개발이 시작되고 있다.

이렇게 I/O 밀도가 높은 3D SoC는 파운드리 기업으로부터 만들어지기 시작했다. 필요한 메모리를 받아서 인터포저와 같은 기판에 자신이 만든 로직 칩과 함께 결합하는 것이다. 그런데 바꾸어 생각해 보면 메모리 회사 역시 반대의 형태로 같은 비즈니스를 하는 것이 가능하다. 로직 칩을 파운드리로부터 구매해 자사 메모리와 같이 3D로 집적하는 것이다.

이처럼 3D SoC 시장의 급격한 성장은 메모리, 로직 설계, 반도체 패키징·테스트(Outsourced Semiconductor Assembly and Test, OSAT) 등으로 구분되던 종래 반도체 소자 회사의 비즈니스 영역에 커다란 변화를 불러오고 있다. 새로운 반도체 비즈니스 영역에서 한국 기업들의 선전을 기원한다.

※ 본 칼럼은 반도체에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스 공식 입장과 다를 수 있습니다