반도체를 이해하기 위해서는 산업과 시스템 전체를 바라볼 필요가 있다. 뉴스룸은 지난 20년간 반도체 소자를 연구하고 있는 인하대학교 신소재공학과 최리노 교수를 통해 반도체 시스템과 소자의 관계 및 발전사를 소개한다. 총 7편으로 구성된 이번 시리즈는 반도체의 개념과 앞으로의 발전 방향을 이해하는 데 많은 도움이 될 것이다.

이 칼럼 시리즈는 『최리노의 한 권으로 끝내는 반도체 이야기』의 일부를 발췌하여 정리했다. 이 책은 반도체 역사부터 시스템과 소자의 발전까지 폭넓게 다루며 반도체 산업 및 시스템 전반을 소개하고 있다.

반도체는 부품이다. 부품은 그 자체로 쓰이지 못하고 어떤 제품(시스템 혹은 세트) 내에서 사용된다. 시스템이 추구하는 바가 그 부품인 반도체의 탄생과 발전을 가져왔고, 앞으로 나올 새로운 시스템은 반도체의 변화를 요구하고 있다. 본 연재에서는 반도체를 시스템과 연결해 설명하며 과거와 미래, 앞으로의 발전 방향에 관해 7편에 걸쳐 이야기하고자 한다. (필자 주)

컴퓨터를 만들기 위해 제안된 폰노이만 구조(아키텍처)는 ▲연산과 제어를 담당하는 로직 회로와 ▲데이터와 소프트웨어를 저장하는 메모리로 나뉜다. 1945년 제안된 이 구조로 컴퓨터를 만들기 위해서는 데이터나 소프트웨어를 저장했다가 로직 회로 CPU에 돌려줄 메모리는 단독으로 만들어져야 했다.

지난 편 로직 회로를 살펴본 것에 이어 이번 연재에서는 메모리 반도체의 발전사를 들여다보도록 하겠다.

수은과 자성체’에 데이터 담다, 반도체 소자 이전의 시대

메모리는 정보를 2진수로 바꾸어 0과 1의 상태로 기록해 보관하는 저장 장치다. 두 가지(0 혹은 1) 명확한 상태를 안정적으로 가질 수 있다면 무엇이든 메모리가 될 수 있다. 물의 높낮이, 주판알의 위치 등도 일종의 메모리다. 메모리는 두 가지 안정된 상태를 전기(電氣)적으로 기록하고(Write), 읽을(Read) 수 있어야 한다. 또 필요 없어진 데이터를 지워서(Erase) 다시 사용할 수 있게 만든다면 더욱 좋을 것이다.

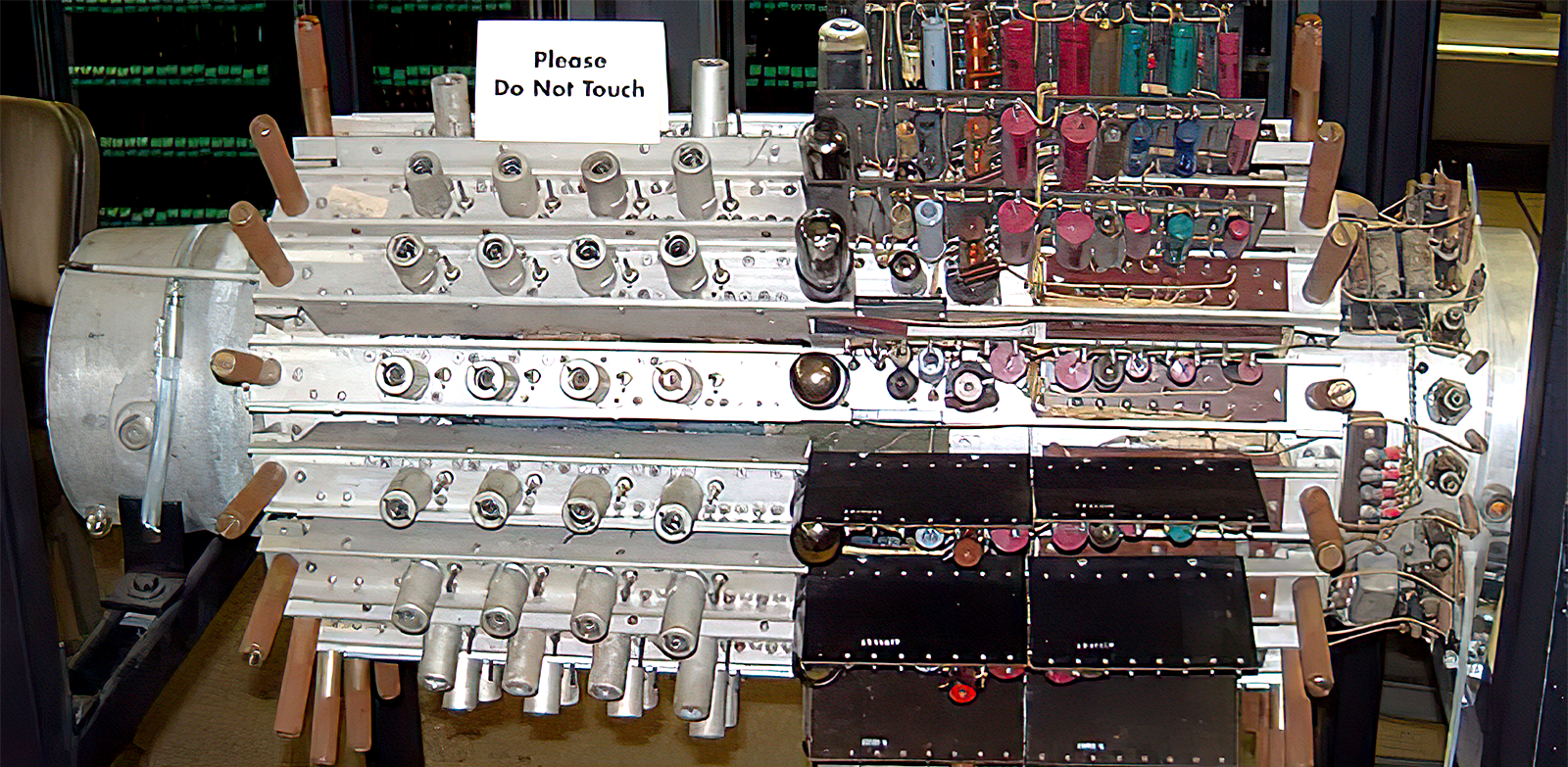

많은 사람이 메모리를 이야기하면 반도체 칩을 생각한다. 그러나 폰노이만 구조가 제안된 1945년은 반도체 소자가 발명되기 전이었다. 로직 회로에서 반도체 소자 이전에 진공관 소자를 사용했듯 메모리에도 반도체 소자가 아닌 다른 소자가 사용됐다. 폰노이만 구조의 초창기 컴퓨터였던 EDSAC(1949년)과 EDVAC(1951년)은 ‘수은 지연 메모리(Mercury Delay Line Memory)’를 사용했다.

▲ 수은 지연 메모리(Mercury Delay Line Memory) 실물 이미지(출처. Wikipedia)

이 메모리는 수은으로 채워진 튜브로 만들어졌다. 튜브의 한끝에 전기 신호를 소리 파장으로 만들 수 있는 변환기(Transducer)를 달아 놓았다. 이것으로 소리 파장을 만들어 수은 안으로 보내는 것이다. 반대쪽 출력 단에도 변환기가 달려 있었다. 그래서 소리 파장이 이곳에 도달하면 파장을 다시 전기 신호로 바꾼다. 이를 다시 입력 단에 넣어주어 계속 회전하는 방식으로 데이터를 저장하는 것이다. 수은 속에서 다른 파형을 가진 일정량의 파장들이 계속 돌고 있는 튜브라고 생각하면 된다. EDSAC과 EDVAC은 각각 512단어와 1,000단어를 기억하는 메모리를 갖고 있었다.

이외에 자성 물질을 이용한 메모리도 사용됐다. ‘자기 드럼 메모리(Magnetic Drum Memory)’는 원통형 드럼에 자기적인 표면을 가진 구조였다. 이 드럼은 고속으로 회전하며 표면에 자기 트랙을 형성했다. 자기적 펄스를 이용해 자기 드럼의 특정 위치를 자화시켜 데이터를 저장했다. 읽을 때는 반대로 그 위치의 자기 신호를 읽어 복원하는 형태였다. 이 메모리는 회전해야 하므로 실행 시간이 길었으며 기계적인 요인으로 소음과 고장이 발생하는 단점이 있었다.

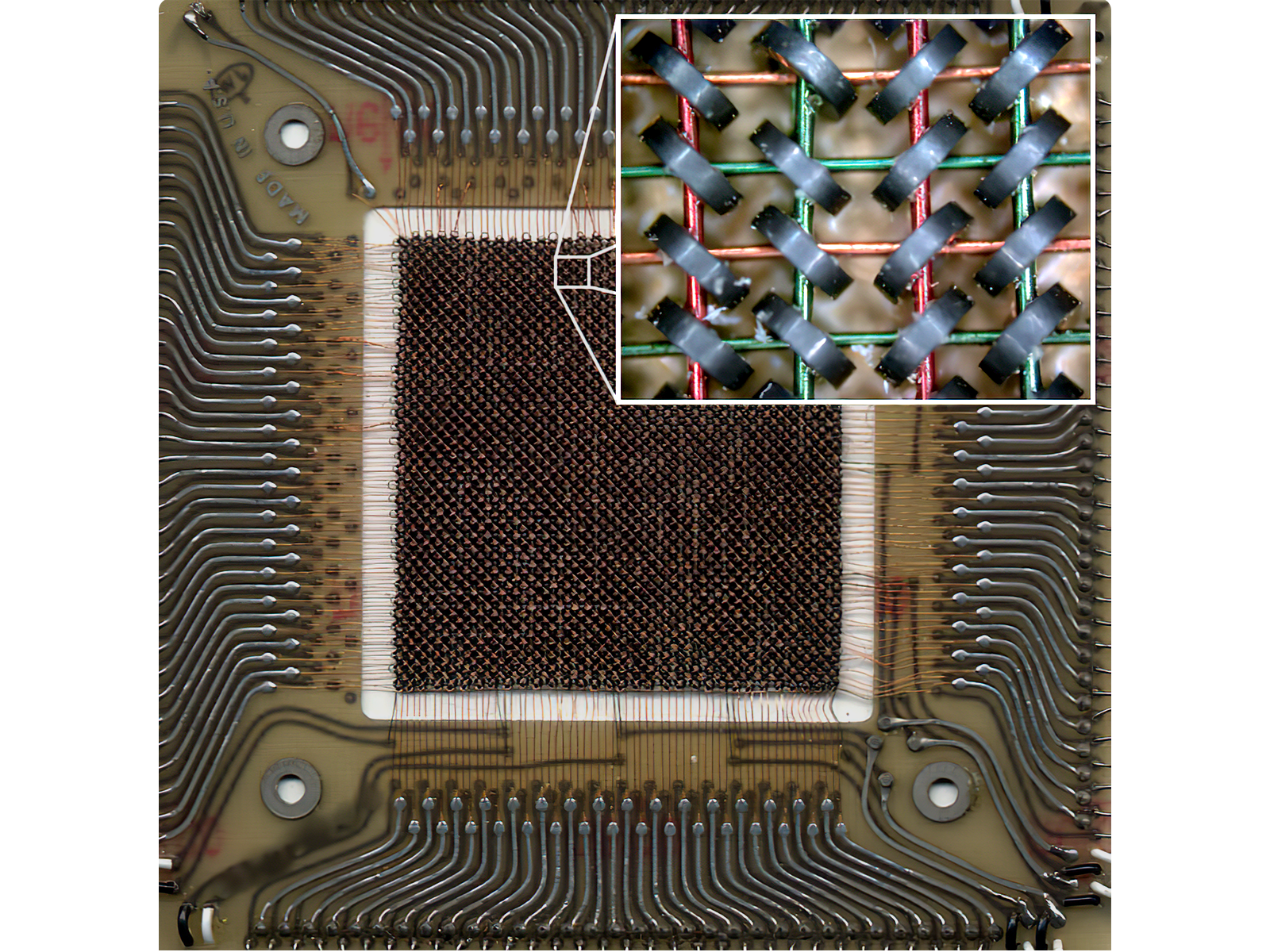

▲ 자기 코어 메모리(Magnetic Core Memory) 실물 이미지(출처. Wikipedia)

이러한 메모리들은 1951년 실용화된 자기 코어 메모리(Magnetic Core Memory)에 밀려 사라지게 된다. 중국계 미국인 안왕(An Wang)은 작은 페라이트(Ferrite)* 자성체로 된 고리에 케이블이 통과하는 모양의 격자 구조를 만들어 메모리로 사용할 수 있게 했다. 이는 데이터 비트를 저장하기 위해 사용되는 행과 열의 격자 구조로 이루어졌는데, 그림과 같이 전기 케이블이 마치 씨줄 · 날줄처럼 엮인 격자의 교차점에 ‘코어’라 불리는 작은 자성 재료를 배치했다. 전기 케이블에 전류를 흘려 자기 유도를 발생시키고, 코어의 자기장을 통해 데이터를 저장했다.

자세히 이야기하자면, 선택된 코어에 전류를 흘려 특정한 방향으로 자기장을 생성해 상태를 변경한다. 이러한 방식으로 코어의 자기장 상태를 변경해 ‘1’ 또는 ‘0’을 표현한다. 데이터를 읽기 위해서는 선택된 코어 주위에 전류를 흘려 현재의 자기장 상태를 감지한다.

자기 코어 메모리는 초기 형태의 램(Random Access Memory, RAM)이라 할 수 있다. 셀의 전압 정보를 읽어오는 데 위치와 관계없이 동일한 시간이 소요됐다.

자기 코어 메모리의 다른 특징은 전기를 차단해도 데이터가 날아가지 않는 비휘발성(Non-Volatile) 메모리였다. 또한, 내구성이 뛰어나고 소비 전력이 적었으며, 자성체 고리 코어를 많이 만들어 넣을수록 용량을 높일 수 있다는 장점이 있었다. 현재의 메모리 반도체와 같이 미세화(스케일링)를 통한 용량 증대도 가능했다. 작고 용량이 커지면 비싸게 팔리므로, 사람들은 자성체 고리를 매우 작게 만들고 많은 수를 집어넣어 용량을 높이려고 노력했다. 이러한 특징으로 자기 코어 메모리는 반도체 소자 메모리가 발명된 이후에도 1970년대까지 가격 경쟁력에서 앞서며 가장 보편적인 메모리로 사용되었다.

반도체 소자 ‘트랜지스터’가 불러온 변화, 캐시 메모리 S램(SRAM)의 탄생

반도체 소자를 사용한 메모리는 1961년 텍사스 인스트루먼츠(Texas Instruments, TI)에서 처음 개발되었다. 냉전 시대였던 1960년대는 군수 산업과 우주 산업이 기술 발전을 이끌고 있었다. 일반 전자 시장에서 팔 수 없을 정도로 가격이 비싼 제품도 기꺼이 구매해 주었으므로 기술의 급격한 발전이 이루어질 수 있었다.

TI는 미 공군에서 사용할 안정된 메모리를 만들기 위해 반도체 소자로 메모리를 개발했다. 이때의 메모리는 바이폴라 접합 트랜지스터(Bipolar Junction Transistor, BJT)를 사용했는데[관련기사], 집적회로 형태로 만들어진 것은 아니었다.

당시 메모리 반도체는 집적회로가 아니었으므로 크기를 작게 하는 데 어려움이 있었고, 또 휘발성(Volatile) 메모리로 비휘발성 제품인 기존 자기 코어 메모리 대비 장점이 없었다. 그래서 처음에는 크게 주목받지 못하다가 집적회로(IC, Integrated Circuit)가 발명되고 소자 미세화가 가능해지면서 다시 주목받았다. 1970년대에 들어서면서 메모리 반도체는 소자 미세화로 고집적화가 이뤄졌고, 가격 경쟁력에서 자기 코어 메모리를 앞서게 된다. 이후는 알다시피 메모리 대부분을 반도체 소자를 이용해 만들게 된다.

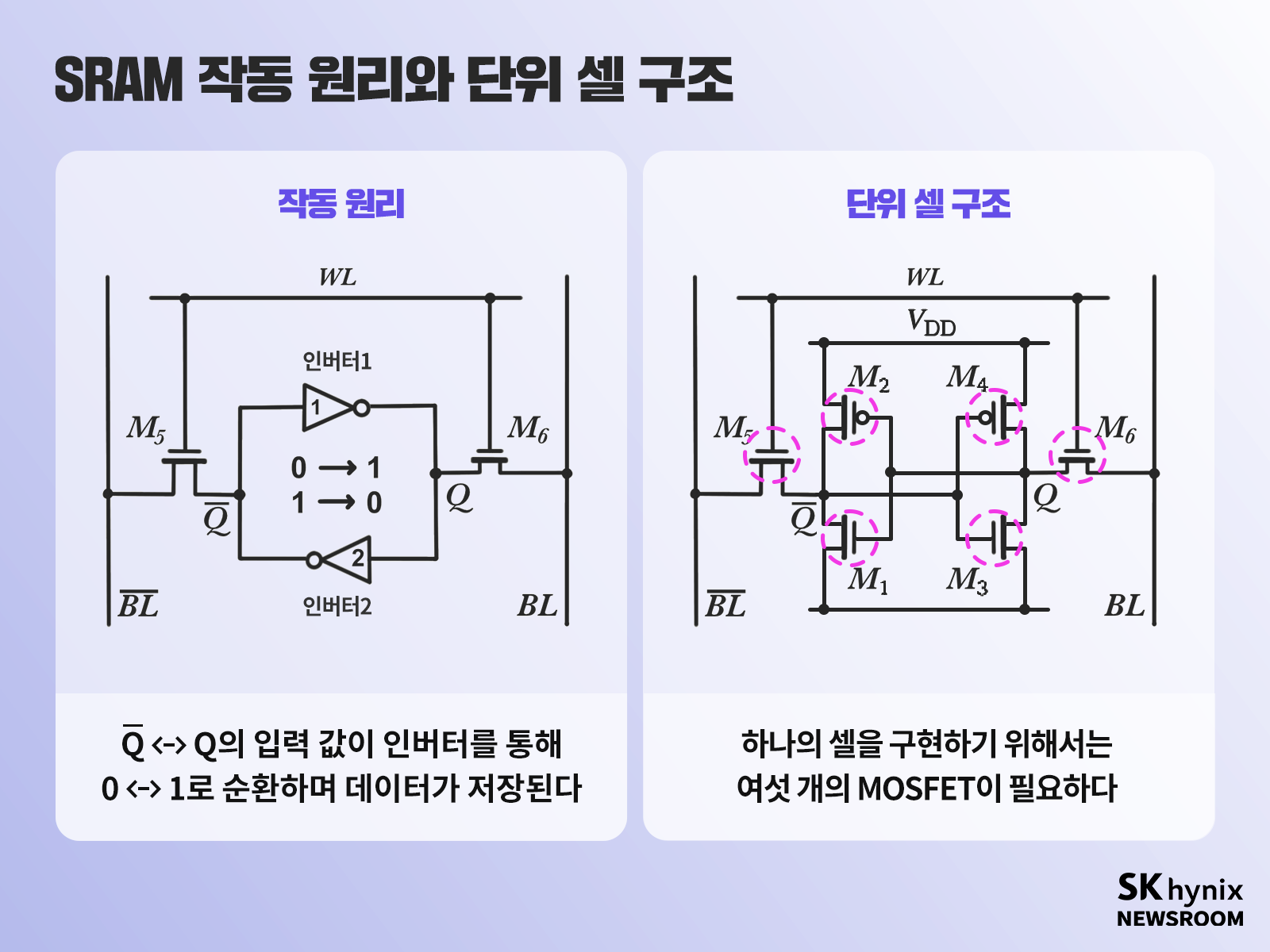

1960년 벨 연구소 강대원 박사가 발명한 MOSFET(Metal Oxide Semiconductor Field Effect Transistor)은 로직 반도체에만 변화를 준 것은 아니다. 이 MOSFET을 사용한 메모리 반도체도 출현했다. 1964년 페어차일드반도체사(Fairchild Semiconductor Inc.)의 존 슈미트(John Schmidt)는 MOSFET 소자로 이루어진 메모리를 처음으로 만든다. 이 메모리는 S램(Static Random Access Memory, SRAM)이었다. S램의 정보 1비트(bit)를 저장하는 최소 단위 셀은 두 개의 인버터 입력과 출력이 서로 연결된 형태로 만들어진다. 인버터는 지난 글에서 소개했듯 0과 1의 신호를 거꾸로 나오게 하는 회로다.

S램의 작동 원리는 다음과 같다. 위 그림 [작동 원리]에서 가 0이면 [인버터1]에 의해 Q는 1이 된다. 그러면 [인버터2]에 의해 는 다시 0이 되어 순환한다. 만약 왼쪽 가 1이면 [인버터1]에 의해 Q는 0이 된다. 그러면 [인버터2]에 의해 는 다시 1이 되어 순환하게 된다. 그렇게 Q가 0이 되는 상태와 1이 되는 상태의 두 가지 안정된 상태를 가질 수 있게 되어 메모리 셀로 사용할 수 있는 것이다.

[단위 셀 구조] 그림에서 셀을 읽을 수 있도록 열어주는 Word Line(M5, M6의 게이트에 연결된 WL)이 선택되면 Bit Line(BL)을 통해 셀에 정보를 쓰거나 읽을 수 있게 되는 것이다. S램은 기본적으로 많은 수의 스위치 소자를 쓸 수밖에 없었다. CMOS로 구현할 경우는 두 개의 인버터를 만드는 데 각각 두 개의 nMOSFET, pMOSFET이 필요하다. 그리고 입구를 막아주는 두 개의 nMOSFET을 합하여 총 여섯 개의 MOSFET이 하나의 단위 셀을 만드는 데 필요했다.

전기적으로 전달되는 신호이므로 메모리를 읽고 쓰는 속도는 전자의 속도만큼 매우 빠르다. 또한, MOSFET으로만 이루어지므로 CMOS 기술로 로직 CPU를 만들면서 다른 공정 없이 동시에 만들 수 있다. 이러한 장점에도 불구하고 S램은 주메모리로 사용되지 않았다. 치명적인 약점이 있기 때문이다. S램의 경우 한 개의 Bit Cell을 만들기 위해 6개의 MOSFET이 필요한데, 이렇게 많은 스위치 소자는 넓은 면적이 필요하다.

또, 인버터를 사용하는 특성상 nMOSFET과 pMOSFET의 문턱전압(Threshold Voltage)* 아래에서 흐르는 작은 전류(Sub Threshold Current)가 Power로부터 두 MOSFET을 거쳐 Ground로 흐른다. 이 때문에 전력 소모가 발생하는데 이로 인해 고정 전력 소실(Static Power Dissipation)이 생긴다. 이 전력 소모는 칩의 온도가 올라갈수록 더욱 커진다. 이러한 면적과 전력 소모의 약점 때문에 S램은 작은 용량이지만 더 빠르게 읽고 쓰기가 필요한 레지스터 파일(Register File)이나 캐시 메모리(Cache)로 한정되어 사용되고 있다.

데이터를 담는 그릇 ‘캐퍼시터’의 등장, 그리고 주메모리 D램(DRAM)의 탄생

주메모리로 사용하기 위해 면적을 줄이고 개발된 제품이 D램(Dynamic RAM, DRAM)이다.

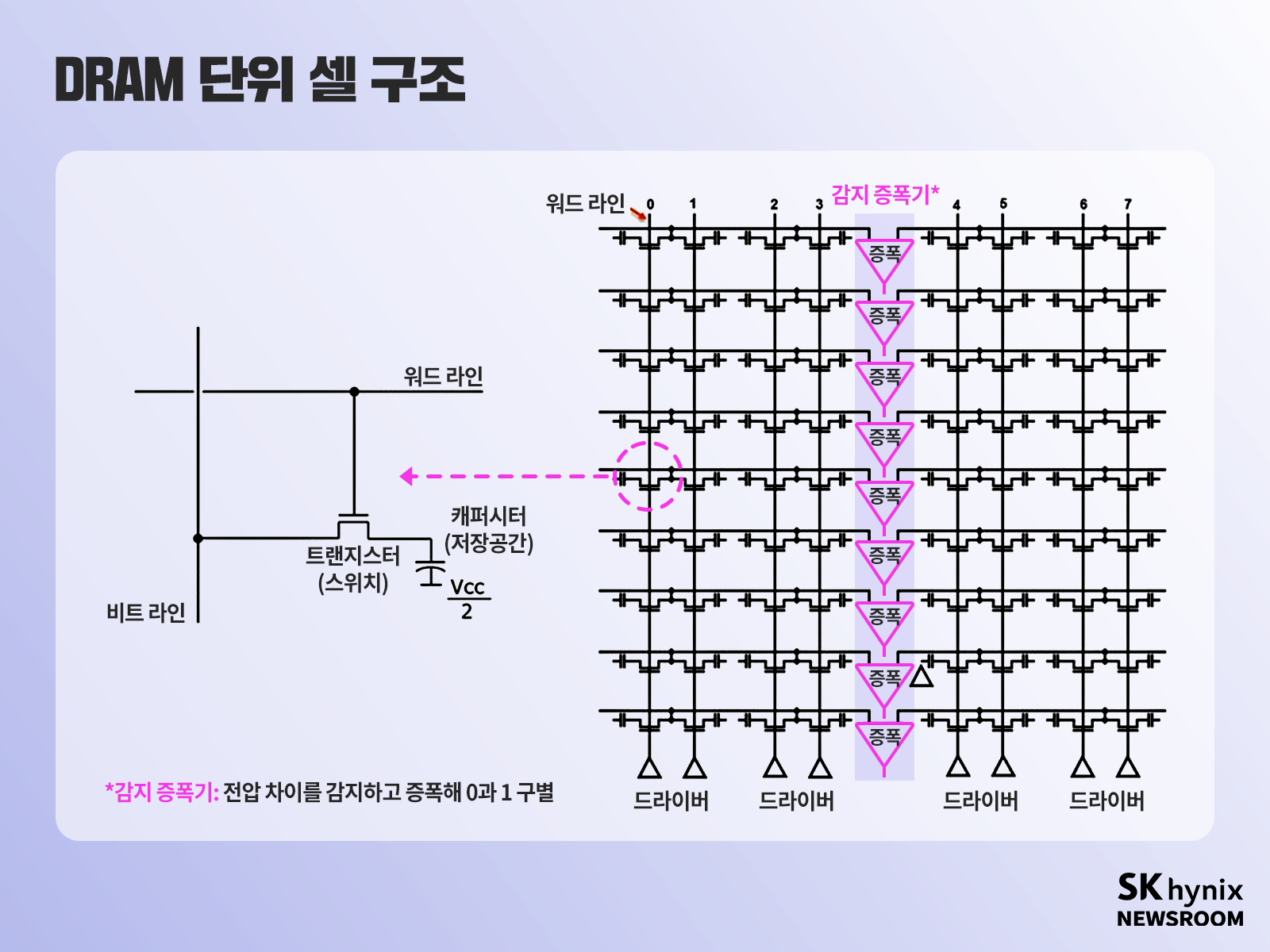

캐퍼시터(Capacitor)에 전하가 채워져 있는지 비어 있는지, 두 상태를 이용해 정보를 저장하는 D램은 그림 왼쪽처럼 한 개의 캐퍼시터와 한 개의 트랜지스터로 단위 셀을 구성한다. 캐퍼시터에 저장된 전하는 차츰 새어나가서 저장된 정보가 없어지는 단점이 있다. 그래서 주기적으로 전하를 보충해 정보가 없어지지 않도록 다시 저장을 해주어야 한다. 이러한 동작을 리프레시(Refresh)라고 한다. S램이나 D램 모두 휘발성 메모리다. 그러나 전기가 들어와 있는 동안은 계속 정보를 유지하고 있는 S램과는 다르게 D램은 계속 주기적으로 리프레시 해주지 않으면 정보가 사라진다. 그래서 다이내믹(Dynamic)이라는 수식어가 붙었다.

이 D램의 특허는 소자 미세화 법칙인 ‘데나드(Dennard)의 법칙’을 만든 IBM의 로버트 데나드(Robert Dennard)에 의해서 1966년 출원됐다. D램은 S램에 비해서 정보를 쓰고 읽는 데 약간 느리지만, 훨씬 단순한 구조여서 같은 면적에 많은 셀을 집어넣을 수 있었다. 이러한 집적도의 장점으로 현재까지도 가장 중요한 메모리로 사용되고 있다.

S램이 주로 캐시로 사용되는 데 반해 D램은 별도의 위치에서 CPU와 통신하는 주메모리 역할을 한다. 빠른 컴퓨터에 대한 요구는 CPU의 속도 증대뿐만 아니라 주메모리 용량의 증대도 요구된다.

메모리 용랑 증대는 온전히 소자 미세화에 의존했다. 반도체 집적 공정 기술의 발전은 놀라울 만큼 엄청난 속도로 메모리 용량을 증대시켰다. D램 역시 셀당 면적을 지속해서 줄이며 용량을 키워갔다. 그러나 셀 면적의 감소는 캐퍼시터의 용량 감소를 동반한다. 물통이 작아지면 그 안에 물이 있는지 없는지를 알기 힘든 것과 같이 캐퍼시터 용량은 일정 수준 이상으로 커야 한다.

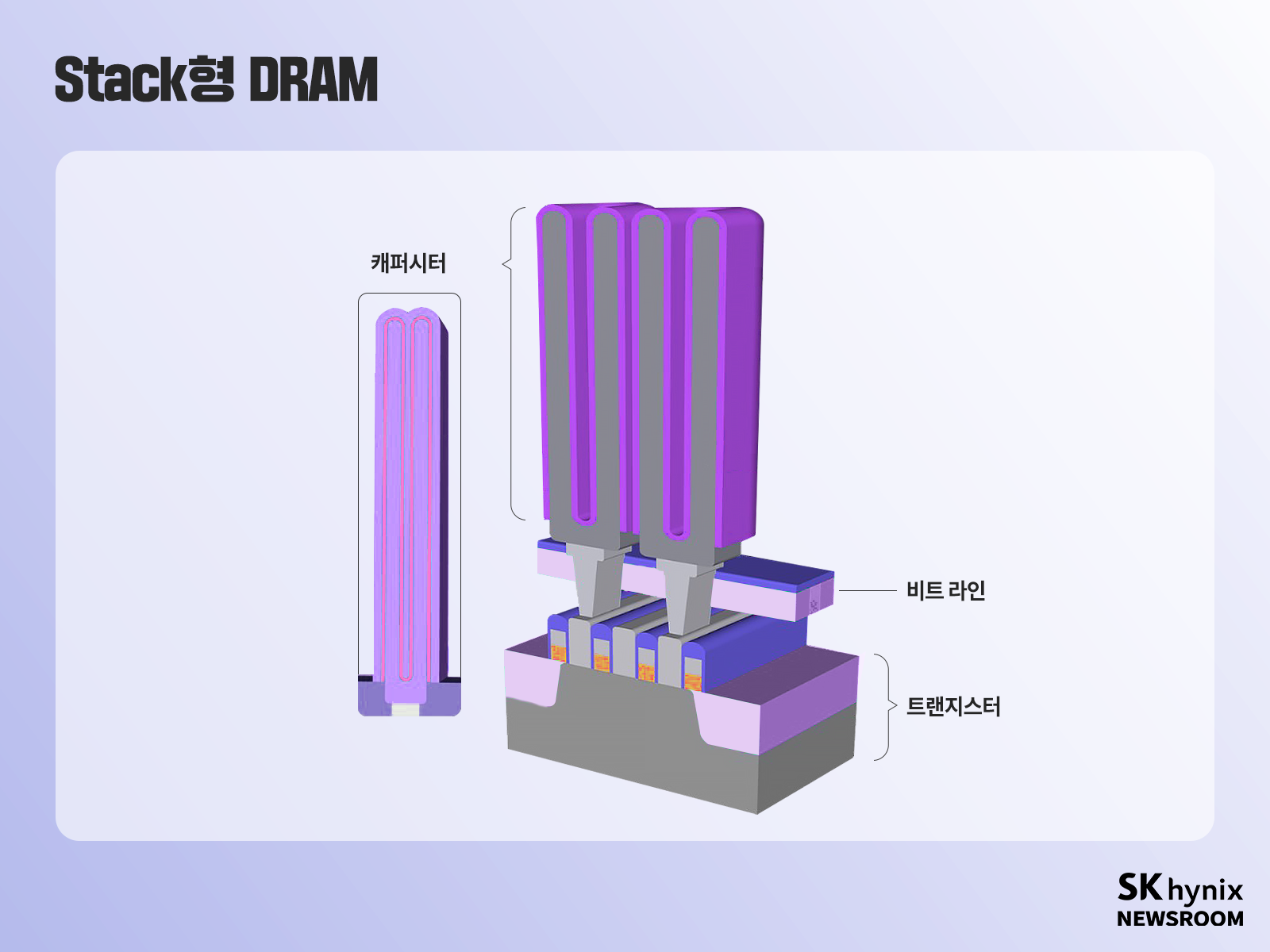

이러한 모순은 점점 커졌고, 1980년대 4M D램을 개발하면서 이를 해결하기 위해 3차원 형태로 캐퍼시터 면적을 넓히는 아이디어가 제시된다. 땅을 파고 들어가는 트렌치(Trench)형 구조와 탑을 쌓는 스택(Stack)형 구조가 그것이다. 많은 D램 기업은 두 아이디어 중 하나를 선택해 개발했고 결국 승자는 추후 스케일링과 불량 검증에 유리한 스택형 구조로 발전했다.

데이터를 붙잡는 Floating Gate의 발견과 비휘발성 플래시 메모리의 탄생

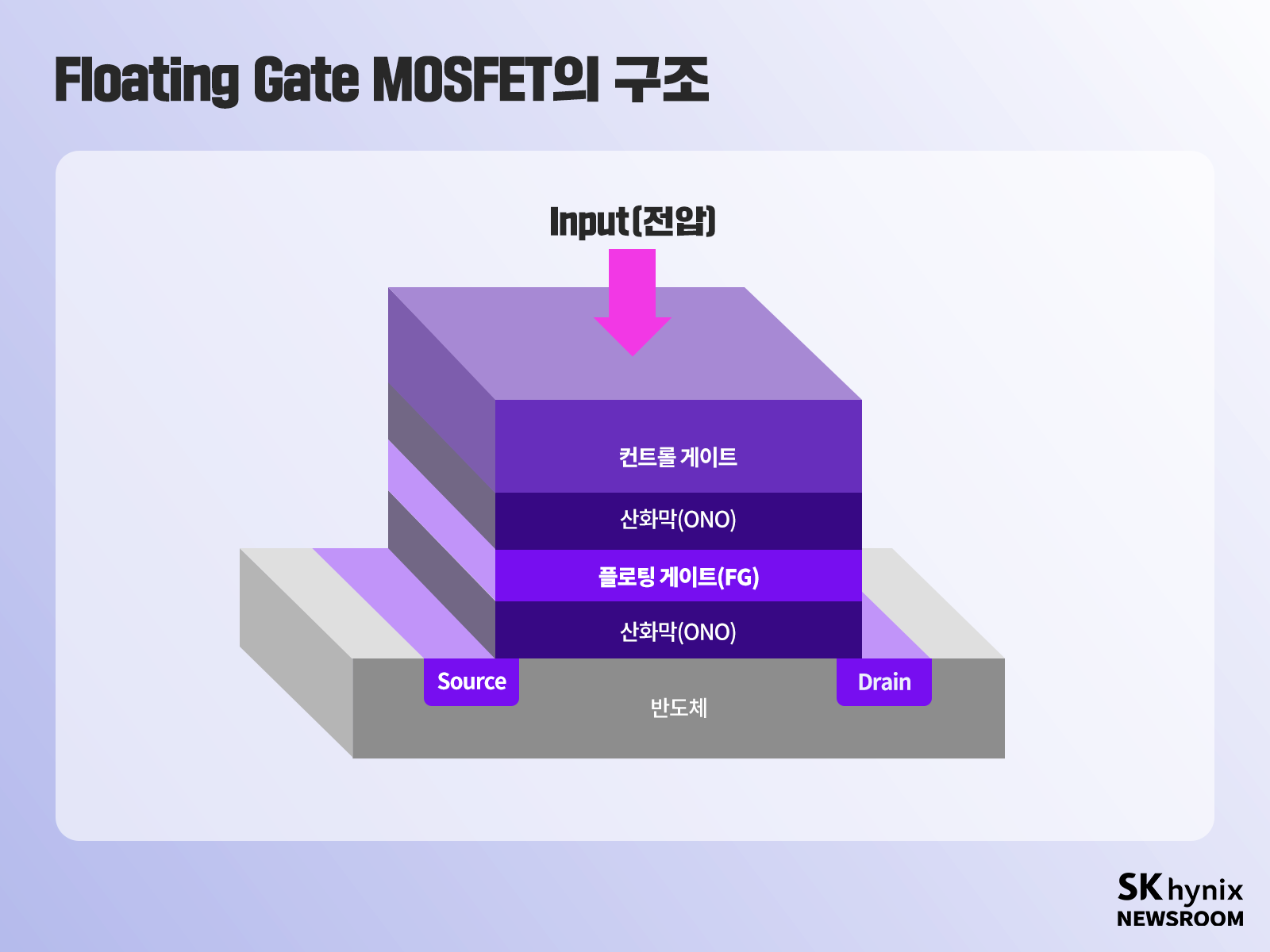

강대원 박사가 이룬 또 하나의 업적인 Floating Gate(이하 플로팅 게이트)* MOSFET도 메모리로 시장에 나온다. 1967년 사이먼 지(Simon M. Sze) 박사와 함께 발명한 플로팅 게이트 MOSFET은 MOSFET 구조에 금속 전극층(Floating Gate)을 한 겹 더 삽입해 넣은 형태다.

위쪽 컨트롤 게이트에 높은 전압을 가하면 채널에 모인 전하 캐리어가 아래쪽 산화막을 뚫고 들어와 플로팅 게이트에 저장된다. 플로팅 게이트에 모인 전하 캐리어의 양에 따라 트랜지스터가 켜지고 꺼지는 기준인 문턱전압이 변한다. 플로팅 게이트에 저장된 전하 캐리어는 전기를 꺼도 산화막의 에너지 베리어(Energy Barrier) 때문에 채널로 돌아가지 못하고 머물러 있으므로 전기가 없는 상태로도 정보를 저장하는 비휘발성(Non-Volatile) 메모리가 되는 것이다.

플로팅 게이트 MOSFET은 EPROM(Erasable Programmable Read-Only Memory)이나 EEPROM(Electrically Erasable Programmable Read-Only Memory) 등과 같이 컴퓨터가 꺼졌을 때도 데이터를 저장하는 매체로 처음 사용되었다. 1980년 일본 도시바에서 이 소자를 응용해 플래시 메모리(Flash Memory)라는 제품을 출시하며 커다란 시장을 형성하게 된다. 이는 같은 셀에 여러 차례 정보를 저장했다가 지웠다 할 수 있는 제품이었다.

플래시 메모리는 읽고 쓰는 데 시간이 오래 걸리는 느린 메모리다. 그러나 비휘발성이면서 MOSFET과 동일하게 생겨 소자 미세화에 가장 유리하여, 매우 싸게 큰 용량을 만들 수 있다는 장점이 있다. 이 플래시 메모리는 2000년대 휴대폰, 디지털카메라 등 다양한 모바일 기기가 나오면서 폭발적인 수요가 생긴다. 요즘은 컴퓨터의 하드디스크 드라이브 대신 사용하는 SSD(Solid State Drive), 이동식 USB 드라이브, SD 카드 등 다양한 곳에 사용되고 있다.

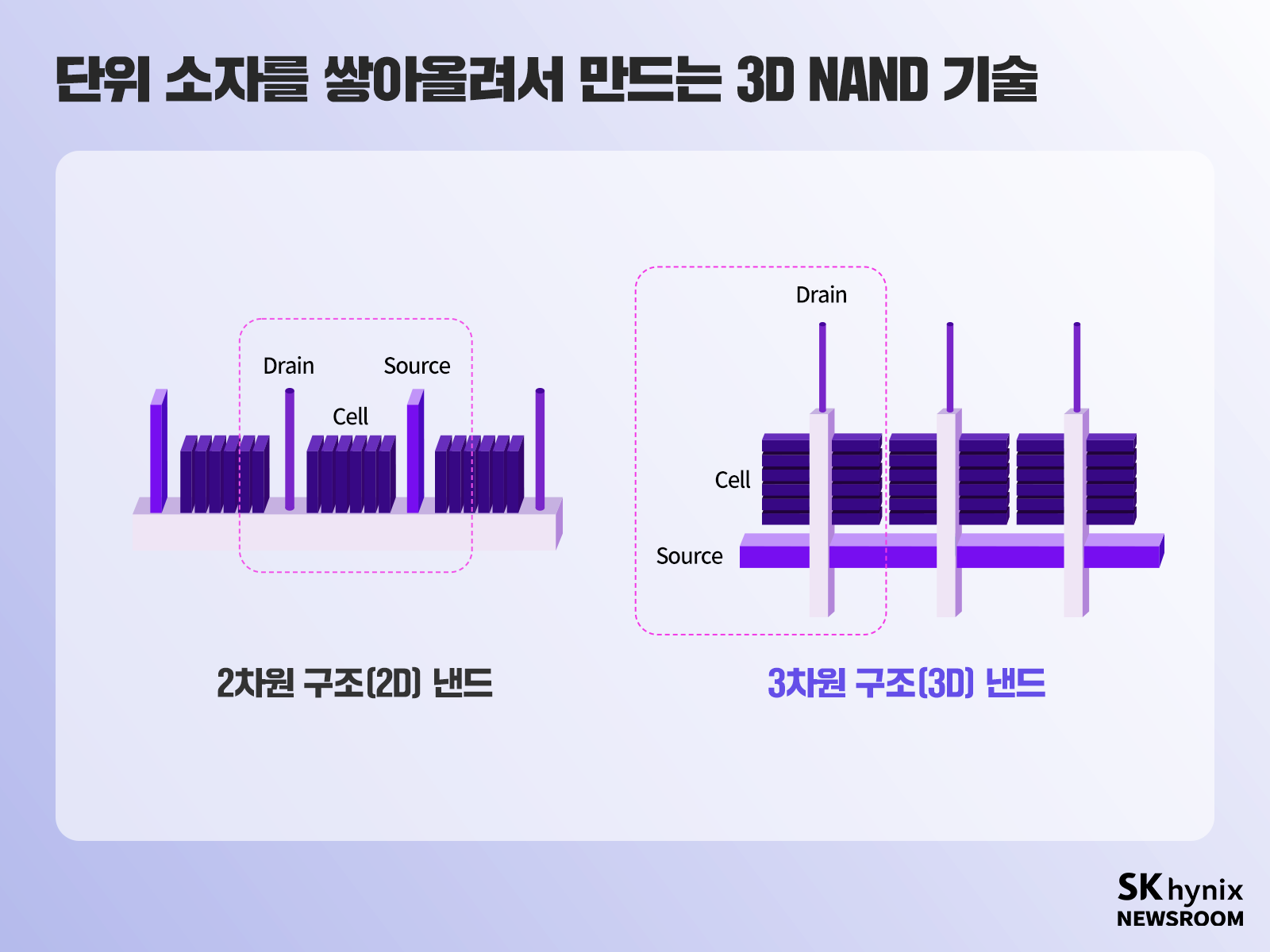

하지만 싼 가격으로 용량을 크게 늘리는 것이 장점인 플래시 메모리는 가장 빠르게 미세화의 한계에 도달하게 된다. 크기가 작아지면서 소자 간의 간섭이 심해진 것이다. 또, 지속하여 미세화하기 위해선 포토 공정의 EUV(Extreme Ultraviolet)* 같은 기술이 적용해야 하고 이 장비는 매우 높은 비용이 요구된다. 이는 가격을 가장 큰 경쟁력으로 삼고 있는 플래시 메모리의 선택지에는 없었다.

그래서 선택한 것이 트랜지스터를 3차원으로 쌓아 올리는 것이었다. 3D 낸드 플래시(NAND Flash)는 현재 200단 이상 적층되며 용량이 늘었고, D램과 함께 메모리 시장의 양대 산맥 중 하나로 중요한 부분을 차지하는 제품이 되었다.

한편, D램과 마찬가지로 현재 플래시 메모리 역시 우리나라 기업이 시장 점유율 절반 이상을 차지하고 있을 만큼 시장을 선도하고 있다. 플로팅 게이트 MOSFET을 계승한 기술, 즉 질화물(Nitride)층을 이용한 차지 트랩 플래시(Charge Trapped Flash, CTF) 메모리* 기술을 비롯해 3D 낸드 기술도 국내에서 최초로 상용화하는 등 플래시 메모리는 우리나라와 인연이 깊은 제품이다.

지금까지 메모리 반도체의 시작부터 현재까지 발전 과정을 살펴봤다. 다음 연재에서는 새로운 메모리의 등장 가능성을 짚어보도록 하겠다.

※ 본 칼럼은 반도체에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.