반도체 기판(Substrate)은 넓은 의미로 웨이퍼를 말합니다. 이 웨이퍼 표면 위로 반도체 회로의 기본 소자인 트랜지스터(Transistor)를 직접 쌓아 올리기도 하고, 새로운 층을 만들어 이를 기판으로 그 위에 소자를 형성하기도 하지요. 특히 통신용, 군사용, 광소자용 등의 특수 용도 트랜지스터나 고성능, 고품질의 트랜지스터는 에피택셜 웨이퍼(Epitaxial Wafer)를 필요로 하는데요. 이번 장에서는 초순수 실리콘으로 형성된 웨이퍼 위에 새롭게 형성되는 극초순수 층, ‘에피택셜 층(Epitaxial Layer)’의 형성 과정과 용도 및 특징에 대해 알아보도록 하겠습니다.

1. 초순수 웨이퍼 위 ‘극초순수’ 층, 에피택셜 층(Epitaxial Layer)

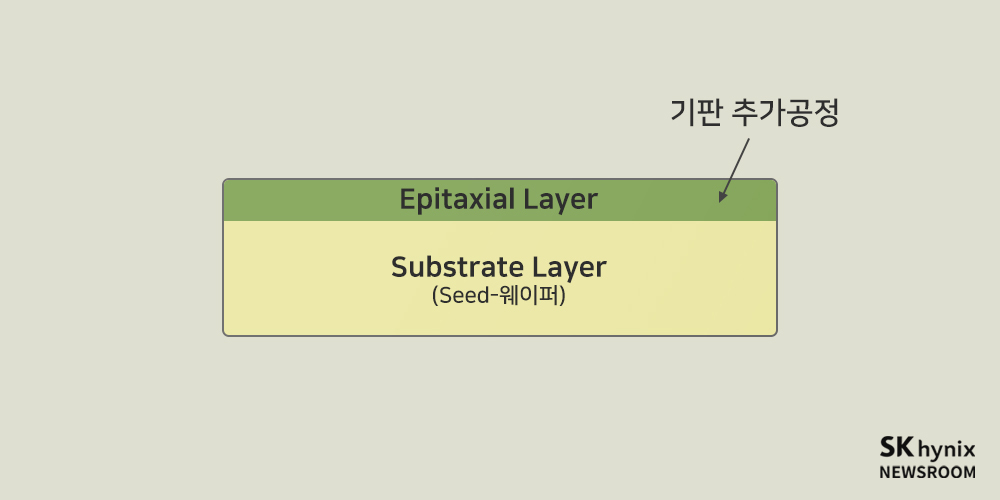

<그림1> 초기 Seed 웨이퍼와 추가 공정을 진행한 에피택셜 층(Epitaxial Layer)

웨이퍼는 반도체 제조공정과 별개로 웨이퍼 제조공정에서 별도로 제작됩니다. 용융시킨 실리콘을 고순도(100%에 가까운) 잉곳(Ingot)으로 뽑아내어 접시 형태로 잘라내면 웨이퍼가 완성되지요. 웨이퍼의 재질로는 집적회로 용도로 가장 많이 쓰이는 실리콘부터 저마늄, 혹은 고속 아날로그 용도의 갈륨비소 등이 사용됩니다.

대부분의 웨이퍼 제조 과정은 공정 조건 및 방식이 조금씩 다를 뿐 큰 흐름은 유사합니다. 반도체 제조에 투입되는 실리콘 웨이퍼의 경우 초순수 웨이퍼, 불순물(P/N Type) 웨이퍼, 공정이 추가된 에피택셜 웨이퍼(Epitaxial Wafer) 등으로 구분되는데, 그중 P-Type으로 도핑된 실리콘 웨이퍼가 가장 보편적으로 사용됩니다. P-Type 기판 위에 간편하게 N-Well(반도체 제조 공정)을 형성하면 곧바로 CMOSFET를 제작할 수 있기 때문이지요. 에피택셜 웨이퍼(에피 웨이퍼)는 주로 순도 높은 초순수 웨이퍼를 Seed(매개체) 삼아 그 위에 추가 공정(Epitaxial Process)을 진행해 만듭니다. ▶<[반도체 특강] CMOS가 정착할 신대륙, 웨이퍼의 종류와 특성> 편 참고

2. 에피택셜 층(Epitaxial Layer)의 조건: 결정질(Crystalline) 구조

<그림2> 에피택셜 막(Epitaxial Layer) vs 비정질 상태의 막

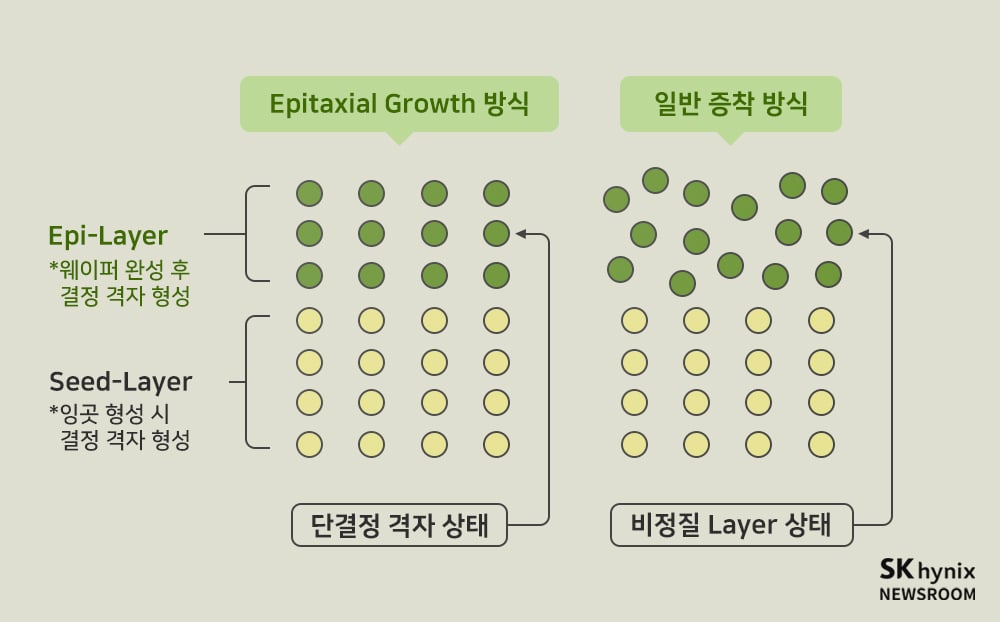

에피(Epi)란 윗 방향으로 더해진다는 뜻이며, 에피택셜(Epitaxial)이란 윗 축의 방향으로 만들어지는 몸체(Layer)를 의미합니다. 에피택셜 그로스(Epitaxial Growth)는 에피택시(Epitaxy) 혹은 별칭으로 에피라고도 부르는데, 이는 Seed 웨이퍼를 밑에 깔고 격자 방향을 유지하면서 단결정(한 종류로 된 결정 전체가 일정한 결정축을 따라 규칙적으로 생성된 고체)으로 성장해 추가로 새로운 층을 쌓아 올린다는 의미입니다.

트랜지스터 구조에서 드레인 전류가 흐르는 통로인 기판은 결정질(Crystalline) 구조를 갖춰야 합니다. 하지만 초창기 반도체 제조공정에서 사용하던 일반적인 증착(Deposition) 방식은 대부분 비결정질(비정질) 막이기 때문에, 비정질을 피하기 위해서는 특별한 조건과 방식으로 에피택셜 층을 성장시켜야 합니다.

Seed-Layer로 사용되기 위해서는 격자(Lattice)의 구성이 결정질이면서, 하부 막의 결정격자구조를 그대로 이어받아 윗 방향으로 성장시켜야 합니다. 따라서 격자들의 정렬 상태가 규칙적이고 격자상수가 일정하거나 혹은 거의 유사한 정도의 막이 필요하지요. 이렇게 Seed-Layer 위에 특별한 방법으로 형성된 새로운 Layer 또는 기판을 에피택셜 층이라 하며, 에피택셜 층을 형성한 웨이퍼를 에피택셜 웨이퍼라고 합니다.

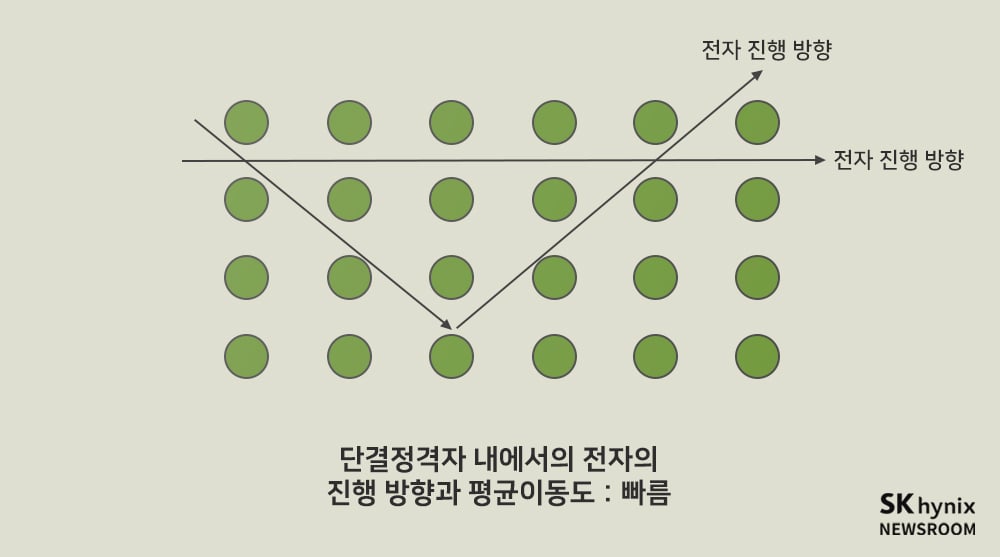

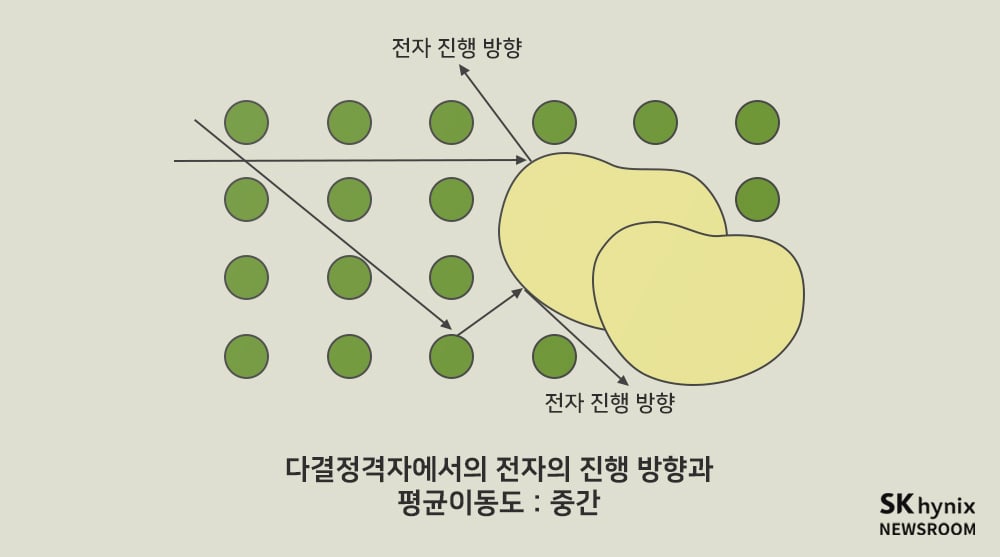

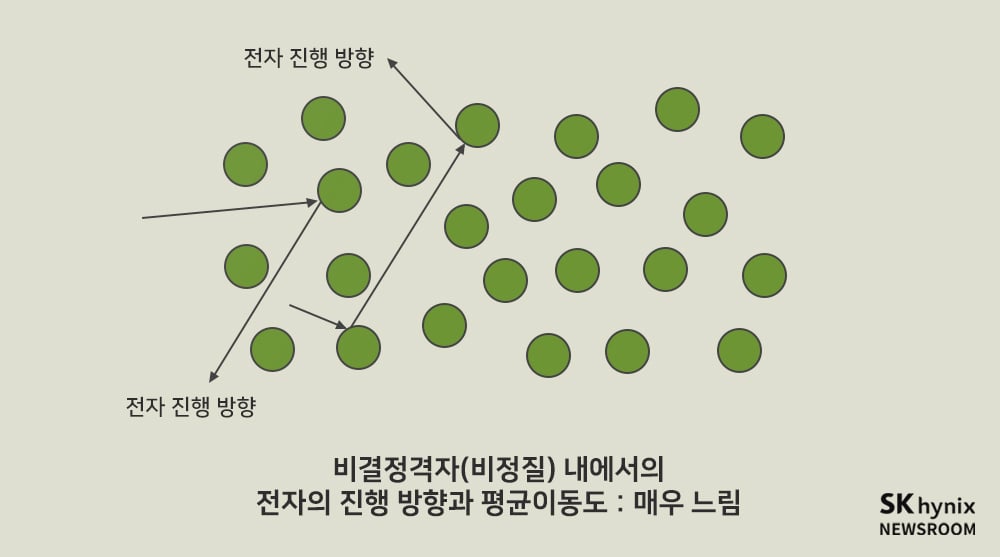

3. 결정격자 내 전자의 이동 조건

<그림3> 전자의 평균이동도 비교 @ 단결정막 > 다결정막 > 비정질막

반도체 소자의 기능은 전자들을 움직이고 그 움직임을 감지해 판단한 결과를 ON/OFF 정보로 사용하는 것입니다. Seed-웨이퍼 위에 추가 공정(극초순수)을 진행하는 이유는, 결함이 없는 막을 마련해 전자들을 무결점 필드(Field)에서 손쉽게 이동시키기 위함입니다.

일정 방향으로 전자의 평균이동도를 높이려면 결정격자가 규칙적으로 배열돼 있어야 하며, 원자들 사이의 거리가 일정하면 더 유리해집니다. 따라서 다결정 혹은 비정질 격자 배열은 전자의 이동도를 약화시키고 전자 Trap(잡힌 전자)을 발생시켜 게이트 전압과 드레인 전류에 대한 예측된 관리를 어렵게 하지요.

4. 결정격자상수(Lattice Constant)

<그림4> 에피택셜 층(Epitaxial Layer)과 단결정 구조의 격자상수

격자상수란 실리콘 원자와 원자 사이에서 결합(공유결합)을 이루고 있는 거리를 의미합니다. 다른 원소가 중간에 들어오면 원자의 전하량이 달라지므로, 원자 간 거리(격자상수)도 달라지지요. 격자상수는 가능한 한 일정하게 유지하는 게 중요합니다. 격자상수가 상이해 위아래층의 열팽창계수에 영향을 끼치면, 웨이퍼의 휨(Warpage) 현상이 발생하기 쉽습니다. 또한, 게이트 산화막인 SiO2 혹은 HfO2를 쌓을 때, 일부 불순한 실리콘 기판보다는 에피택셜 성장을 해 결정격자상수가 통일된 극초순수 층을 기반으로 쌓아 올리는 것이 계면 사이에 끼는 전자 Trap 및 계면 사이의 불일치(접착력 약화 등)를 최소화할 수 있습니다.

에피택셜 층은 품질이 우수한 대신 공정 진행이 어렵고 가격이 비싸 특별한 경우에만 사용됩니다. 특히 에피택셜 프로세스는 단결정으로 성장시켜야 하다 보니 공정 속도가 느리다는 단점이 있습니다.

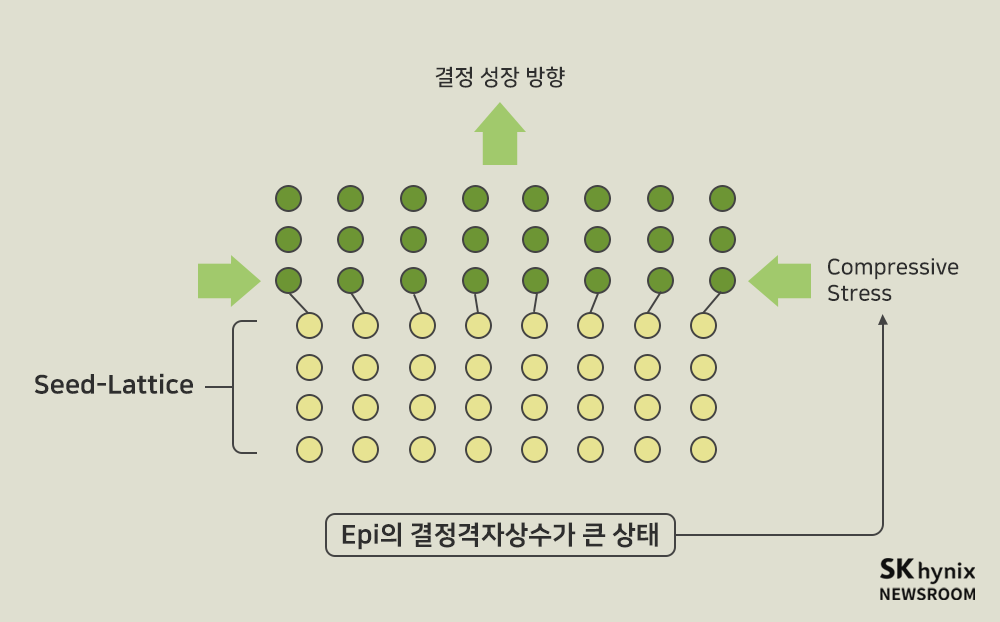

5. 격자정합과 부정합(Lattice Match & Mis-match)

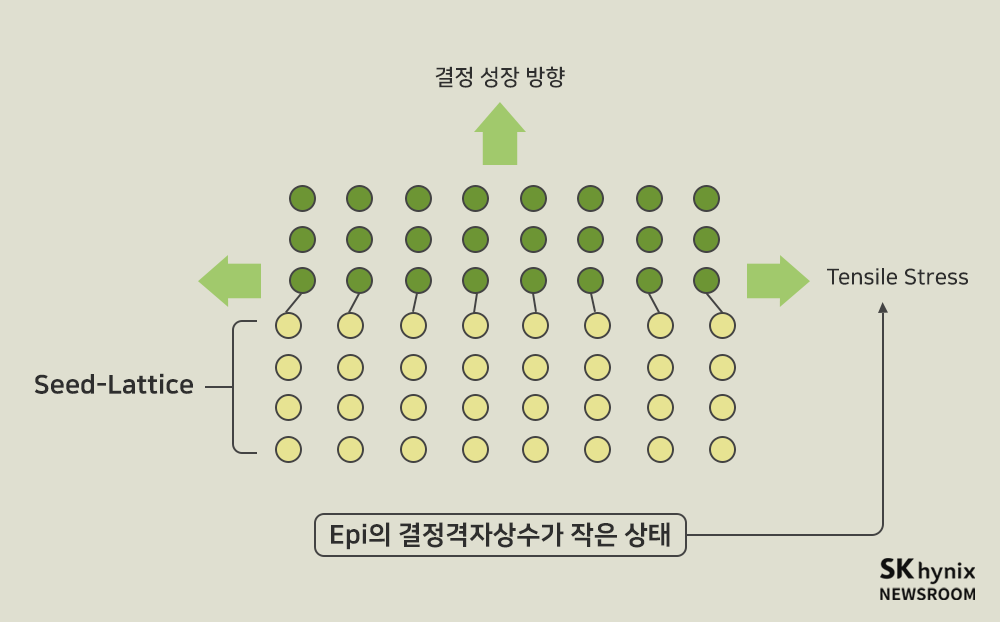

<그림5> 헤테로-에피택시(Herero-Epitaxy)의 두 가지 경우

Seed-Layer와 에피택셜 층의 결정구조 간격이 일치하는 경우를 호모-에피택시(Homo-Epitaxy, 격자정합)라고 하며, 일치하지 않는 경우를 헤테로-에피택시(Hetero-Epitaxy, 격자부정합)라고 합니다. 헤테로-에피택시인 경우, 에피층의 결정격자 간격이 크면 Seed-Layer 간격에 맞추기 위해 압축하려는 압축 스트레스(Compressive Stress)가 가해집니다. 반면, 결정격자 간격이 아래층에 비해 좁을 경우 이를 늘리려는 인장 스트레스(Tensile Stress)가 가해집니다.

원자들이 결합한 형태를 결정구조(혹은 격자)라고 하는데, 결정구조 내 원자들의 거리가 맞지 않는(Mis-Match) 격자가 발생하면 보이드(Void), 힐럭(Hillock) 등의 원치 않는 불량이 발생해 품질 문제가 생깁니다. 이를 극복하기 위해 기판 위에 새로운 에피택셜 기판을 성장시키면, 격자상수(원자 간 거리)가 틀어져 발생하는 위치이탈(Dislocation)이나 전자 Trap 등을 방지할 수 있지요. 이에 더해 에피택셜 층을 형성하는 동시에 도핑을 실시할 경우 원하는 불순물 타입으로 층을 만들 수 있어, 이 층이 반도체 소자를 형성하는 기판으로 활용될 수 있답니다.

※ 본 칼럼은 반도체/ICT에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.