웨이퍼가 발전하면 반도체 제품도 그에 따라 발전합니다. 또 반도체 제품이 진보하면 웨이퍼가 보조를 맞춰 더 나은 웨이퍼로 거듭나지요. 이렇듯 반도체 입장에서 보면 웨이퍼는 항상 새로운 세계입니다. 집을 지을 때 기반공사를 하듯, CMOS를 만들기 위해서도 우선 웨이퍼라는 기판이 마련되어야 합니다. 웨이퍼 제조업체가 반도체 제조업체로 보낸 웨이퍼의 제품 품질에 따라 반도체의 성능이 좌지우지되는 것이죠. 또한, 반도체의 집적도가 높아지면서 연마웨이퍼에서 에피텍셜웨이퍼, SOI웨이퍼 등으로 이동하며 성능 좋은 웨이퍼가 선호되는 추세인데요. 이렇게 여러 웨이퍼의 개발로 선택의 폭이 넓어지고 있는 웨이퍼의 종류와 특성에 대해 알아보겠습니다.

반도체 요구조건을 맞추기 위한 웨이퍼의 다변화

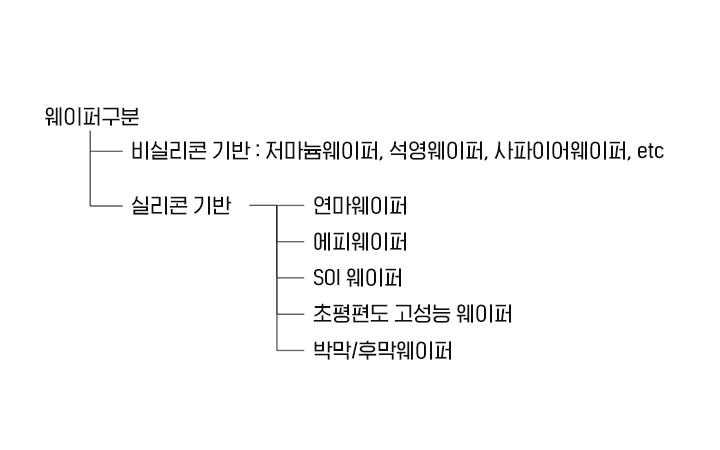

▲ 웨이퍼의 종류 @실리콘 기반, 비실리콘 기반

웨이퍼(Wafer)의 종류는 기반 물질에 따라 여러 가지가 있습니다. 그 중에서도 크게 실리콘 기반의 실리콘 웨이퍼와 비실리콘 웨이퍼로 나뉘는데요. CMOS는 실리콘 기반 물질로 된 웨이퍼가 사용됩니다. 실리콘 웨이퍼를 성능이 낮은 순에서 높은 순으로 보면, 연마(Polished)웨이퍼→에피(Epi)웨이퍼→SOI웨이퍼로 나열할 수 있습니다. 이는 반도체의 다양한 요구를 충족시키기 위함입니다. 이외에도 실리콘 웨이퍼는 형태적, 혹은 기능적으로 종류를 다양하게 나누어 볼 수 있습니다. 그런데 비실리콘 웨이퍼는 이보다도 종류가 훨씬 더 복잡하답니다.

웨이퍼를 쓰임새별로 들여다보면, 프라임(Prime)웨이퍼, 테스트(Test)웨이퍼, 더미(Dummy)웨이퍼, 재생웨이퍼 등이 있는데요. 생산에 실질적으로 투입되는 웨이퍼는 프라임웨이퍼입니다. 또한, 테스트웨이퍼는 프라임웨이퍼를 Fab라인에 투입하기 전에 공정라인의 이상 유무를 미리 점검하는 척후병 역할을 하고, 더미웨이퍼는 공정에 프라임웨이퍼와 같이 투입되기는 하지만 총알받이처럼 프라임웨이퍼를 보호하다가 버려지는 불쌍한 존재랍니다.

연마웨이퍼, 첫 번째 터 닦기

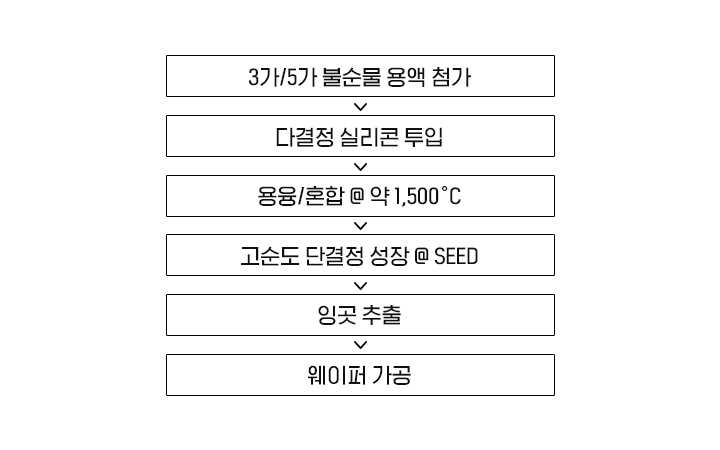

▲ 투입 원료 입장에서 본 연마웨이퍼의 제조 흐름

실리콘웨이퍼 중 가장 보편적으로 사용하는 것은 연마웨이퍼(Polished Wafer)입니다. 이것을 만들기 위해 처음에는 고순도 다결정 실리콘(Poly Silicon) 덩어리와 3가 혹은 5가 도펀트(불순물 첨가제) 원료를 도가니에 함께 넣습니다. 다결정 실리콘은 고순도 단결정 실리콘을 얻기 위한 원료로 사용됩니다. 그런 다음 온도를 약 섭씨 1,500도 가까이 높여 용융시킨 후, 단결정(Single Crystal) 실리콘으로 형성되는 잉곳(p/n_type 불순물 반도체)으로 뽑아내어 전기전도도를 높입니다. 반도체 제조업체들은 n_type 웨이퍼보다는 p_type 웨이퍼를 많이 사용하고 있습니다.

연마웨이퍼는 반도체에 CMOS란 집을 지을 수 있도록 첫 번째 터(Substrate)를 닦아 놓았다고 볼 수 있습니다. 완성된 연마 웨이퍼는 한 쪽 면 만을 연마한 것과 양면을 연마한 것으로 나뉘는데, 직경12인치 이상부터는 단면 보다는 양면 연마웨이퍼가 주로 쓰이고 있습니다. 이렇게 생산된 연마웨이퍼를 기준으로 성능이 좀 더 뛰어난 파생웨이퍼(에피나 SOI 등등)들이 만들어지게 된답니다.

실리콘 결정격자 방향의 일체화

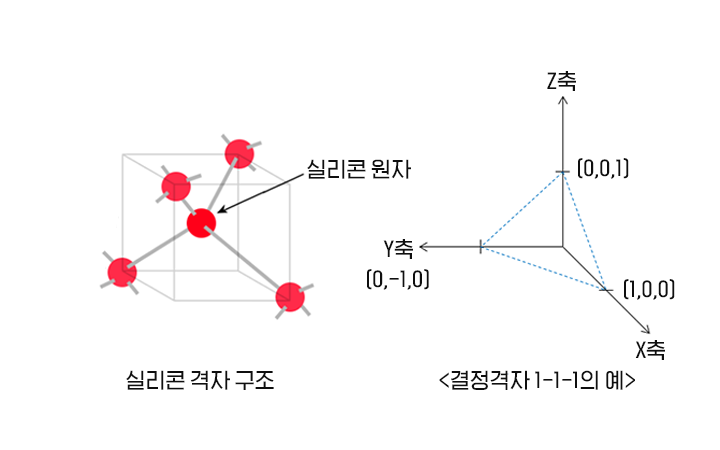

▲ 실리콘 원자구조와 결정격자 @y축 격자방향으로 –1인 경우의 예

잉곳을 만드는 과정에서는 원자와 원자가 연결된 결정격자의 성장방향도 일률적이어야 합니다. 실리콘의 결정격자방향은 용융된 실리콘에서 잉곳을 끌어올리는 부모격인 Seed의 결정격자방향을 따라서 자식격인 실리콘 격자(액체 상태에서 고체 상태로)들이 같은 방향으로 줄을 서게 되면서 결정됩니다.

실리콘 원자 구조는 내부적으로 정육면체의 8개 코너 중 4개 코너에 점유한 실리콘 원자와, 중심에 위치한 원자들 간에 공유결합한 격자형태(반도체 특강 반도체 속의 전자여행 편 참조)로 존재합니다. 결정격자방향은 웨이퍼의 표면이 어떤 형태로 격자를 끊어 내느냐에 따라 달라지지요. 임플란트 공정이나 확산공정 시 불순물 원소를 웨이퍼 표면에서 하부로 침투시킬 때, 원자핵들의 구조적인 위치(격자의 형태)에 따라 침투하는 불순물 원소들의 이동도와 깊이가 달라지겠지요. 즉 불순물 원자가 웨이퍼 속으로 들어가기 위해 웨이퍼를 들여다보았을 때, 결정격자방향에 따라서 실리콘 원자핵이 많기도 하고 적기도 하지요. 그러면 당연히 도펀트가 실리콘 원자핵에 충돌하는 횟수에 영향을 끼칩니다.

물리적으로 웨이퍼가 쉽게 깨지는 것 역시 격자 형태에 따라 달라집니다. 바위나 유리가 결에 따라 쪼개지는 것과 유사한 경우이지요. 웨이퍼 결을 나타내는 결정격자방향으로는 1(x축)-0(y축)-0(z축)이 가장 많이 사용되고, 그 다음으로는 1-1-1을 많이 사용합니다.

에피텍셜 웨이퍼, 두 번째 터 닦기

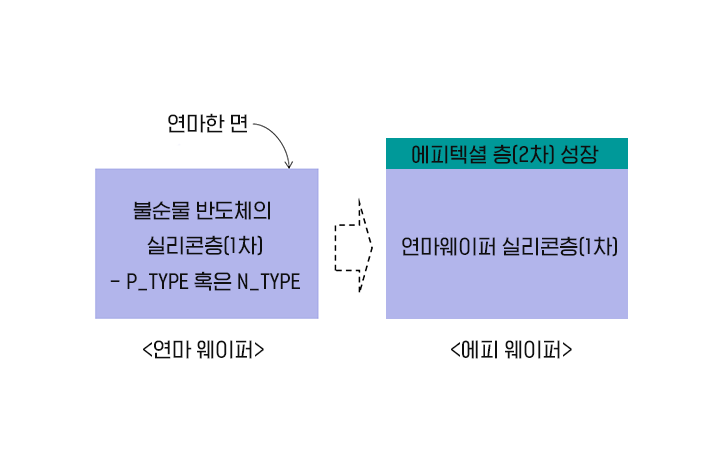

▲ 에피텍셜 웨이퍼의 단면

반도체 성능이 고도화되면서 연마웨이퍼는 고질적인 불량의 한계(표면에 노출되는 결정 결함)를 뛰어넘어야 할 필요성이 대두됐습니다. 그래서 에피텍셜(Epitaxial)웨이퍼가 고안되었지요. 하부층(Substrate)과 동일한 결정격자 방향으로 정렬시키면서 상부층으로 초고순도 단결정을 쌓아 올리는 방식을 에피텍셜 성장(혹은 에피텍시)이라 부르는데요. 이것의 등장으로 반도체가 필요로 하는 요구를 웨이퍼가 어느 정도 맞춰주게 되었답니다. 성장 시키려고 하는 Base층의 표면에는 격자 결이 맞는 원자층을 쌓아 올려야 하는데, 이에 대한 다양한 방식이 적용됩니다.

웨이퍼는 씨앗(Seed)의 역할이 중요

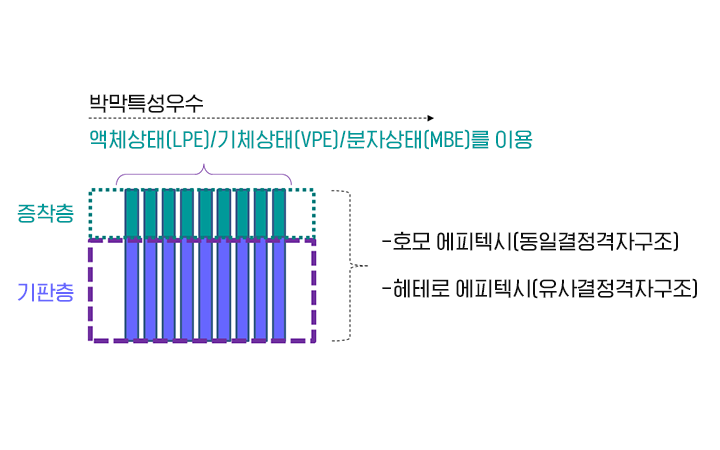

▲ 에피텍셜웨이퍼의 호모 에피텍시와 헤테로 에피텍시 구조

에피웨이퍼는 연마웨이퍼의 기판(Substrate)을 씨앗(Seed) 삼아 단결정으로 된 얇은 박막을 증착시켜 만듭니다. 불순물 농도도 비교적 쉽게 조절하여 기판보다는 몇 배 낮은/높은 농도로도 증착층을 균일하게 유지할 수 있답니다. 캐리어들을 이동시키거나 불순물 입자를 웨이퍼에 집어넣을 때(임플란트 공정), 실리콘의 결정격자방향은 이동자의 진행 방향을 막아서는 중요한 역할을 하는데요. (이런 실리콘결정격자방향은 용융된 실리콘이 Seed에 딸려 올라가는 웨이퍼 성장시 이미 정해집니다.) 성장층이 기판층과 동일한 결정격자인 경우를 호모 에피텍시(Homo Epitaxy)라고 합니다. 층을 쌓는 방법은 액체, 기체, 분자Beam 등 여러 가지 형태를 이용하고 있습니다. 반면, 기판층과 증착증이 서로 다르거나 유사한 결정격자구조를 갖는 것을 헤테로 에피텍시라 합니다.

단, 에피 공정시 기판이 녹아서는 안 되므로 실리콘의 용융온도(약 섭씨 1,440도)보다는 낮은 온도로 진행해야 합니다. (기판은 미용융 상태에서 피증착 물질은 용융시켜야 하기 때문에 온도 조절이 매우 중요합니다) 여기서 특이한 것은 웨이퍼를 성장시킬 때 잉곳과 에피텍시 모두 웨이퍼의 핵심적인 제조방법으로 Seed를 이용한다는 것입니다. 웨이퍼는 뿌린 대로 거두는 제품인 것이지요.

에피텍셜 웨이퍼는 연마웨이퍼 보다 조금 더 발전된 웨이퍼로서 일반 공정에 추가 공정을 거친 웨이퍼이지요. 추가 공정은 연마웨이퍼의 기판위에 약 100um이하의 매우 얇은 두께로 Sub보다 약10배 정도의 고순도로 실리콘 층을 증착시킨 층입니다. 두 번째 터를 닦아놓는 셈이지요. 기판층(단결정 Substrate) 위에 증착층(단결정 Layer)이 성장된 에피텍셜웨이퍼는 연마웨이퍼에 비해 고가이지만, 가격 대비 반도체 제품불량을 적게 만들어 가성비가 좋은 웨이퍼입니다. 또한, 반도체 공정 수를 줄일 수 있다는 장점이 있어 많이 사용하는 추세랍니다.

SOI(Silicon on Insulator) 웨이퍼

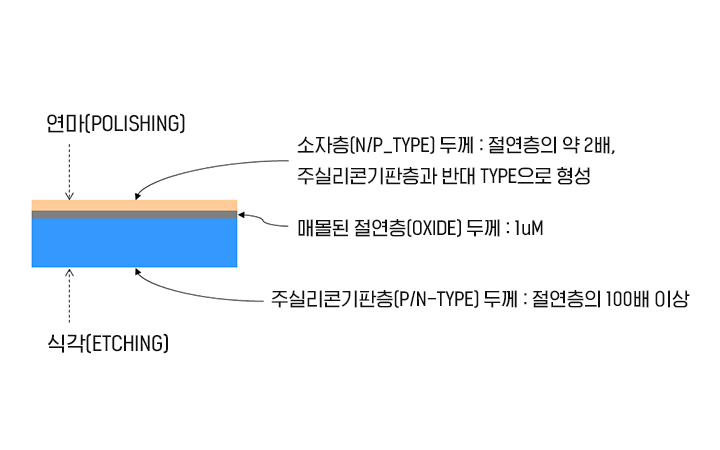

▲ 3개 층으로 형성된 SOI 웨이퍼 단면

에피텍셜 웨이퍼 보다 더 상위개념인 웨이퍼로는 실리콘 단결정층을 산화막 위에 형성한 SOI(Silicon On Insulator)웨이퍼가 있습니다. SOI웨이퍼는 많이 사용되지는 않지만 일부 높은 성능이 필요할 때, 혹은 낮은 Power와 발열을 적게 할 필요가 있을 때 CMOS를 이용해 한정적으로 적용되기도 합니다. 미약한 전도성이라도 근원부터 철저히 차단해야 할 때 SOI가 중요해지지요.

전체 층은 위에서부터 소자층, 절연층, 주실리콘기판층인 3개 Layer로 구성되어 있습니다. 상부층에 배치되는 소자입장에서 보면, 중간에 있는 절연층으로 인해 하부층의 영향이 완전히 차단되도록 하는 것이 필요한데요. 그래서 가운데 층 두께는 1um정도의 매우 얇은 층으로 전기가 흐르지 못하도록 절연막으로 형성되어 있습니다. 또한, 하부층 두께는 절연층 대비 100배에서 600배 정도로 유지됩니다. 맨 위는 소자를 배치하는 층이지요. SOI의 상부층을 만드는 방법도 여러 가지가 있어서, 다른 새로운 웨이퍼를 절연층 위에 덮거나 혹은 별도로 새로운 층을 성장시키는 방법 등으로 다양하게 만듭니다. 2개 웨이퍼를 아래위로 붙이는 것 또한 고난이도의 기술에 속하지요.

작고 얇고 가늘게, 그 중 박막 웨이퍼

처음부터 얇은 두께의 웨이퍼가 필요하거나 일반적인 두께의 웨이퍼를 재생시킬 필요가 있을 경우, 래핑이나 그라이딩을 하여 웨이퍼 두께를 50~80um정도로 감소시킵니다. 이때 웨이퍼 전체 부피 중에서 3분의 1 혹은 8분의 1정도의 많은 실리콘을 없애지요. 웨이퍼의 상층부 실리콘을 제거하는 경우에는 래핑(Lapping)방식을 사용하고, 밑면의 실리콘을 제거할 경우는 주로 그라인딩(Grinding)방식을 적용합니다. 래핑을 한 후에는 웨이퍼 표면을 연마해 표면의 거칠기를 없애주어야 합니다. 연마도 일반적인 연마방식이 있고, 웨이퍼 표면의 스크레치나 미세한 결정결함이 표면에 노출되어 발생되는 약한 결점을 없애주는 Fine연마가 있습니다. 한편 웨이퍼의 두께가 너무 얇으면 쉽게 파손되므로 이를 방지하기 위하여 Destress공정을 진행해주어야 합니다. 이와는 반대로 일반 웨이퍼 두께의 4~5배 정도로 두꺼운 후막 웨이퍼도 있습니다만, 일반적으로는 CMOS에서는 너무 두께가 얇거나 두꺼운 웨이퍼는 사용하지 않습니다. 물론 반도체를 다 만든 후 패키징공정을 진행하기 전에, 일반적으로 웨이퍼 밑면을 알맞은 두께까지 갈아내지요.

CMOS의 Fab공정을 이해하기 위해서는 먼저 웨이퍼에 대하여 알아야 합니다. 그래서 이번 챕터에서는 주로 웨이퍼의 종류와 일부 특성에 대하여 소개했는데요. 다음에는 웨이퍼를 만드는 공정에 대해서도 알아보는 시간을 마련하도록 하겠습니다. 웨이퍼는 반도체 제품과 비교하면 반도체의 일부분에 지나지 않지만, 웨이퍼의 성능과 품질이 반도체에 끼치는 영향은 막대합니다. 웨이퍼는 반도체의 변화무쌍한 변화를 소화할 수 있도록 반도체 기술의 변화에 따라 신속하게 변신해야 합니다. 왜냐하면 웨이퍼는 반도체바라기이기 때문이지요.

※ 본 칼럼은 반도체/ICT에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.