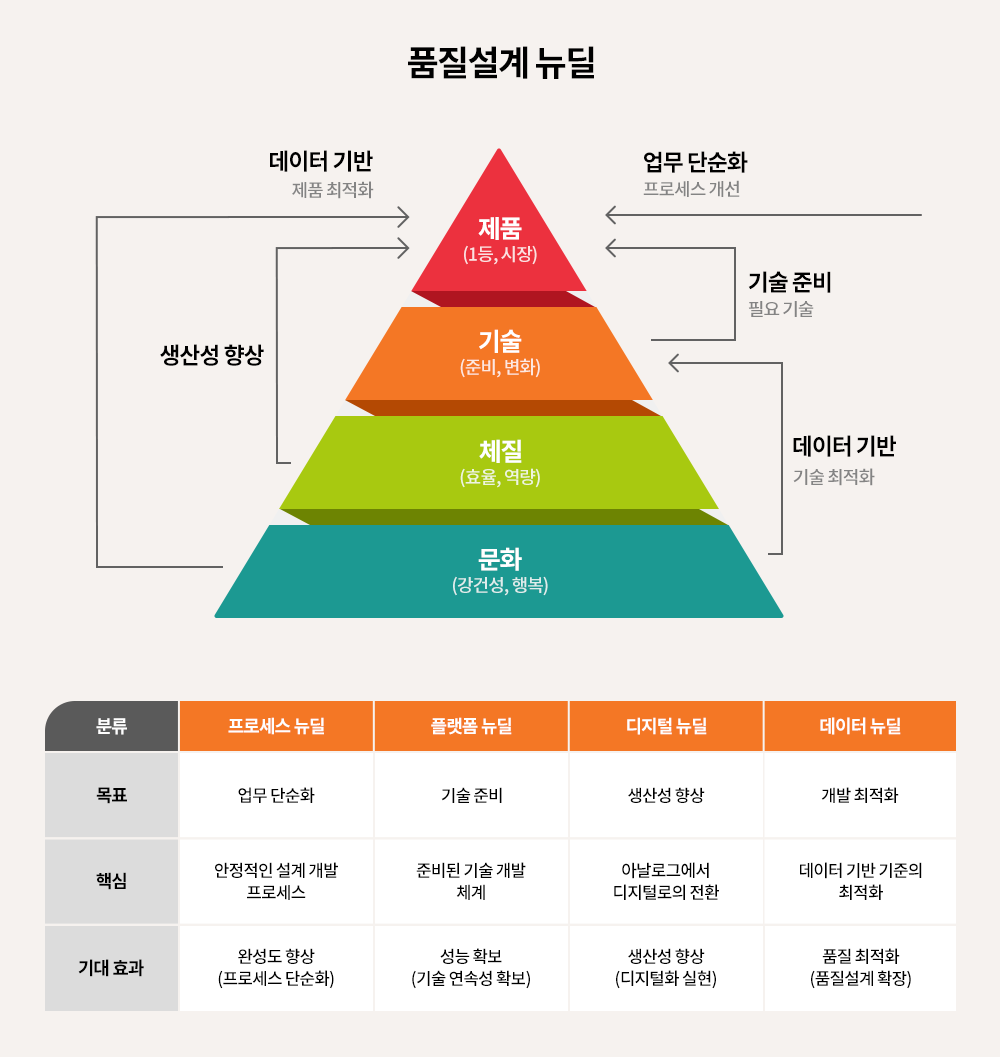

SK하이닉스의 품질설계 뉴딜(Quality Design New Deal) 정책의 목표는 세계 최고의 품질과 특성을 지닌 최적화된 제품을 개발해, DRAM을 안정적으로 공급하고 고객에게 더 나은 가치를 제공하는 것이다. 이를 위해 SK하이닉스는 제품, 기술, 체질, 문화를 변화시켜 완성도와 경쟁력을 지속적으로 향상시킬 수 있도록 시스템을 구축하고 있다. 이 정책을 4가지로 구분하면, 프로세스 뉴딜, 플랫폼 뉴딜, 디지털 뉴딜 및 데이터 뉴딜이다.

▲ ‘DRAM 품질설계 뉴딜 선포식’, 고객에게 더 나은 가치를 제공한다는 의지를 다진 DRAM설계 구성원들

지속적인 개선이 가능한 시스템 구축

미국의 32대 대통령인 F.D. 루스벨트는 대공황 극복을 위한 계획으로 뉴딜정책을 시행하였고, 이는 미국의 글로벌 패권의 토대를 마련했다. 여러 면에서 현재의 ICT 비즈니스 환경과 대공황의 혼돈은 유사해 보인다.

메모리 비즈니스 모델은 점점 더 복잡하고 다양하며 불확실성이 높아짐에 따라, 효율적인 제품 개발이 요구되고 있다. SK하이닉스 DRAM설계는 이러한 요구사항에 효과적으로 대응하고 제품 개발 체계를 혁신적으로 개선하기 위해 품질설계 뉴딜정책을 추진하고 있다.

품질설계 뉴딜정책의 목적은 제품, 기술, 체질, 문화의 변화를 통해 완성도와 경쟁력을 지속적으로 향상시킬 수 있는 시스템을 구축하는 것이다. 이 정책은 다음 4가지로 구성된다.

① 프로세스 뉴딜 : 설계 완성도 향상을 위한 안정적인 설계 업무 프로세스 확보

② 플랫폼 뉴딜 : 1등 기술 확보를 위한 기술 개발 체계 준비와 기술의 연속성 확보

③ 디지털 뉴딜 : ‘아날로그에서 디지털’로의 변화를 통한 개발 효율 및 생산성 향상

④ 데이터 뉴딜 : 경험 기반의 일을 데이터 기반의 일로 전환을 통해 최적화의 문제 해결

▲ SK하이닉스의 품질설계 뉴딜

세계 최고 DRAM 완성도를 위한 [프로세스 뉴딜]

DRAM설계는 ▲설계준비와 ▲설계 두 단계로 구성된다. 설계준비 단계는 제품 target을 결정하고 경쟁력 있는 제품 설계를 준비한다. 또한 제품 architecture 검토 및 불량 zero를 위한 사전 체크리스트 점검을 통해 설계 완성도를 확보한다. 설계 단계는 설계준비 단계에서 검토한 사항을 바탕으로 효율적인 설계를 통해 세계 최고의 제품 특성을 보장한다. 이를 위해서는 설계 전 과정의 단계별 업무와 업무별 체크리스트가 세밀하고 명확하게 정의되고 실행하는 것이 중요하다.

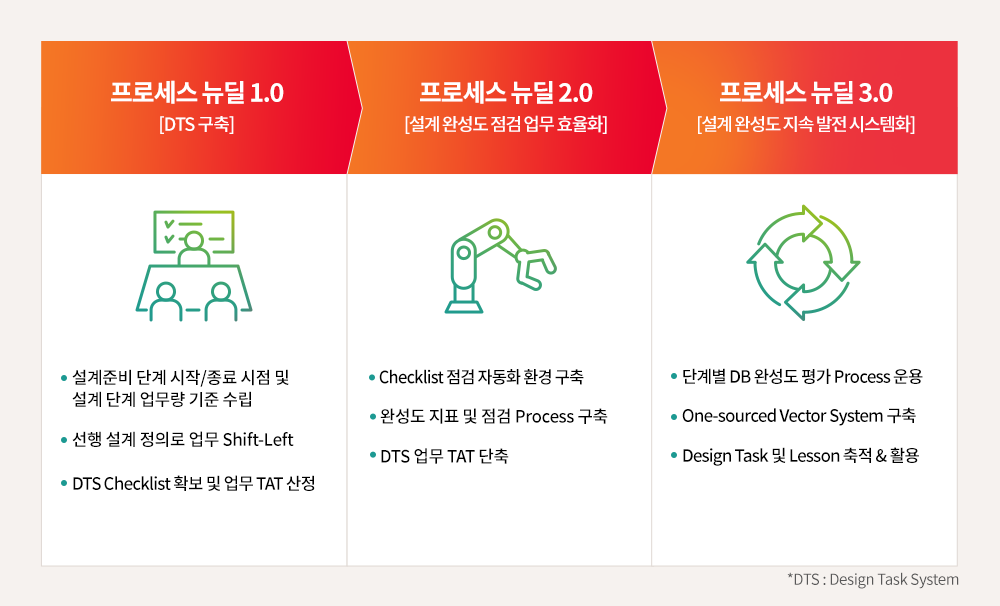

프로세스 뉴딜에서는 설계 단계의 제품 성격에 맞는 제반 사항을 상세히 기술하고, 설계준비 단계의 시작과 끝이 무엇인지 명확하게 정의한다. 또한, SK하이닉스는 성공적인 제품 개발을 위해 스테이지 게이트 프로세스(Stage-Gate Process)* 를 구축하였다. 이것은 R&D Process로 제품의 품질향상을 목표로 아이디어부터 출시까지 제품 개발의 전 과정을 관리한다. 프로세스 뉴딜은 설계 단계의 설계 완성도 향상 및 효율성을 극대화하기 위해 크게 3단계로 진행된다.

* 스테이지 게이트 프로세스(Stage-Gate Process) : 전체 제품 개발 공정을 관리하는 R&D Process이다. 스테이지는 R&D 활동을 수행하는 시기를 나타내고 게이트는 각 단계에서 R&D 활동을 평가하여 계속 또는 중단 여부를 결정한다.

▶ 1단계 : 설계준비 단계, 설계 단계, 제품 테스트 단계의 모든 작업을 정의하는 DTS(Design Task System)를 구축해, 설계 단계에 해야 할 일들(Check Item)이 사전에 준비될 수 있도록 우선순위 결정과 TAT(Turn Around Time) 산정 작업을 진행한다. 사전 작업의 성격 및 프로젝트 특성에 따라 3가지 선행 설계 모델을 제공함으로써 설계준비 단계 이후에 설계 단계를 안정적으로 수행할 수 있게 한다.

▶ 2단계 : 1단계에서 정의한 Check Item 및 Check 방법에 대한 솔루션을 확보하고 TAT를 개선한다. 이는 Check 자동화 및 수치화를 통해 완성도 지표를 빠르게 확인할 수 있어 시스템 효율을 극대화할 수 있다.

▶ 3단계 : 설계 업무 시스템이 고도화될 수 있는 선순환 체계를 구축하는 한편, 구축된 DTS를 적극 활용한다. 각 설계 단계에서 일정 수준의 단계별 완성도를 확보하여 업무를 분산한다. 누적된 lesson을 검증 가능한 통합 테스트 패턴(단일 소스 벡터 시스템 : One-sourced Vector System)에 포함시켜 설계 완성도를 지속적으로 유지한다.

프로세스 뉴딜은 설계 기간 동안의 모든 작업을 정의하고 관리한다. 이를 통해, 사전 설계 업무와 설계 업무를 명확히 구분하고, 설계 업무와 검증에 주어진 시간을 사용할 수 있도록 한다. 또한 각 단계에서 신속하고 적절한 의사결정 기준을 수립하여 최적의 인력과 일정을 투입하여 최고 수준의 설계 완성도를 달성한다.

▲ 프로세스 뉴딜 3단계

세계 최고 DRAM 기술 개발을 위한 [플랫폼 뉴딜]

DRAM 기술 개발의 한계 요인은 다음과 같다.

1) 연속성 있는 기술 체계 부재로 요소 기술 선정 시에 엔지니어의 개인 역량과 판단으로 결정

2) 필요 기술에 대한 선행 점검 미흡 및 검증되지 않은 기술 적용

이러한 한계 요인들은 세계 최고 사양의 제품 개발에 위험 요소가 되었고, 체계적인 기술 플랫폼 구축이 필요해졌다.

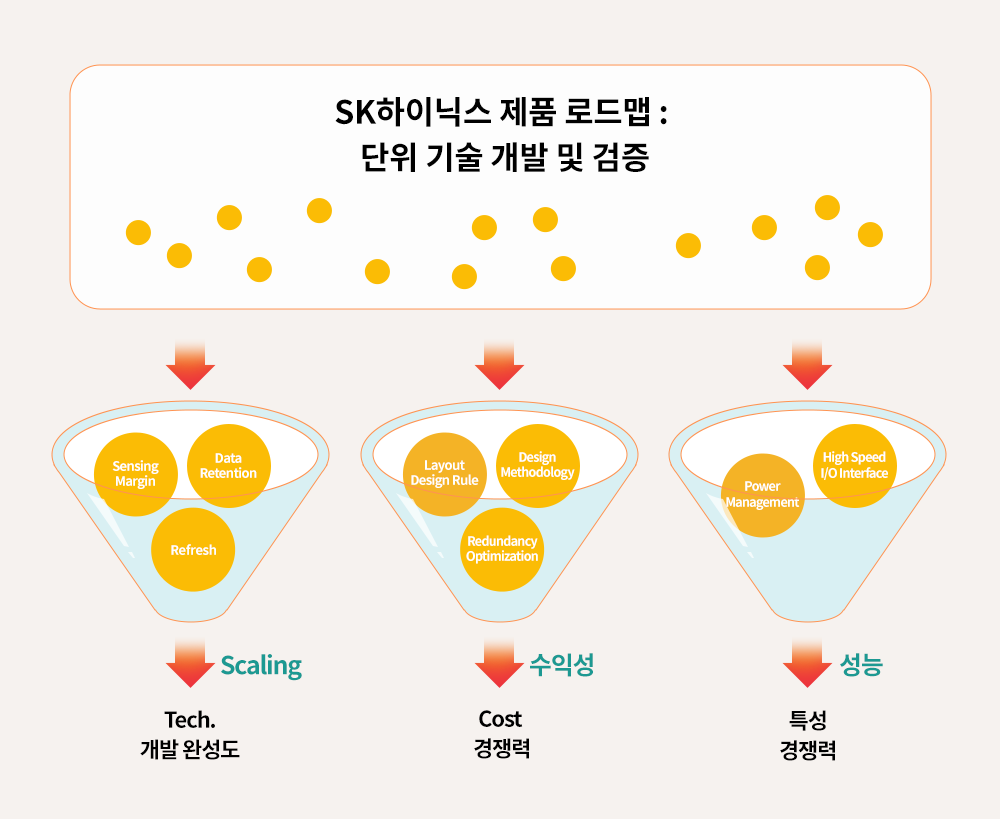

플랫폼 뉴딜은 필요 요소기술 로드맵과 연계를 통해 필요 기술을 미리 점검하고, 완성도 있는 기술을 개발하며, 이를 바탕으로 제품 개발에 필요한 Packing(기술집합체) 형태의 기술 프레임 및 시스템을 구축한다. 일하는 방법의 틀(시스템)인 플랫폼을 구축하고, 시기에 맞는 제품 개발을 가능하게 하는 것이 목표이며, 3개의 세부적인 플랫폼으로 구성되어 있다.

▶ 스케일링 플랫폼(Scaling Platform) :DRAM Process Technology 개발을 위한 주요 인자인 Sensing Margin/Data Retention 특성 확보를 위한 기술들의 집합체(Bank Packing)를 준비한다.

▶ 수익성 플랫폼(Cost Platform) : 기술 플랫폼으로서 각 세대의 Process Technology에서 비트 성장률(Bit Growth)*을 극대화하고 넷 다이(Net Die)** 경쟁력 확보를 통해 세계 최고 원가 경쟁력을 제공한다. 주요 기술은 레이아웃 설계 규칙(Layout Design Rule) 적용을 통한 회로 면적 최소화, 수리를 위한 여분 회로(Redundancy) 최적화를 통한 수율 개선 등이 있다.

▶ 성능 플랫폼(Performance Platform) : 성능 플랫폼은 SK하이닉스 제품 로드맵에 필요한 회로 요소기술을 바탕으로 세계 최고 속도에서 최소의 전력을 소모할 수 있는 기술을 미리 확보하기 위한 도구다. 이를 실현하기 위해 고성능 소자 특성에 설계 기술을 더한 테스트용 시제품을 운용하여 세계 최고 특성을 만드는 기술을 사전에 검증한다

* 비트 성장률(Bit Growth) : 메모리 반도체의 전체 성장률을 의미하며 메모리 용량을 1비트 단위로 환산하여 계산한다. 이 개념은 출하 수량을 기준으로 계산할 때 발생할 수 있는 성장률의 왜곡을 방지하기 위해 도입.

** 넷 다이(Net Die) : 웨이퍼에서 실제로 생성된 다이의 총개수.

이러한 3개 플랫폼을 결합해, 효율은 극대화하고 최종 제품 경쟁력 또한 확보할 수 있었다. 스케일링 플랫폼(Scaling Platform)은 새로운 공정 기술(Process Technology) 개발을 가능하게 하는 회로/공정 기술을 제공하며, 이를 바탕으로 수익성 플랫폼(Cost Platform)과 성능 플랫폼(Performance Platform)은 제품 경쟁력을 보장한다. 제품별 필수 요소기술 로드맵을 구축하여 미래에 필요한 기술을 사전에 발굴하고, 이를 Test vehicle을 통해 사전 검증한다. 이를 활용하여 SK하이닉스는 플랫폼 기술 및 일하는 방법의 틀을 만들고 변화하는 목표에 따라 필요한 기술을 채워 경쟁력 있는 제품을 개발할 수 있다. 따라서 일회성 대응이 아닌 지속적인 기술개발 환경을 제공하게 된다.

▲ 플랫폼 뉴딜

세계 최고 DRAM설계 효율화를 위한 [디지털 뉴딜]

DRAM설계는 그동안 회로 면적 최소화를 통한 넷 다이 증가에 우선순위를 두고 Custom DRAM설계 방식을 적용해 왔다. 그러나, 최근 제품군의 다양화, 제품 용량 및 성능 증가에 따라 개발 효율 저하 문제가 발생하고 있다. 그 결과, 설계 디지털화(Design Digitalization)를 위한 표준화, 규격화, 자동화 필요성이 증가하고 있다.

디지털 뉴딜의 목적은 디지털 인프라 구축을 통해 DRAM설계의 구조적 변화를 유도하고, 디지털 설계방식을 활용하여 개발 효율을 높일 수 있는 체계를 구축하는 것이다. 이를 달성하기 위해 다음 세 단계를 수행한다.

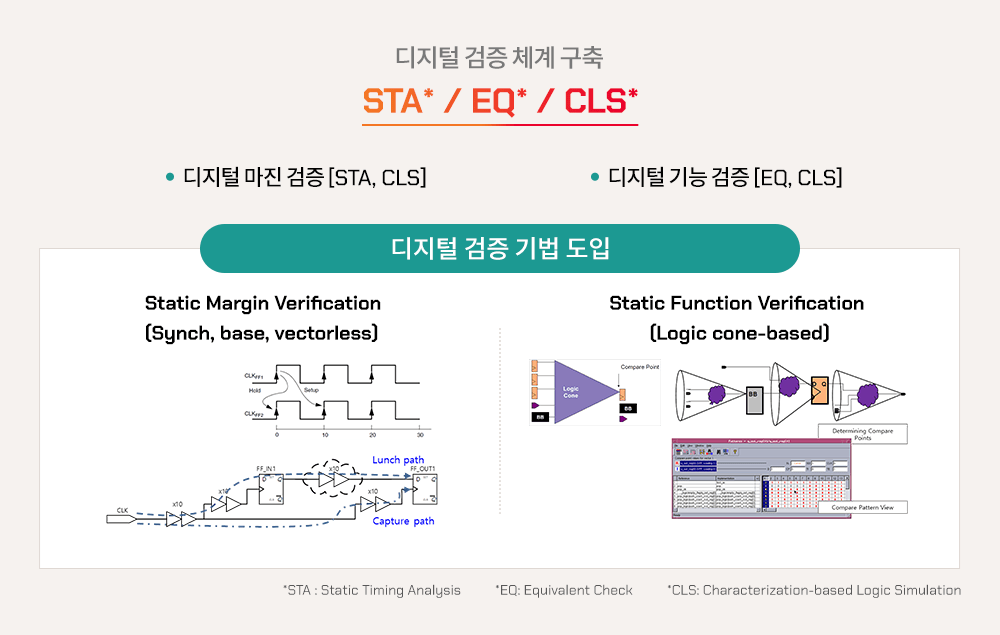

▶ 디지털화 기반 구축 : 기존 로직 반도체 설계에 적용되었던 STA(Static Timing Analysis : 정적 타이밍 분석)를 Custom DRAM설계에 적용하기 위한 DRAM STA 방법론을 개발한다. STA를 DRAM설계에 적용함으로써, 다양하고 복잡한 테스트 패턴 없이 짧은 시간에 높은 DRAM 회로 검증 커버리지를 달성할 수 있다. 이로써, 설계 단계의 완성도를 보장한다.

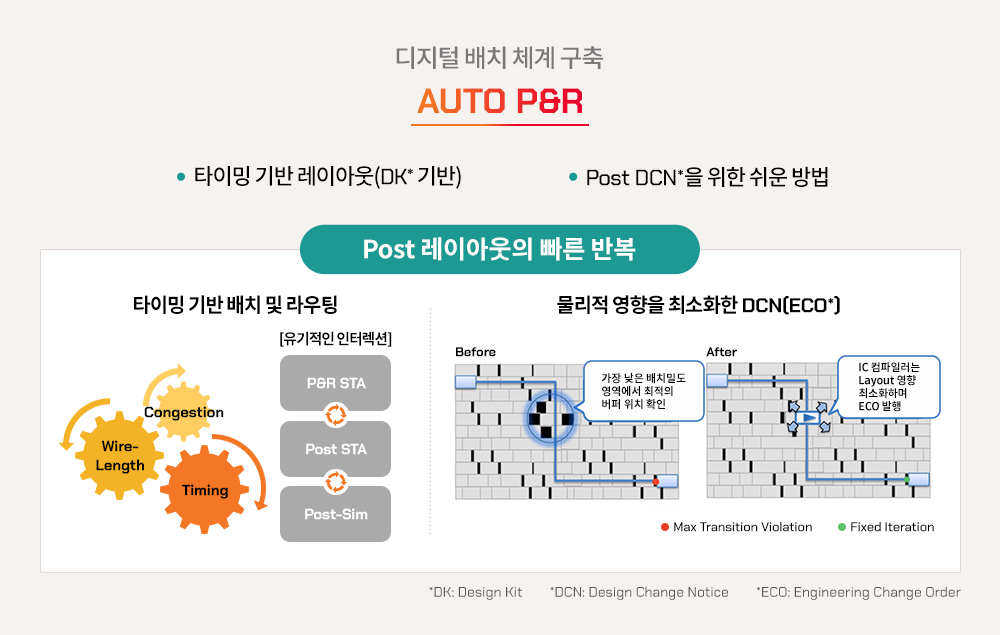

▶ 디지털화 전개 : 디지털화 기반 구축을 통해 확보된 STA 환경을 기반으로 타이밍 기반 자동 배치 및 라우팅(Timing-driven Automatic Placement and Routing, Auto P&R) 방법을 개발한다. DRAM을 위한 Auto P&R 방법 개발하여 배치 설계(Layout Design)의 생산성을 높이고 경직성을 낮춰서 전체 개발 효율을 높일 수 있다.

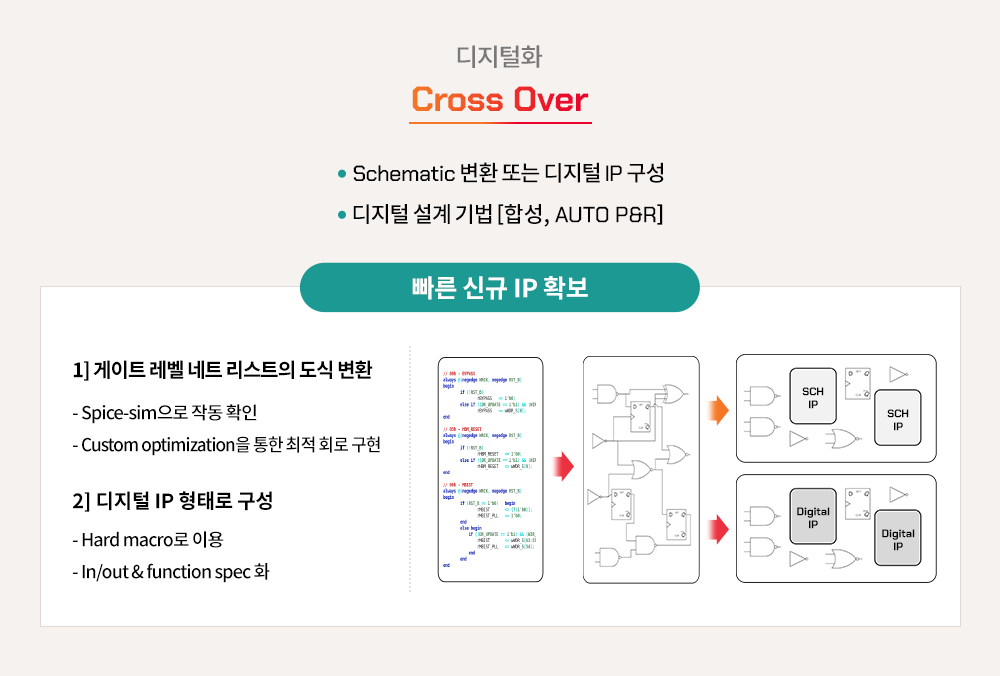

▶ 설계 디지털화 : ‘디지털화 기반 구축’ 및 ‘디지털화 전개’가 설계 검증(Design Verification) 및 배치(Layout)의 디지털화를 달성하는 것이라면, ‘디지털화 설계’는 회로 설계의 디지털화를 의미한다. 또한, 차세대 고대역폭 메모리(High Bandwidth Memory, HBM) 개발을 위해 논의하고 있는 기술인 DRAM용 로직 파운드리 설계 기술을 확보하고 디지털 설계 영역 확장한다. 이러한 검증, 배치, 회로 설계의 디지털화를 수행함으로써 궁극적으로 DRAM설계 체질을 변화시키고, DRAM설계에 특화된 디지털 설계 methodology 체계를 구축할 수 있다. 이를 통해 SK하이닉스는 다양한 고객의 니즈와 급변하는 시장 상황에 대응하고 신제품의 개발 효율성을 높일 수 있다.

SK하이닉스는 디지털 뉴딜을 통해 DRAM설계의 체질을 바꾸는 디지털화 인프라를 구축한 후, 적용 분야를 지속적으로 확대 모색할 것이다. 그리고 이를 DRAM설계 문화로 내재화함으로써 디지털화의 강점인 표준화, 규격화, 자동화를 통한 개발 효율(생산성)을 혁신적으로 높여 나갈 수 있을 것으로 기대하고 있다.

세계 최고 DRAM설계 최적화를 위한 [데이터 뉴딜]

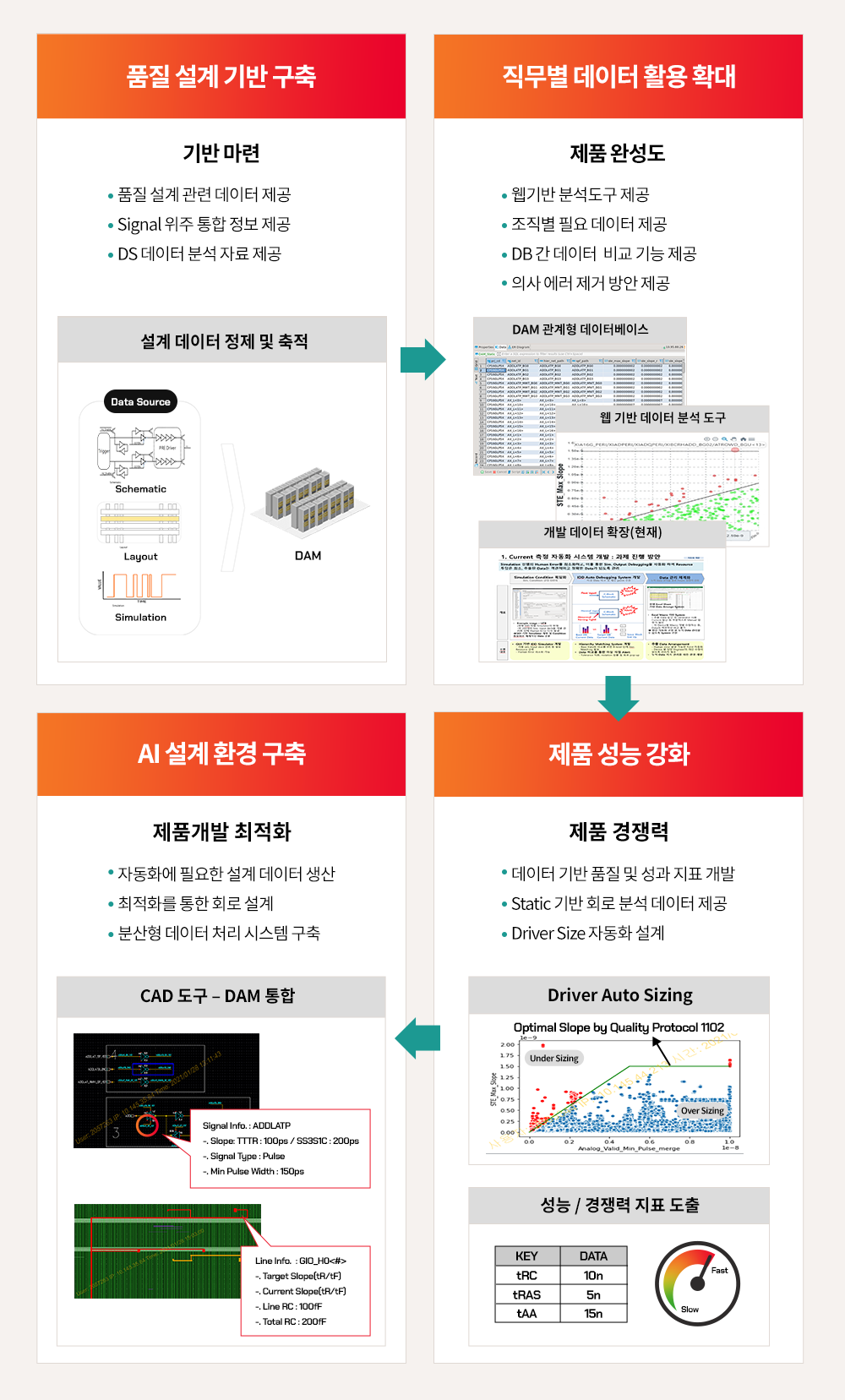

SK하이닉스 DRAM설계는 2021년에 품질설계를 발표하고, 품질설계의 기반이 되는 DAM(신호정보 누적 정보시스템)을 구축했다. DAM에 축적된 설계 데이터(회로, 배치, 신호 정보 등)의 활용 방안을 고도화하는 것이 데이터 뉴딜의 배경이다. 이를 통해, 경험 기반 업무를 데이터 기반 업무로 변화시켜 DRAM설계 효율 및 최적화 문제를 해결할 수 있다.

데이터 뉴딜은 데이터를 활용한 설계 최적화 기여도를 점진적으로 확대하고, 궁극적으로 AI 기반 미래 설계 환경을 준비하는 것이다. 이를 위해 SK하이닉스는 신규 품질 규약 도출과 DRAM설계 인공지능 시스템(HoVIS: 하이닉스와 자비스(Jarvis)의 합성어, 자비스는 아이언맨의 인공지능 시스템)을 개발할 계획이다.

▶ 신규 품질 규약 도출 : 품질 규약은 ‘경험’과 ‘데이터’로 구분하여 도출할 수 있다. 이는 ‘경험’ 관련 불량 사례들을 신규 품질 규약화하고, ‘데이터’ 관련 방대한 정보 속에서 Insight를 도출할 수 있는 N차원 다변량 분석 발전을 통해 신규 품질 규약화를 추진할 수 있다.

▶ HoVIS: 예상되는 프로세스별 Task(SPEC, Circuit Design, Pre Auto P&R, Optimizing, Digital Verification, Unit Verification, Full Chip Verification)에 확보해야 할 최적화 기술을 순차적으로 개발하면서, 미래의 설계 환경 측면에서 세계 최고의 DRAM설계 효율과 최적화 문제 해결 능력을 준비해 나갈 예정이다. 이를 위해 데이터 뉴딜은 3단계에 걸쳐 순차적으로 진행된다.

1단계는 데이터를 기반으로 신규 품질 규약이 도출될 수 있는 체계를 개발하고, 설계 완성도를 신규 품질 규약의 기준으로 설정하는 것이다. 2단계는 신규 품질 규약의 기준을 설계 완성도에서 설계 성능 개선으로 상향한다. 마지막 3단계는 설계 성능 개선에서 설계 최적화로 상향시켜 단일 신호 품질, 이중 신호 품질, 다중 신호 품질을 순차적으로 확보한다.

이처럼 신규 품질 규약 기준을 제품의 완성도 → 성능 → 최적화로 상향하여 DRAM설계를 강화하면서 SK하이닉스 DRAM설계 인공지능 시스템인 HoVIS와 연계하여 AI 기반 미래 설계 환경의 기준으로 활용된다면, 경험 기반의 일을 데이터 기반의 일로 변화시켜 효율과 최적화의 문제를 함께 해결할 수 있을 것으로 기대한다.

▲ 데이터 뉴딜

고객에게 더 나은 가치 제공

최근 급변하는 ICT 비즈니스 환경에서는 이러한 새로운 시대에 적합한 틀과 기준의 재정립 요구가 증가하고 있다. SK하이닉스의 DRAM 품질설계 뉴딜정책은 세계 최고의 품질, 완성도 및 특성을 갖는 최적화된 제품 개발을 목표로 한다. 이 정책은 최고 품질의 DRAM을 안정적으로 공급하고D 글로벌 ICT 생태계에서 요구하는 혁신적인 제품 개발 시스템을 개발하며, 고객에게 더 나은 가치를 제공함으로써 SK하이닉스의 ESG 경영에도 기여할 것이다. SK하이닉스는 업계의 선두주자로서 체계와 표준을 만들어 계속 새로운 이정표를 세워나갈 것이다.