SK하이닉스는 D램 기술의 초격차를 유지하기 위해 기술 한계를 극복할 수 있는 다양한 연구를 진행하고 있다. 특히 D램 셀(Cell)의 크기가 미세화되면서 몇 가지 기술적 한계에 직면하였는데, 그중 가장 큰 문제는 D램 셀 캐퍼시터(Capacitor)의 면적은 작아지더라도 요구되는 정전 용량(Capacitance)*은 유지해야 하는 것이다. 이러한 문제를 해결하기 위해서는 높은 유전상수(K)*와 낮은 누설 전류 특성을 가진 초박막 유전체(Dielectric, DE)* 개발이 필수적이다.

* 유전상수(Dielectric constant): 유전체의 전기 유전 특성을 나타내는 값. 유전상수가 높을수록 유전체는 더 많은 전하를 축적할 수 있음

* 유전체(Dielectric, DE): 전기장에 노출되면 극성을 보이는 절연 물질로, 전기장에 노출되면 분극화되어 정전기장을 지원할 수 있음

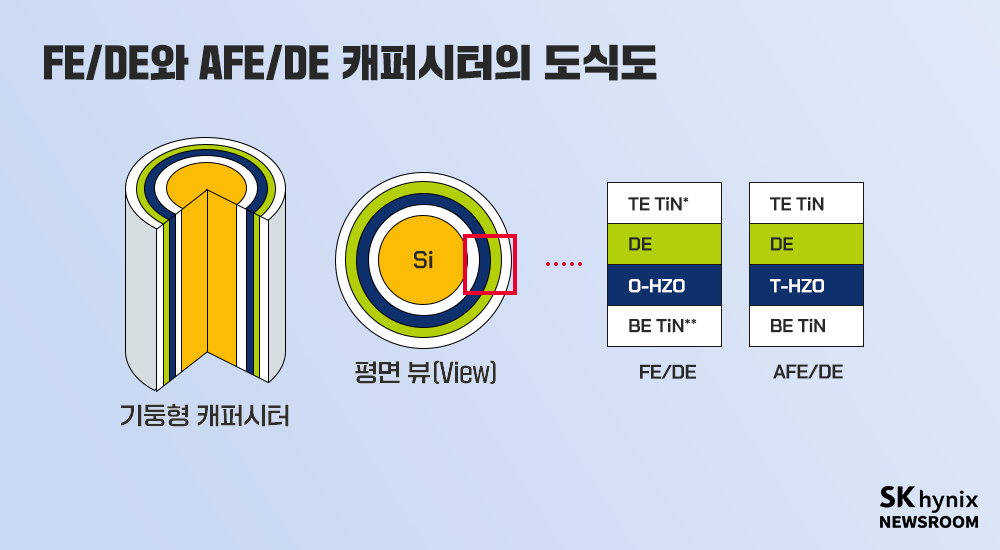

이를 위해 SK하이닉스 RTC는 [그림 1]과 같이 초박형 강유전체(Ferroelectric, FE)*와 반강유전체(Anti-Ferroelectric, AFE)*를 초박막 유전체와 각각 융합하는 새로운 방법을 시도했다. 이는 기술적 한계에 부딪혀도 새로운 방법을 연구하여 지속적으로 해결 방향을 찾았던 사례이기에 소개하고자 한다. 이 글에서는 ‘IEEE EDTM 2023’에서 처음 발표된 해당 연구를 요약하여 그 과정과 결과를 살펴보고자 한다.

* 반강유전체(Anti-Ferroelectric, AFE): 외부 전기장에는 강유전성 분극 특성을 보이지만, 외부 전기장이 없을 때는 자발 분극이 존재하지 않는 물질

▲ 그림 1 : [좌측] FE/DE와 AFE/DE 기둥형 D램 캐퍼시터 도식도와 평면 뷰(View). FE/DE와 AFE/DE 모두 동일한 구조로 만들어짐. [우측] 강유전체와 반강유전체 이중 레이어의 차이를 확인하기 위해 각각 다른 박막[O-phase* rich HZO(Hafnium–zirconium oxide)* 강유전체 이중 레이어와 T-phase* rich HZO 반강유전체 이중 레이어] 박막을 적용한 구조의 모습

* HZO(Hafnium–zirconium oxide): 하프늄(Hf)과 지르코늄(Zr)으로 이루어진 산화물(HfZrO2)

* T-phase(Tetragonal phase): 세 개의 축이 직각을 이루고, 그중 두 개의 축이 같은 결정 구조. T-phase HZO는 반강유전성과 유사한 전기적 특성을 보임

D램 셀 캐퍼시터로 사용하기에 무엇이 더 적합한지 찾기 위해, 연구에서는 CMOS 공정 적합성이 높은 하프늄지르코늄옥사이드(HZO) 기반의 강유전 물질(O-phase HZO)과 반강유전 물질(T-phase HZO)을 활용하여 ‘초박형 강유전체 이중 레이어(이하 FE/DE)’와 ‘초박형 반강유전체 이중 레이어(이하 AFE/DE)’를 제조하였다.

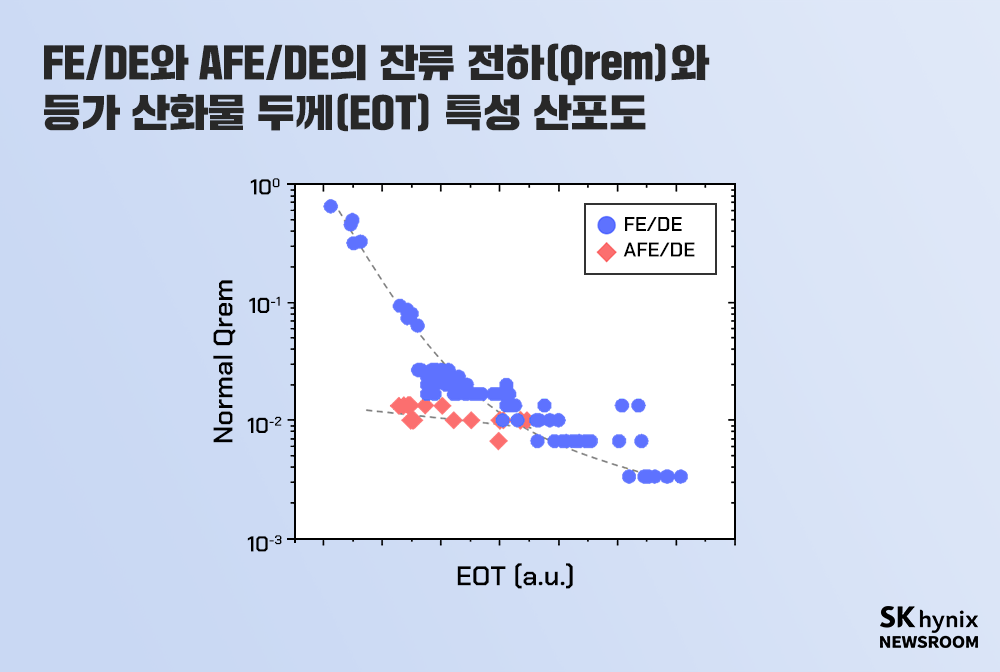

이때 제조된 이중 레이어의 강유전성과 반강유전성 특성을 제어하며, D램 캐퍼시터의 주요 특성인 등가 산화물 두께(Equivalent Oxide Thickness, EOT)*와 강유전체의 주요 특성인 잔류 전하(Qrem)* 값의 상관관계를 분석하였다.

* 잔류 전하(Qrem): 강유전체 또는 반강유전체 박막에 남아 있는 분극을 의미

[그림 2]에서 볼 수 있듯이, ‘FE/DE’로 구성된 캐퍼시터는 등가 산화물 두께가 크게 개선되었지만, 잔류 전하가 급격히 증가하는 트레이드오프(Trade-off) 관계를 보였다. 이러한 관계는 강유전층의 강유전 특성이 발현되는 정도가 증가하며 자발 분극 특성이 높아져 잔류 분극도 함께 커졌기 때문이다.

반면에 ‘AFE/DE’로 구성된 캐퍼시터는 등가 산화물 두께(EOT)가 작은 폭으로 개선되었지만, 잔류 전하(Qrem)의 증가 폭이 매우 작았는데, 이는 반강유전체의 자발 분극 특성이 강유전체 대비 매우 낮기 때문이다.

▲ 그림 2 : FE/DE와 AFE/DE의 다양한 잔류 전하(Qrem)와 등가 산화물 두께(EOT) 특성을 보여주는 산포도

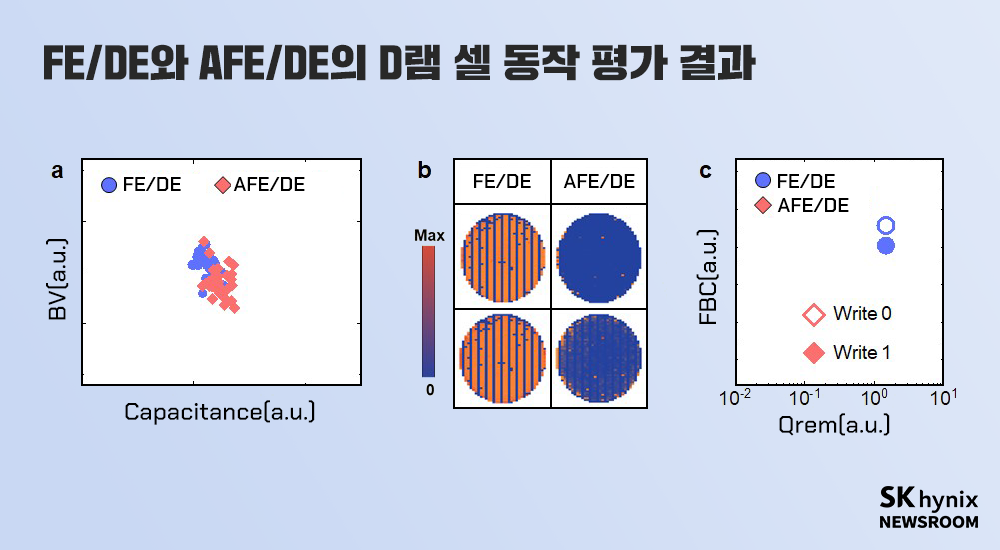

잔류 분극 특성에 따른 D램 셀 동작 차이를 분석하기 위해 캐퍼시터의 주요한 트레이드오프 특성인 BV*(Breakdown Voltage)와 정전 용량 값이 유사한 ‘AFE/DE’와 ‘FE/DE’를 선정하여 평가했다[그림 3]. 그 결과, 두 캐퍼시터는 기존의 주요한 트레이드오프 특성인 BV(Breakdown Voltage)*와 정전 용량 값이 유사했으나, D램 셀 동작 평가에서는 큰 차이를 보였다(그림 3a).

그러나 ‘AFE/DE’ 캐퍼시터를 활용한 D램 셀은 ‘FE/DE’ 캐퍼시터를 활용한 D램 셀보다 현저히 적은 tWR(Write Recovery Time)*과 FBC(Fail Bit Counts)*를 보였다(그림 3b). 이는 tWR 테스트를 통해 D램 셀의 데이터 쓰기 동작 시간을 확인했을 때, ‘FE/DE’의 강유전성으로 인해 발생하는 상대적으로 많은 잔류 전하(Qrem) 특성이 쓰기 동작 중에 반대 극성으로 작용, 이후의 D램 동작을 방해하여 쓰기 동작이 제대로 작동하지 않기 때문이다(그림 3c). 따라서 강유전체 및 반강유전체를 D램 캐퍼시터로 활용할 경우, 기존의 주요한 특성인 정전 용량(Capacitance)과 BV 특성(누설 전류)뿐만 아니라 잔류 전하(Qrem)의 특성까지 고려해야 함을 확인했다.

* tWR(Write Recovery Time): D램 셀(Cell)에 데이터가 Write 되는데 요구되는 적정 시간. tWR이 충분하지 못할 경우 데이터 읽기와 쓰기 작업 시 데이터 오류를 유발함

* FBC(Fail Bit Counts): D램 구동 평가 시 한 장의 웨이퍼에서 발생한 불량 비트(Fail Bit)의 개수

▲ 그림 3 : BV(Breakdown Voltage)와 정전 용량(Capacitance) 값이 유사한 ‘AFE/DE’와 ‘FE/DE’를 선정하여 평가한 결과. (a) ‘FE/DE’와 ‘AFE/DE’의 BV와 정전 용량(Capacitance) 특성의 산점도. (b) D램 셀의 tWR 불량 비트들에 대한 12인치 웨이퍼 맵, (c) FBC(Fail bit counts)와 잔류 전하(Qrem) 특성의 상관관계 그래프

요약하면, 이 연구는 ‘FE/DE’와 ‘AFE/DE’의 전기적 특성을 조사하고, D램 셀에서 실제 동작을 검증했다. 그 결과 ‘FE/DE’는 등가 산화물 두께(EOT)를 줄이는 데에는 우수한 잠재력을 보여 주었지만, 상대적으로 높은 잔류 전하 특성으로 인해 tWR 테스트 시 불량 비트(Fail Bit) 발생 확률이 급격히 증가함을 확인했다.

반면에, ‘AFE/DE’는 등가 산화물 두께를 줄이는 데에는 제한적이지만, 상대적으로 낮은 잔류 전하 특성으로 인해 tWR 테스트 시 불량 비트(Fail Bit) 발생 확률이 감소함을 확인했다.

따라서, 안정적인 D램 동작을 위해서는 잔류 전하가 엄격히 제어되어야 하므로 ‘FE/DE’보다 ‘AFE/DE’가 D램 셀 캐퍼시터로 사용하기에 더 적합하다는 결론을 얻을 수 있었다.

본 연구에서는 강유전체 성질이 추가된 다중 레이어 유전체를 최적화하여 D램 셀 캐퍼시터로 활용할 수 있는 하나의 방안을 제시하였다. 향후 D램 기술의 미세화를 위해, 이 기술에 대한 심층적인 검증뿐만 아니라 높은 유전 물질을 확보하기 위한 다양한 접근 방법이 지속적으로 발굴될 것으로 예상된다.