3차원을 뜻하는 3D 낸드플래시가 4D로 진화했습니다. SK하이닉스는 최근 세계 최초로 4D 낸드 구조의 96단 512Gbit TLC(Triple Level Cell) 낸드플래시 개발에 성공해 연내 초 양산에 진입한다고 밝혔습니다. 128단부터 향후 200단 이상의 차세대 로드맵에서도 4D 기술을 적용할 계획이라고 하는데요. 업계 최고의 성능과 생산성을 갖춘 96단 512Gbit 4D 낸드의 핵심 기술에 대해 알아보도록 하겠습니다.

4D 낸드플래시 개발의 일등공신, PUC

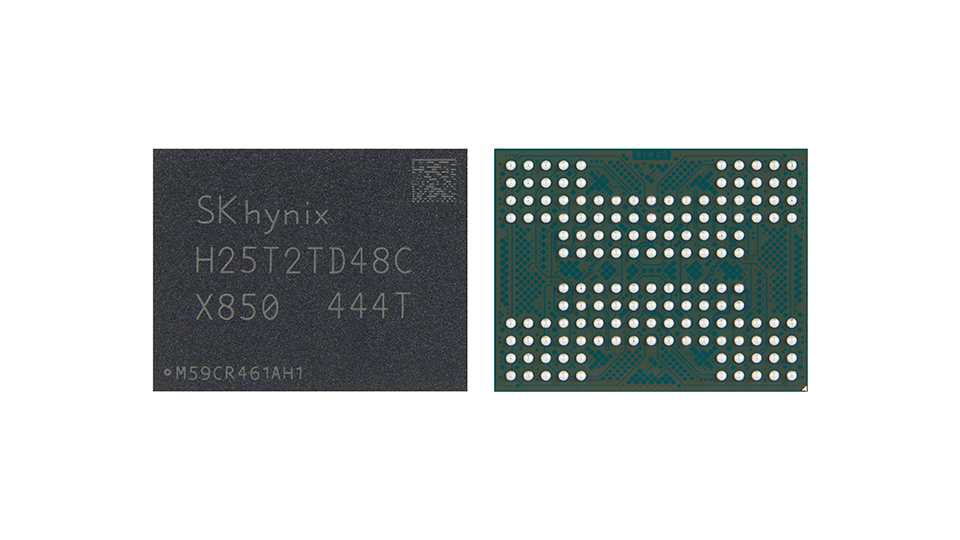

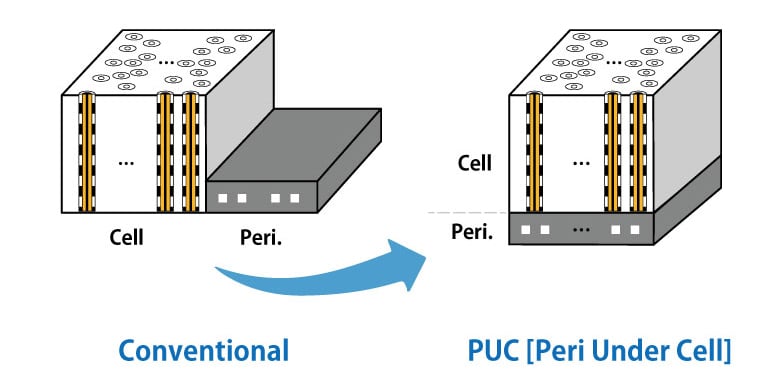

SK하이닉스가 ‘4D 낸드플래시’란 이름을 붙인 이유는 기존 3D 낸드의 CTF(Charge Trap Flash) 구조에 PUC(Peripheral Under Cell) 기술을 결합했기 때문입니다. 셀 작동을 관장하는 주변부(peri) 회로를 셀 아래로 옮겨 면적을 줄인 것이죠. 아파트 옥외주차장을 지하주차장으로 구조변경해 공간의 효율성을 높인 셈입니다. 반도체 업계의 지상과제인 면적 문제를 해결해 생산 효율(단위 웨이퍼당 생산가능 칩의 수)을 높이기 위해서입니다.

▲SK하이닉스는 셀 옆에 붙어있던 주변회로(Peri)를 셀 아래로 배치해 공간 효율성을 확보했다.

여기서 주변부(peri) 회로란 데이터를 저장하는 셀들을 선택하고 컨트롤하는 역할을 하는 로직(Logic) 회로를 뜻합니다. 주로 Row와 Column Decoder, Sense Amplifier와 컨트롤러 회로 등을 의미하는데요. ‘주변부’라 불리지만 메모리 제품에서 반드시 필요한 영역으로, 통상 전체 메모리 제품에서 20~30%의 큰 면적을 차지한답니다. SK하이닉스에 따르면, 이 제품은 72단 512Gbit 3D 낸드보다 칩 사이즈는 30% 이상 줄었고, 웨이퍼(Wafer) 당 비트(bit) 생산은 1.5배 향상됐습니다. 동시 처리 가능한 데이터는 업계 최고 수준인 64KByte로 2배 늘었죠. 작은 사이즈 덕에 스마트폰용 모바일 패키지에도 탑재가 가능합니다. 4D 낸드 1개로 기존 256Gbit 3D 낸드 2개를 대체할 수 있게 됐습니다.

이 같은 혁신을 가능하게 한 PUC 기술은 면적을 줄여 생산효율을 높이기 위한 돌파구입니다. 현재 SK하이닉스를 비롯해 경쟁사인 미국 마이크론은 이를 ‘CMOS Under the Array (CUA)’로, 삼성전자는 ‘Core Over Periphery (COP)’로 부르며 개발 중입니다.

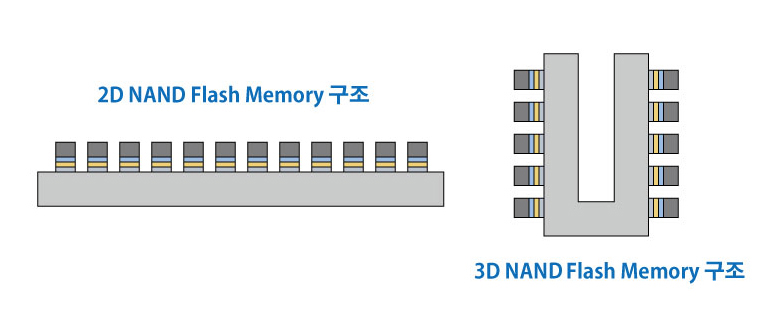

이처럼 반도체 업계가 낸드플래시를 3D로 쌓아올리고, 이제는 아래 면적까지 활용해 4D로 나아가려는 이유는 생산효율을 확보하면서 저장용량을 높이는 일이 매우 어렵기 때문입니다. 3차원 구조의 3D 낸드플래시 기술은 회로 선폭을 줄여 집적도를 높여온 기존의 2D 낸드 기술이 10나노대에서 막히면서 탈출구로 나온 해법이었죠. 반도체를 아파트처럼 쌓아올려 집적도를 높이고 저장 용량을 늘린 것입니다.

2D 낸드 vs 3D 낸드 기술의 차이점은?

2D 낸드와 3D 낸드의 차이점은 크게 공정, 물질, 소자구조 등 3가지로 요약할 수 있습니다.

▲평면(2D)으로 펼쳤던 셀(cell)을 수직으로 쌓는 기술을 적용한 3D 낸드플래시는 미세공정의 한계를 극복하고 용량을 빠르게 끌어올릴 수 있게 되었다.

먼저 공정 측면에서는 수직 적층이 핵심입니다. 기존 반도체가 1층짜리 주택이라면 96단 3D 낸드는 96층짜리 아파트라고 이해하면 됩니다. 적은 전력으로 동작 속도가 빠르고 수명도 오래가죠. 3차원은 2차원과 비교해 동일한 면적에서 더 많은 셀을 저장할 수 있어 원가절감에 유리하다는 강점이 있습니다.

두 번째로는 사용하는 물질입니다. 전하를 저장하는 게이트 형태를 기존 플로팅게이트(Floating Gate, FG)에서 차지 트랩 플래시(Charge Trap Flash, CTF)로 바꾼 것이 핵심입니다. 기존 플로팅게이트는 ‘폴리실리콘’에 전하를 저장했지만, CTF에서는 ‘나이트라이드’라는 부도체에 전하를 저장합니다. 나이트라이드가 전하를 붙잡고 있는 힘이 강해서 누설전류를 줄이는 장점이 있습니다. 이러한 CTF 기술은 1971년 비휘발성 메모리가 처음 개발된 이래 35년간 상용화에 적용돼온 ‘플로팅 게이트’ 기술의 한계를 극복한 혁신적인 기술로 꼽히고 있습니다.

마지막 세 번째는 ‘소자 구조’입니다. 기존 평면형 구조를 벗어나 3차원의 원통형 적층으로 구조가 바뀌면서 셀을 구성하는 채널도 게이트에 의해 손으로 쥐어싸듯 감싸지는 구조가 됐습니다. 이를 전문용어로 GAA(Gate-All-Around) 구조라고 합니다. 96단 낸드의 경우 먼저 전류가 흐르는 도체와 전류가 흐르지 않는 부도체를 순서대로 각각 96개(도체·부도체 한 쌍이 1단)를 쌓아올립니다. 그다음 통조림 파인애플처럼 위에서 아래로 구멍을 뚫고(에칭 공정), 그 구멍을 측벽부터 순차적으로 셀을 구성하는 물질로 발라 메우는 작업을 합니다.

이렇게 해서 만들어진 원통 셀 하나가 0, 1 이진법으로 표시되는 기억단위 하나가 됩니다. 이러한 셀들이 수억 개 모여서 특정한 저장용량을 가진 하나의 칩이 되는 것이죠.

차세대 기술 개발의 장벽

앞으로 반도체 업계는 적층에 따른 기술적 문제를 해결하는 것이 관건입니다. 기술이 진화한다 해도 양산시 수익을 낼 수 있을 정도로 효율이 받쳐주어야 하기 때문이죠. D램과 마찬가지로 낸드플래시도 경제적 이유로 스케일링(미세화)의 한계가 올 것이며, 이를 극복하는 혁신기술에 낸드플래시의 성패가 달려있다고 합니다.

우선 200단에 근접하게 되면 완전히 새로운 기술적 돌파구가 필요해집니다. 낸드플래시의 스택(stack) 수가 높아지면 스트레스가 증가하는 등 부정적 영향이 발생하기 때문입니다. 200단 근처가 되면 양산시 수익을 내기 어려울 정도가 될 것이란 게 대체적인 전망입니다. 이를 위해 반도체 업계에서는 적층 단수가 올라갈수록 생기는 ‘High Aspect ratio’ 이슈와 그에 따라 쌓아올릴수록 구조가 휘는 문제, 각 층의 천정 높이를 낮춰야 하는 문제 등 여러 기술적 한계를 보완해야 할 것입니다.

이렇듯 혁신기술로 평가받는 96단 4D 낸드플래시 그 이후에도 넘어야 할 장벽이 무수히 존재합니다. 2D에서 3D로, 그리고 지금의 4D에 이르기까지 반도체 기술은 수많은 한계를 극복하며 진화를 거듭해왔습니다. 낸드플래시 업계의 승기는 이 같은 기술적 난제를 가장 먼저 해결하는 기업이 잡을 것으로 전망됩니다.

※ 본 칼럼은 반도체/ICT에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.