AI(인공지능)의 활용이 확대되면서 데이터센터를 비롯해 AI 서버 등에서는 차세대 메모리 제품 수요가 늘어나고 있다. 차세대 메모리 제품은 고용량, 고속 연산, 고성능, 저전력의 특성이 있으며, SK하이닉스를 비롯한 세계적인 메모리 기업들은 역동적이고 혁신적인 차세대 메모리 제품을 개발하며 선의의 경쟁을 펼치고 있다. 특히 SK하이닉스는 D램과 낸드플래시(NAND Flash, 이하 낸드) 두 분야에서 최고 수준의 기술 경쟁력을 갖추고 있는데, 이는 지난 2년간 메모리 가격이 내려갔음에도 불구하고 과감한 R&D 투자와 기술개발을 위한 노력이 있었기에 가능한 결과라고 생각한다. 이번 기고문을 통해 2편에 걸쳐, D램과 낸드의 기술 동향을 살펴보고 도전적인 과제와 전망도 함께 이야기할 예정이다.

낸드플래시의 기술 동향과 전망

스토리지(Storage) 향(向) 낸드 제품, 특히 3D 낸드 제품 영역에서는 SK하이닉스를 비롯한 주요 업체들이 경쟁에 참여하고 있다. 현재까지 낸드 기업들에 의해 상용화된 3D 낸드 제품들은 대부분 128단, 176단, 232단 TLC* 및 QLC* 제품이며, 낸드 칩당 메모리 용량은 현재 512Gb(기가비트)와 1Tb(테라비트)(또는 1.3Tb)가 주를 이루고 있고, SK하이닉스는 이미 차세대 제품인 321단 4D PUC 제품 칩을 FMS 2023에서 공개한 바 있다[관련기사]. 321단 제품의 경우, 셀렉터(Selector)로 사용되는 게이트(Gate)들과 패싱 게이트(Passing Gate)들을 합친다면 한 개의 수직 스트링*에 구성된 실제 총 게이트 수는 340개를 넘을 것으로 예상된다.

* TLC(Triple Level Cell, 트리플 레벨 셀): 낸드플래시 메모리의 한 형태로서 메모리 셀당 최대 3비트의 데이터를 저장할 수 있다.

* QLC(Quad Level Cell, 쿼드 레벨 셀): 낸드플래시 메모리의 한 형태로서 메모리 셀당 최대 4비트의 데이터를 저장할 수 있다.

* 스트링(String): 3D 낸드 구조에서 한 개의 수직 스트링은 여러 개의 워드라인들, 소스와 드레인 영역 부근의 셀렉트 트랜지스터들, 그리고 몇 개의 더미 또는 패싱 게이트들로 구성된다.

낸드의 경우, 불과 10여 년 전까지도 14nm~16nm 기술을 적용한 2D 낸드 제품이 시장의 주를 이뤘다. 쿼드러플 패터닝 기술*과 에어갭* 등의 새로운 기술이 개발되고 적용됐음에도 불구하고, 비트(bit) 밀도 증가의 어려움, 공정 결함 증가, 셀 간섭(Interference) 증가 등의 이유로 인해 혁신적인 성능 향상이 어려웠다. 이에 GAA* 셀 타입을 갖는 3차원 구조로 전환하면서 SK하이닉스를 비롯한 여러 낸드 기업들은 CTN*을 기반으로 하는 3D 낸드 제품을 상용화했다.

* 쿼드러플 패터닝 기술: 단일 노광 공정으로 만들기 힘든 미세선폭의 패턴을 여러 번의 노광 공정, 박막 증착 공정, 식각 공정 기술을 추가 활용해 패턴 형성을 하는 것을 멀티 패터닝(Multi-Patterning)이라고 하는데, 한 번만 추가 활용할 경우에 이를 더블 패터닝(Double Pattering Technology, DPT)이라고 부르며, 더블 패터닝을 한번 더 반복할 경우 쿼드러플 패터닝(Quadruple Patterning Technology, QPT)이라고 부른다.

* 에어갭(Air-Gap): 회로와 회로 사이에 절연 물질이 아닌 빈 공간(Air)으로 절연층을 형성하는 기술

* GAA(Gate-All-Around): 반도체 미세화 한계 극복을 위해 도입한 기술로, 3나노 이하 초미세 회로에 도입될 트랜지스터(전류 흐름을 증폭하거나 스위치 하는 역할) 구조다.

* CTN(Charge Trap Nitride): 전하 포획 물질로 플로팅 게이트와 같이 3D 낸드에서 데이터를 저장하는 물질

반면, 플로팅 게이트* 기반의 3D 낸드를 CMOS-under-Array(CuA) 구조로 상용화한 낸드 기업들도 있었다. 이외에도 여러 연구소, 대학교, 장비회사들은 VRAT, VSAT, VCSTAR 등 여러 가지 다양한 3D 낸드 구조를 제안하기도 했다. 이런 수많은 기술 개발 끝에 현재 상용화된 기술들은 ▲BiCS* ▲P-BiCS* ▲T-CAT V-NAND* ▲FG-CuA* ▲Xtacking* 등이며, CuA 개념이 접목된 ▲CoP*와 ▲4D PUC* 등의 기술이 최근 TLC 및 QLC 제품군에 적용되고 있다. SK하이닉스의 경우, 96단 낸드 제품부터 4D PUC를 적용했다.

* 플로팅 게이트(Floating Gate, FG): 전원이 꺼져도 전자의 값을 보관할 수 있는 공간으로 이후 플래시 메모리에 적용된다.

* BiCS(Bit Cost Scalable): 도시바 메모리와 샌디스크에서 제안한 3차원 낸드 구조

* P-BiCS(Pipe-Bit Cost Scalable): BiCS 구조의 하부에 Pipe(도관) 형태의 연결 게이트를 형성해 낸드 스트링을 서로 연결해 주는 3차원 낸드 구조

* T-CAT V-NAND(Terabit Cell Array Transistor Vertical NAND): 삼성전자가 제안한 3차원 낸드 구조

* FG-CuA: Poly-Si(폴리-실리콘) 전하 저장체를 활용한 낸드 셀 어레이 아래에 CMOS 주변회로를 형성한(CMOS under Array) 3차원 낸드 구조

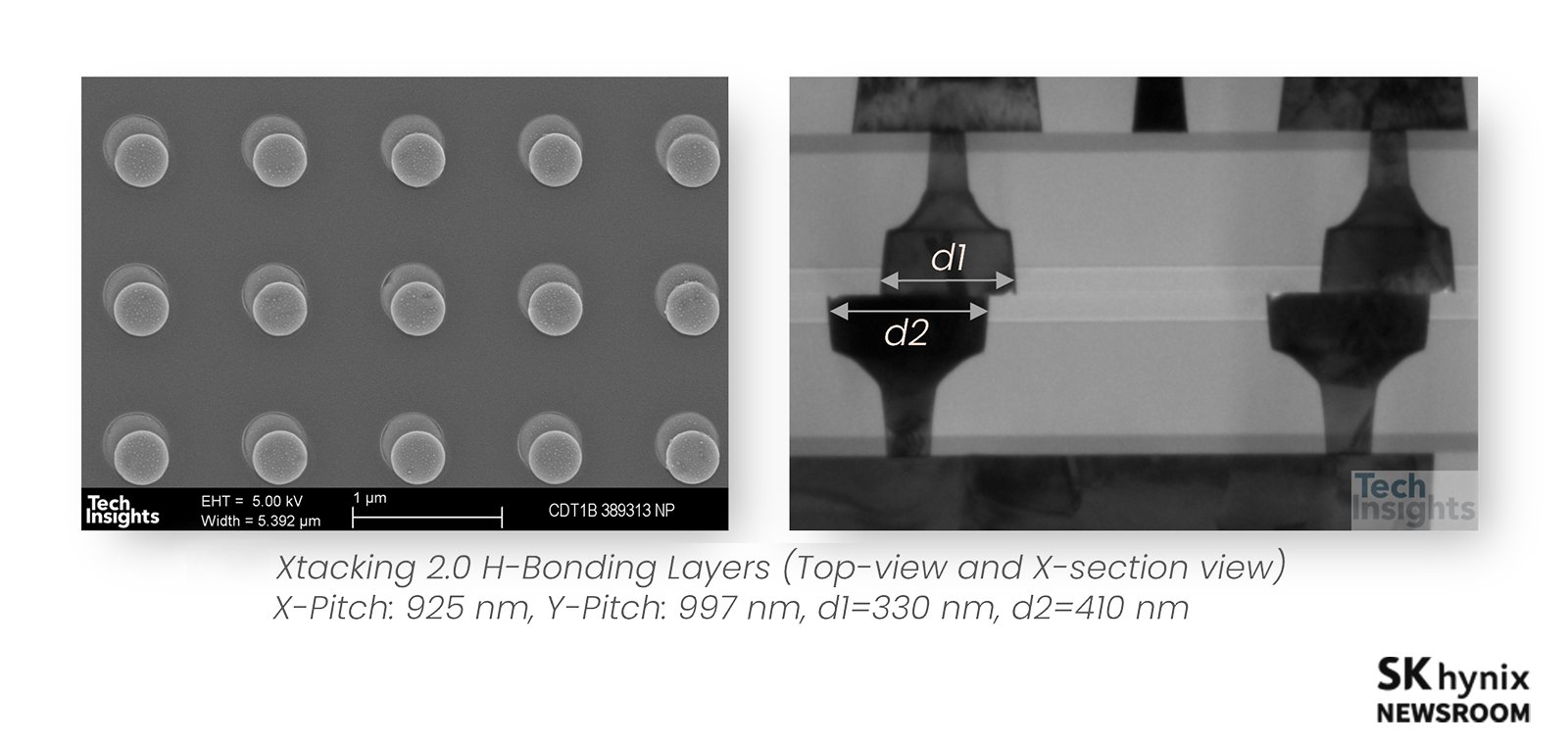

* Xtacking: 중국 업체에서 자체 개발한 낸드 제품에 적용 중인 웨이퍼 본딩 기술이며 하이브리드 본딩 기술을 활용하고 있다.

* CoP(Cell array-on-Periphery): 셀의 제어를 담당하는 주변회로를 데이터 셀 어레이 아래에 배치해 표면적을 줄이는 기술

* PUC(Peri Under Cell): 셀 영역 하부에 셀 작동을 관장하는 주변회로(Peri.)를 배치해 전체 면적을 줄이고 적층 수를 늘리는 기술

162단에서 처음으로 CuA 개념을 적용한 한 업체는 218단 조기 개발에 주력하고 있다. 특히 이 제품은 하이브리드 본딩 기술을 처음으로 적용하는 제품(CMOS Bonded Array, CBA)인 만큼 고용량, 고집적, 고성능, 저비용 등의 여러 시도가 이뤄지고 있다.

상용화된 3D 낸드를 살펴보면, 전반적으로 비트 밀도는 200대 단 TLC 기준 15~16Gb/mm2, QLC 기준 19~20Gb/mm2 수준까지 도달했다. 워드라인 수직 방향 선폭(Pitch)은 지속적으로 감소해 일부 제품에서는 이미 최소 구간에서 42~43nm까지 감소했다. 이에 더해 일부 업체들은 Deck* 사이의 두꺼운 버퍼 레이어를 제거함으로써 공정 효율성과 제품의 성능을 개선했다.

* Deck: 3차원 낸드 구조 형성 시에 단수가 높아짐에 따라 한 번에 수십, 수백 단을 형성하기 어려우므로 이를 두 차례 또는 그 이상으로 나누어 구조를 형성하는 공정을 활용한다. 이 경우 여러 개의 Deck이 낸드 셀 어레이를 형성해 적층 모양을 갖게 된다. 통상적으로 한 개의 Deck은 48~128개의 수직 낸드 셀로 구성돼 있다.

▲ 그림 1: 하이브리드 본딩 기술이 적용된 3D 낸드 제품의 예시 ‘Xtacking 본딩 영역’ (출처: TechInsights Report AME-2304-801 published on July 17, 2023)

향후 3D 낸드의 경우에도 D램과 마찬가지로 하이브리드 본딩 기술이 적용 및 확대될 것으로 예상된다. SK하이닉스를 비롯한 주요 낸드 기업들은 현재 하이브리드 본딩 공정 기술을 평가하고 있는 상황이며, 업체별로 하이브리드 본딩 공정을 적용해 Gen2(Xtacking 1.0, 64단) 이후부터 현재의 Gen4 232단 Xtacking 3.0까지 양산하거나, 218단부터 하이브리드 본딩 공정을 적용한 3D 낸드 CBA 구조를 출시한다는 계획이다.

3D 낸드의 단수는 현재의 200~300단 수준에서 향후 수년 내에 500~600단의 제품이 개발될 것으로 보이며, 이 경우, TLC 칩 기준으로 2Tb 다이(Die)가 주요 제품군이 될 것으로 예상된다. 하지만, 여러 가지 도전 과제들 역시 만만치 않다. ▲스트링/셀 전류(Cell Current) 확보 ▲HARC* 장비/공정 개발 ▲극저온 에칭* 적용 확대, ▲Carrier Mobility* 증가 ▲Stress/Warpage 보상 공정* ▲무결점 하이브리드 본딩* 기술 ▲X-&Y- 셀 미세화* ▲Multi-Bonded 낸드* 기술 확보 ▲CMOS/Peripheral Area Scaling* 등의 과제 해결을 위한 노력이 지속돼야 한다.

* HARC(High Aspect Ratio Contact): 높은 종횡비를 갖는 컨택을 의미하며 특히 단수가 증가한 3차원 낸드의 경우에는 종횡비가 50 이상으로 매우 높아서 식각 공정 및 증착 공정에서 높은 종횡비를 감안한 공정 및 장비가 필요하다.

* 극저온 에칭: 저온 또는 극저온 식각장비를 의미하며 공정 온도가 낮아질수록 특히 극저온 상태로 갈수록 높은 종횡비를 갖는 컨택 공정에 유리하다.

* Carrier Mobility: 전류는 곧 전자의 흐름이므로 전자(캐리어)의 이동도를 증가시켜 주는 것이 셀 전류를 확보하는 방법의 하나가 될 수 있다.

* Stress/Warpage 보상 공정: 3차원 낸드 구조 형성 공정 시에 단수가 증가함에 따라 옥사이드와 나이트라이드 막질 증착 증가로 인한 막질 스트레스 증가와 이에 따른 웨이퍼의 휨(Warpage) 현상이 나타나게 되는데 이를 개선하는 공정이다.

* 무결점(Defect-Free) 하이브리드 본딩: 반도체 웨이퍼 또는 반도체 칩을 본딩하는 경우, Cu(구리) 배선 공정과 평탄화 그리고 열처리 기술을 접목하여 사용하는데, 배선 패턴의 높낮이 및 돌출 정도, 평탄화 공정 조건에 따라 발생할 수 있는 미세 동공 등의 결함을 없애는 기술이다.

* X-&Y- 셀 미세화: X-축 및 Y-축 방향으로의 미세화

* Multi-Bonded 낸드: 사용 가능한 웨이퍼 본딩(하이브리드 본딩) 기술을 확대해 여러 번의 낸드 셀 어레이 적층 또는 여러 장의 낸드 어레이 웨이퍼와 주변회로 웨이퍼를 본딩하는 기술이다.

* CMOS/Peripheral Area Scaling: 메모리의 주변회로에 필요한 트랜지스터들이 형성된 영역을 더욱 미세화하기 위한 노력을 의미한다.

지금까지, D램과 낸드플래시로 대표되는 메모리 시장의 동향을 함께 살펴봤다. 누군가는 메모리의 중요성을 간과하기도 한다. 하지만 메모리 없이는 어떠한 반도체 제품의 미래도 없다. 미래를 상징하는 AI, 사물인터넷(IoT), 클라우드, 메타버스, 게임, 자율주행, 우주 산업, 무인 의료 서비스 등 모든 분야는 메모리 기술의 발전이 없이는 이룰 수 없는 것들이다. 지금까지도 잘해 왔지만, 다가올 미래에 획기적인 기술 혁신을 위해, 메모리 강국 대한민국의 SK하이닉스와 같은 기업이 모든 영역에서 리더십을 발휘하기를 바란다.