낸드플래시는 대표적인 비(非)휘발성 메모리입니다. 반대로 D램은 휘발성 메모리고요. 말 그대로 전원이 꺼졌을 때 데이터를 날리지 않고 저장할 수 있느냐 없느냐의 차이죠. 서로 다른 두 메모리는 공통점도 있습니다. 바로 성능을 높이기 위해 3차원(3D) 기술을 활용했다는 사실입니다. D램은 커패시터, 낸드플래시의 경우 셀(Cell)을 평면(2D)이 아닌 수직으로 쌓아 용량을 늘립니다. 3D라는 관점에서 바라보면 낸드플래시는 D램보다 훨씬 빠르게 발전하고 있습니다. 반도체 집적회로의 성능이 24개월마다 2배로 증가한다는 ‘무어의 법칙’을 스스로 증명하고 있다는 생각마저 듭니다. 물론 언젠가 한계에 다다르겠지만 지금은 아닙니다. ‘더블스태킹(Double Stacking)’ 혹은 ‘멀티 티어(Multi Tiers)’로 부르는 다(多)층 구조가 등장한 덕분입니다.

빅데이터 시대, 3D 낸드플래시의 필요성

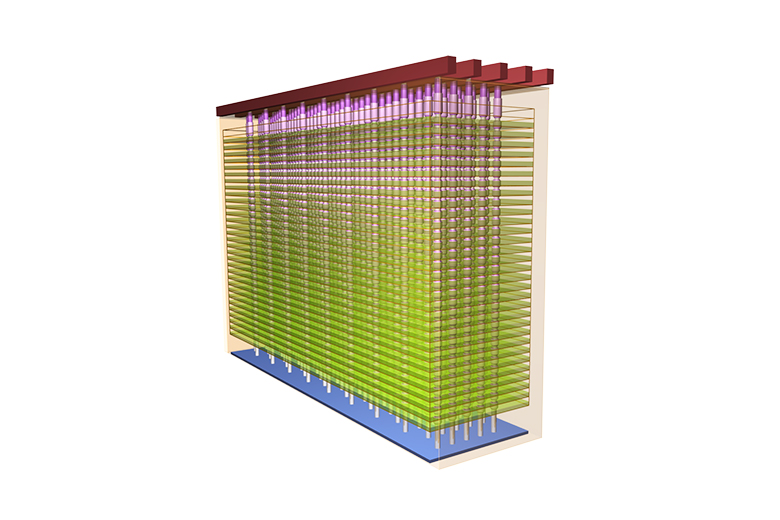

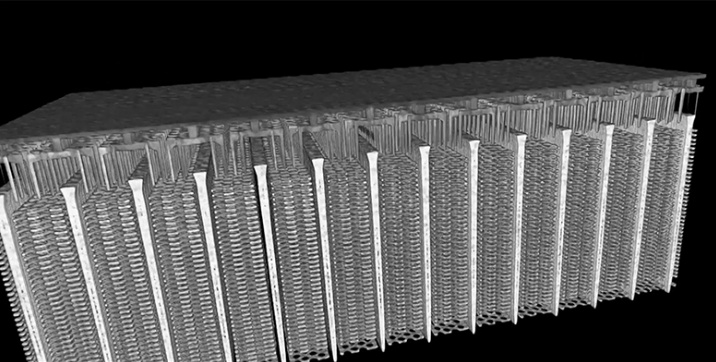

▲ 3D 낸드플래시 내부 구조는 마치 건물의 뼈대와 비슷하다.

잘 알려진 것처럼 3D 낸드플래시는 2D로 펼쳤던 셀을 수직으로 쌓는 기술을 활용한 제품입니다. 덕분에 미세공정의 한계를 극복하고 용량을 빠르게 끌어올릴 수 있었습니다. 우스갯소리로 ‘다다익램’이라는 말이 있습니다. 많으면 많을수록 좋다는 뜻의 ‘다다익선(多多益善)’과 램(RAM)의 합성어죠. 메모리는 클수록 좋다는 의미입니다.

특히 낸드플래시는 쓰임새가 D램과 같은 주메모리가 아닌, 하드디스크드라이브(HDD)와 같은 보조저장장치라는 점을 떠올려야 합니다. 오래 전 컴퓨터는 보조저장장치로 펀치카드(천공카드)와 같은 종이를 사용했습니다.

광학 마크 인식(Optical Mark Recognition, Optical Mark Reading, OMR)카드와 같다고 보면 됩니다. 시기나 종류에 따라 조금씩 차이는 있지만 보통 80자를 횡렬(가로)로 입력할 수 있었는데, 종렬(세로)이 10줄이라면 800비트(Bit)를 저장할 수 있었죠. 바이트(Byte)로 바꾸면 100, 메가바이트(MB)로는 0.000095입니다. 당시는 이 정도로도 충분했죠.

이제는 온갖 빅데이터가 넘쳐납니다. 그래서 보조저장장치 용량이 클수록 좋습니다. 아무리 클라우드와 같은 수단이 발달한다고 해도 스마트폰, PC에 직접 저장해놓고 콘텐츠를 즐기는 게 가장 편리합니다. 낸드플래시 용량이 커져야 하는 이유가 바로 여기에 있죠.

CTF로 한계를 극복하다

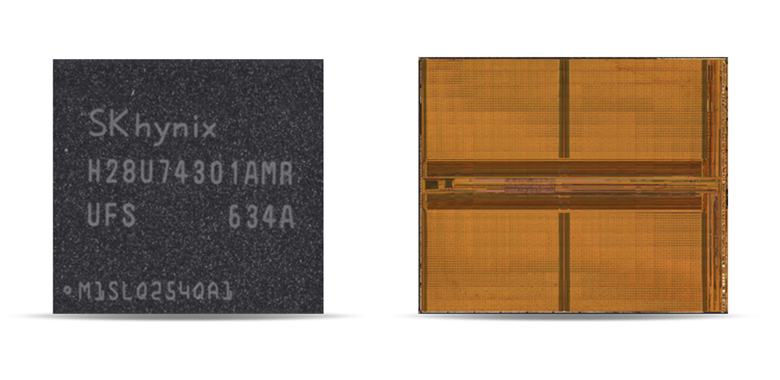

▲ 다층 구조를 통해 용량의 한계를 극복할 수 있다

3D 기술이 본격적으로 활용되면서 메모리 업계는 마치 성경의 바벨탑처럼 셀을 어떻게 하면 효율적으로 높게 쌓을 수 있을까를 고민합니다. 현재 SK하이닉스는 셀에 전하를 저장하는 게이트의 설계로 ‘차지 트랩 플래시(Charge Trap Flash, CTF)’를 사용합니다. CTF는 부도체에 전하를 저장토록 함으로써 셀과 셀 사이의 간섭 현상을 줄이고 간격을 좁힐 수 있다는 장점이 있습니다.

또한, 셀을 적층할 수 있도록 3차원 방식(원통형)으로 구조를 변경하고 드라이 에칭 기술도 사용합니다. ‘채널 홀 에칭(Channel Hole Etching)’이라고도 부르는 드라이 에칭은 메모리칩을 쌓고 수십억 개의 홀(구멍)을 뚫는 에칭(etching, 식각) 과정을 거친 후 이 속에 원통형 셀을 적층해 배치합니다. 셀을 묶은 어레이를 제어하기 위한 컨트롤 회로를 주변에 반드시 수평적으로 배치해야 하는 어려움이 있지만, 3D 낸드플래시의 성능을 높일 수 있는 좋은 방법입니다.

SK하이닉스는 지난 2010년 열렸던 국제전자소자미팅(International Electron Device Meeting, IEDM)까지만 하더라도 마이크론·인텔이 사용하고 있는 ‘플로팅게이트(Floating Gate, FG)’ 기반의 설계를 적용했습니다. CTF를 사용한 것은 향후 적층수를 높이기 위해서는 FG보다 유리하다고 판단한 것으로 보입니다. 따지고 보면 FG보다는 CTF를 사용하는 업체가 더 많습니다. 재료나 인터페이스 구현, 셀 어레이의 설계에는 조금씩 차이가 있지만요.

72단 넘어서 96단 노리는 SK하이닉스

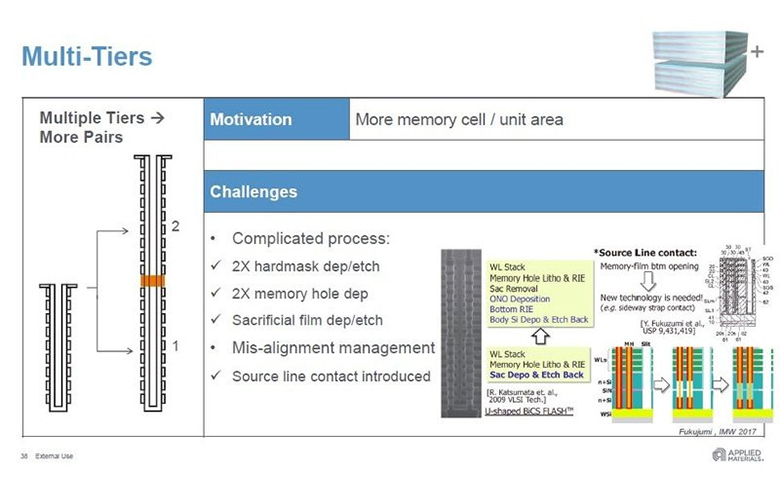

▲ SK하이닉스 72단 3D 낸드플래시는 ‘36×2’의 구조로 이루어져 있다.

반도체 기업은 제품을 어떻게 만드는지 구체적으로 밝히지 않습니다. 당연히 영업비밀입니다. SK하이닉스도 마찬가지지만, 미루어 유추하면 질화규소막(Si3N4)과 CTF를 통해 48단까지 개발하는 데 성공한 것으로 보입니다. 그렇다면 가장 최신인 72단은 어떨까요. 재미있게도 36단을 2개 이어붙여 구성했습니다.

어째서 64단이 아닌 72단을 내놨을까요. 그 이유는 5세대로 분류되는 96단(48×2개)이 오랫동안 사용될 가능성이 크기 때문으로 풀이됩니다. 시스템 반도체 미세공정으로 예를 들어보겠습니다. 지금까지 상용화된 애플리케이션 프로세서(AP) 가운데 가장 최신 공정은 10나노입니다. 올해 7/8나노가 예정되어 있습니다. 역사를 되짚어 보았을 때는 14/28나노가 정말 오랫동안 쓰였습니다.

3D 낸드플래시도 같은 맥락으로 이해하면 됩니다. 32/36단에서 48단까지는 빠르게 발전했습니다. 업체에 따라 차이는 있지만 48단이 주력이고 이후에 64/72단이 등장해 시장에 보급됐죠. 여기까지 걸린 시간을 따져보면 96단은 상당히 오랫동안 사용될 것으로 예상합니다. 아마도 SK하이닉스는 거의 비슷한 시기에 72단과 96단의 연구개발을 시작했을 겁니다. 96단은 48단을 2개 연결한 제품이기 때문입니다.

설계와 재료의 발전 속도로 보면 100단 이상의 제품은 한 번에 구멍을 뚫어 만들기가 쉽지 않습니다. 그래서 3D 낸드플래시는 96단에서 잠시 주춤거릴 수 있습니다. 이후에는 적층 속도를 상당히 빨리 높일 수 있으나, 적어도 2020년까지는 쉽지 않습니다. 마이크론·인텔이 만드는 96단은 32단을 3개 사용했을 정도입니다.

▲ 단수가 높아질수록 WL, 절연 박막의 층을 얇게 만들면서도 셀의 정렬할 때 정밀도가 높아져야 한다.

계속해서 4개, 5개 이상을 붙이면 좋겠지만 시간과 돈이 많이 들어가므로 무작정 더블스태킹·멀티 티어 구조를 이용할 수 없습니다. 더불어 데이터를 읽고 쓰는 작업에 사용되는 워드라인(WL), 절연 박막의 층을 얇게 만들면서도 셀을 정렬할 때 정밀도를 한층 높여야 합니다.

따라서 96단 이후의 초고적층 3D 낸드플래시를 만들려면 64단 이상을 한 번에 뚫어 연결할 수 있는 기술이 필수적입니다. 그런데 SK하이닉스는 64단 제품이 없습니다. 다음 단계는 96단을 36/48단 제품처럼 만들 수 있어야 한다는 계산이 나옵니다. 당장은 아니지만 2021년, 혹은 2022년이면 어느 정도 성과가 나오지 않을까 생각됩니다.

4차 산업혁명 시대에는 온갖 데이터가 넘칩니다. 자율주행차는 1시간 동안 2테라바이트(TB) 이상의 데이터를 만들어냅니다. 네트워크 기업 시스코에 따르면 2016년 기준으로 클라우드 데이터센터의 트래픽은 6제타바이트(ZB)라고 합니다. 1ZB는 1000엑사바이트(EB)이고, 1EB는 104만8576TB입니다. 2021년의 트래픽은 19.5ZB라고 하니 가늠이 안 갈 정도로 엄청난 양의 데이터가 만들어지고 있는 셈입니다. 이런 데이터는 어딘가에 저장되어야 합니다. 이미 HDD는 1개의 제품에 용량 100TB의 시대를 시작했습니다. 앞으로 3D 낸드플래시의 용량이 얼마나 커질 수 있을지 궁금해집니다.

※ 본 칼럼은 반도체/ICT에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.