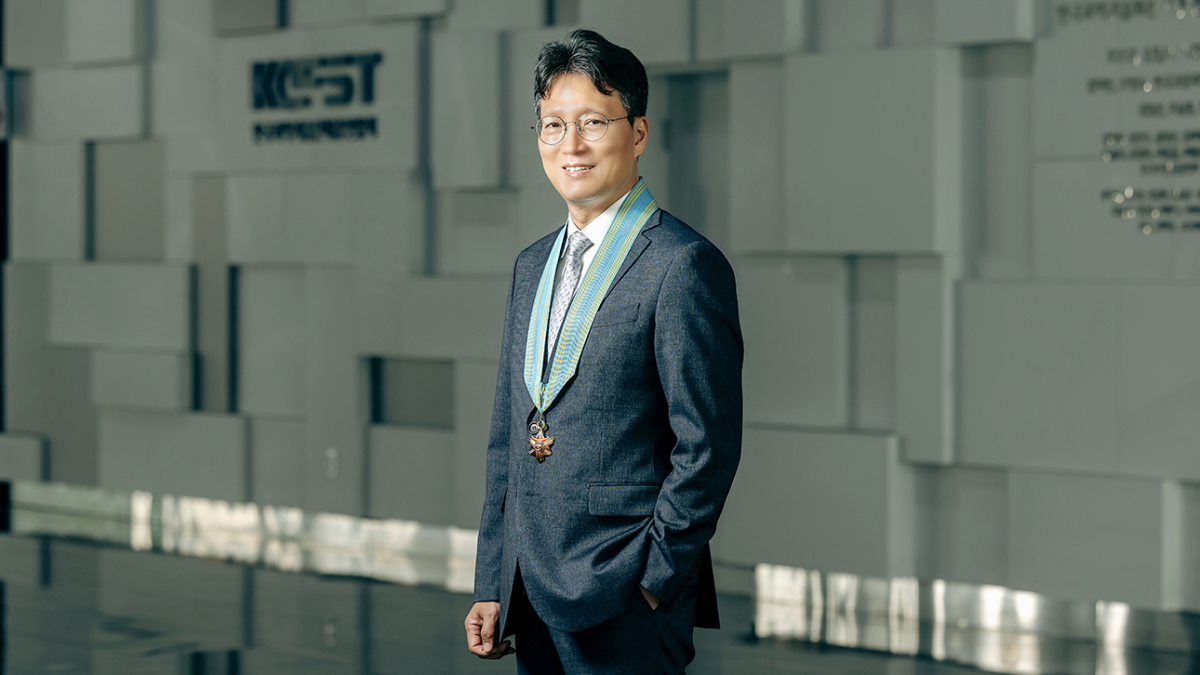

▲ 좌측부터 한국마이크론전자 및 패키징학회 강사윤 학회장, 학술부문 수상자 한국생산기술연구원 고용호 수석연구원, 기술부문 수상자 SK하이닉스 손호영 팀장, 해동과학문화재단 김영재 이사장

“이번 수상은 결코 혼자 받은 상이 아니라고 생각합니다. 기술 개발을 위해 함께 달려온 모든 구성원들께 감사하다는 말씀을 드리고 싶습니다. 지금까지의 영광을 넘어, 새로운 패키지를 개발하는 선행 연구·개발의 관점에서 계속해서 도전하며 세상을 놀라게 하고 싶습니다.”

지난 10월 26일 SK하이닉스 P&T(Package&Test) 손호영 팀장이 제14회 해동젊은공학인상* ‘기술부문’을 수상했다. 이 상은 대덕전자 창업주 고(故) 김정식 회장이 반도체 패키징 분야 기술 발전에 기여한 젊은 공학인을 격려하기 위해 제정한 상으로, 한국마이크로전자 및 패키징학회(KMEPS)에서 주관한다.

* 해동젊은공학인상: 대덕전자 창업주 고(故) 김정식 회장이 설립한 해동과학문화재단이 제정한 상이며, 사단법인 한국마이크로전자 및 패키징학회 주관으로 2006년 1회 시상을 시작했다. 2020년부터 학술상과 기술상을 구분하여 시상하고 있다.

손 팀장은 회사의 3차원 실리콘관통전극(TSV)* 기술 도입 초기부터 주요 기술 개발을 리드하며, 고용량·고사양 메모리 패키지의 핵심 기술을 완성하는 데 기여했다. 특히, 세계 최초로 멀티 칩 스태킹(Multi Chip Stacking) 구조에 MR-MUF* 기술을 도입했고, HBM* 제품 개발에 주도적인 역할을 했다. 어드밴스드 패키징(Advanced Packaging) 분야 최고의 기술 전문가로 인정받는 그는 현재 차세대 패키지 기술 개발 전반을 이끌고 있다.

* TSV(Through Silicon Via): D램 칩에 수천 개의 미세 구멍을 뚫어 상하층 칩의 구멍을 수직 관통하는 전극으로 연결하는 기술

* MR-MUF(Mass Reflow-Molded UnderFill): 적층한 칩 사이에 보호재를 넣은 후 전체를 한번에 굳히는 공정으로, 칩을 하나씩 쌓을 때마다 필름형 소재를 깔아주는 방식 대비 공정이 효율적이고, 열 방출에도 효과적인 공정으로 평가받음

* HBM(High Bandwidth Memory): 여러 개의 D램 칩을 TSV(Through Silicon Via)로 수직 연결해 데이터 처리 속도를 혁신적으로 끌어올린 고부가가치, 고성능 제품. HBM은 1세대(HBM)-2세대(HBM2)-3세대(HBM2E)-4세대(HBM3)를 거쳐 현재 5세대(HBM3E)까지 개발됨. HBM3E는 HBM3의 확장(Extended) 버전

뉴스룸은 손 팀장을 만나 패키지 기술 개발 공적과 회사 미래 경쟁력의 기반인 어드밴스드 패키징 기술 개발 비전에 관해 들어보았다.

패키지 기술 개발로 ‘혁신의 기반’을 닦다

손호영 팀장은 1세대 HBM 개발 초기부터 프로젝트에 참여, 세계 최초로 HBM 개발에 성공하며 현재 HBM3와 HBM3E가 AI 메모리 대표 제품으로 부상하는 데 기여한 주역이다.

손 팀장은 “업계 최고의 기술력으로 인정받고 있는 HBM은 기존에 없던 혁신적인 제품이었기 때문에, 개발 당시 기준으로 삼을 데이터도 존재하지 않았다”며 “제품을 개발하고, 표준 스펙을 만들어 인증하는 모든 과정이 무에서 유를 창조하는 일이나 다름없었다”고 회상했다.

그는 “TSV는 HBM 개발 착수 이전에 고용량 메모리 애플리케이션을 개발하며 계속 연구했던 기술”이라며 “그때의 연구 결과가 있었기에, 비록 시행착오는 겪었지만 결국 HBM 제품화에 성공할 수 있었다”고 말했다. 손 팀장은 ‘기술의 진화’는 성공을 바탕으로 이루어지는 일이지만, 성공은 결국 모든 실패한 경험들이 긍정적으로 쌓여 완성된다는 자신만의 소신을 밝혔다.

“TSV뿐만 아니라 MR-MUF 공법 역시 이전에 계속 연구해 왔던 기술입니다. 물론, HBM과 같이 얇은 두께의 칩에 이 공법을 적용한 경우는 어디에도 없었습니다. 당사가 기술 우위를 점할 수 있었던 것은 지난 경험을 담보로 성공 의지를 다지며 도전했기 때문입니다.”

손 팀장은 계속해서 선행 기술 연구·개발에 매진하고 있다. 그는 최근 업계 최초로 모바일용 팬아웃 WLP(Fan-out WLP)* 기술인 VFO* 기술을 제안하며 또 다른 혁신의 시작을 알렸다. 팬아웃 WLP는 본래 메모리 반도체에 적합하지 않다고 여겨지던 기술이지만, 손 팀장은 고정관념을 깨고 모바일 메모리에 응용하여 한계를 돌파한 것이다.[관련기사] 그는 “VFO 기술로 기판(Substrate)을 없애 더 얇은 패키지를 구현했고, 전력 효율과 발열 문제도 개선했다”며 “이를 통해 향후 모바일 시장을 선도할 수 있는 혁신적인 메모리 제품을 선보일 것”이라고 자신감을 내비쳤다.

* 팬아웃 WLP(Fan Out Wafer Level Package): 기판(Substrate) 없이 칩 바깥 영역에 바로 데이터 출입(I/O) 단자를 붙여 반도체를 만드는 후공정 패키지 기술로 칩 사이즈를 혁신적으로 줄이고 저전력 구현이 가능함

* VFO(Vertical Fan-out): 곡선 와이어 본딩을 수직으로 연결해 소형화하고 발열 문제를 개선한 기술 [관련기사]

어드밴스드 패키징 기술 연구로 더 먼 미래를 준비할 것

손 팀장이 성공적으로 개발한 ‘최초의 기술’은 결국 회사를 넘어 대한민국의 기술 진화까지 이끌었다는 평가다. 그는 국내외 40여 편의 논문 발표와 30여 편의 특허 및 국제표준 출원, 국제 최고 권위의 패키징 관련 학회 분과위원 활동 등을 통해 대외에 회사의 기술력을 입증했고, 국가 경쟁력 향상에도 기여했다.

손 팀장의 눈은 계속 미래를 향하고 있다. 그는 “HBM이 지금보다 더 높은 대역폭과 더 큰 용량을 구현하기 위해서는 더 많은 칩을 쌓아야 한다”며 “언젠가는 현재의 기술도 한계가 올 것이기 때문에, 이를 위해 어드밴스드 패키징 기술인 ‘하이브리드 본딩(Hybrid bonding)*’을 적용하는 계획을 준비 중”이라고 말했다.

* 하이브리드 본딩(Hybrid bonding): 범프 없이 칩과 칩을 접착하고, 데이터 통로를 곧바로 연결하는 고도화된 본딩 기술

특히, 그는 현시점에서 가장 중요한 것은 ‘확장 가능성’이라고 언급했다.

“머지않아 시스템 반도체와 메모리 반도체의 관계 안에서도, 메모리 반도체 내부 기능 안에서도 모든 기능이 해체되고 다시 합쳐지는 이종 집적*이 일어날 것입니다. 그것을 구현하는 방식이 바로 어드밴스드 패키징 기술입니다. 이 기술에는 하이브리드 본딩을 이용한 수직 적층 방식이 있는가 하면, 수평으로 칩을 연결하는 팬아웃 방식을 활용한 이종 칩 집적이나 칩렛* 연결 방식 등이 있습니다. 이들은 모두 기존과는 전혀 다른 방식의 기술입니다. 우리는 고정관념을 깨고, 기능의 확장 가능성에 주목해야 합니다.”

* 이종 집적(Heterogeneous Integration): 기능과 역할이 다른 반도체를 결합하는 기술

* 칩렛(Chiplet): 각각의 기능이 있는 분할된 여러 개의 칩을 재조합하는 기술로 이종 칩 집적 패키징 기술을 수반하는 새로운 설계 방식

또, 손 팀장은 패키지 기술의 진화로 반도체 융합이 이루어지는 미래에는 반도체 업계 내 다양한 협력 구조가 더욱 중요해질 것이라고 강조했다. 제품 및 기술 개발 초기 단계에서부터 다양한 회사들과의 협업이 진행되어야 미래 방향성에 맞는 시너지를 낼 수 있기 때문이다.

그가 활발하게 대외 연구활동을 하는 것도 이런 협력과 시너지를 이루어내기 위한 것이다. 손 팀장은 “사실, 회사 업무와 동시에 학회 참여나 논문 발표 등의 활동을 진행하는 것이 쉽지만은 않았다”며 “하지만 선행 기술 연구에서도 대외 커뮤니케이션 활동과 네트워킹이 점점 중요해지는 만큼, 회사에서도 적극적으로 지원해 주고 개인적으로 동기부여도 가능했기에 최선을 다했다”고 말했다.

끝으로 그는 패키지 기술 연구를 통해 HBM 성공의 초석을 닦았던 것처럼, 미래 반도체의 성공 가능성을 열어주는 연구 문화를 끌어가겠다는 목표를 전했다.

“지금 하는 새로운 기술 연구가 성공할지, 실패할지 현재로서는 알 수 없습니다. 하지만 성공과 실패를 넘어, 미래 기술을 내다보는 SK하이닉스의 안목과 그에 걸맞은 우리의 도전은 멈추지 않고 계속 될 것입니다. 이러한 도전 의지를 후배들이 이어받아 가능성을 열어주면, 결국 미래에는 HBM보다 더 빛나는 제품이 개발되어 미래를 밝힐 것으로 확신합니다.”