32단, 48단, 72단… 반도체 관련 뉴스를 보다 보면 3D 낸드플래시 앞에 붙는 숫자가 점점 높아지고 있다는 걸 알 수 있습니다. 높은 적층 단수가 곧 기술력을 증명하는 척도가 되고 있는 듯한데요. 그렇다면 3D 낸드플래시는 무조건 높이 쌓을수록 좋은 것일까요? 왜 갈수록 층이 점점 높아지는 걸까요? 오늘 <궁금한 반도체 WHY> 2탄에서는 3D 낸드플래시의 적층 기술에 대한 궁금증을 파헤쳐 보도록 하겠습니다.

낸드플래시의 새 패러다임, 적층 기술

아파트는 20년 전만 해도 15층이 주를 이루었지만, 최근에는 50층 이상의 고층 아파트들이 증가하는 추세입니다. 같은 면적의 땅이라도 더 많은 집을 지을 수 있게 된 것이죠. 낸드플래시 역시 소자를 동일 면적에 수직으로 쌓아 올리면, 작은 칩(chip)에서도 고용량의 데이터 저장공간을 확보할 수 있게 됩니다.

이렇듯 3D 낸드플래시란 평면(2D)으로 펼쳤던 셀(cell)을 수직으로 쌓는 기술을 적용한 제품입니다. 덕분에 기존 미세공정의 한계를 극복하고 용량을 빠르게 끌어올릴 수 있게 되었죠.

과거 낸드플래시는 제한적인 면적에서 미세 구조의 셀을 제작하는 2D scaling을 중심으로 기술 개발이 진행되었습니다. 하지만 셀 간격이 좁아지면서 간섭 현상이 심화되고, 작은 소자 내 전자들을 저장하면서 전자 손실에 따른 셀 특성의 민감도가 높아진다는 문제점이 있었습니다.

이 같은 한계에 직면하면서 낸드플래시 기술은 새로운 패러다임을 맞게 됩니다. 수직 구조로 셀을 적층하는 방식이 떠오르게 된 것이죠. 인구가 증가하면서 주거형태가 단독주택에서 집을 적층하는 아파트로 변해가는 것과 동일한 현상으로 볼 수 있겠네요.

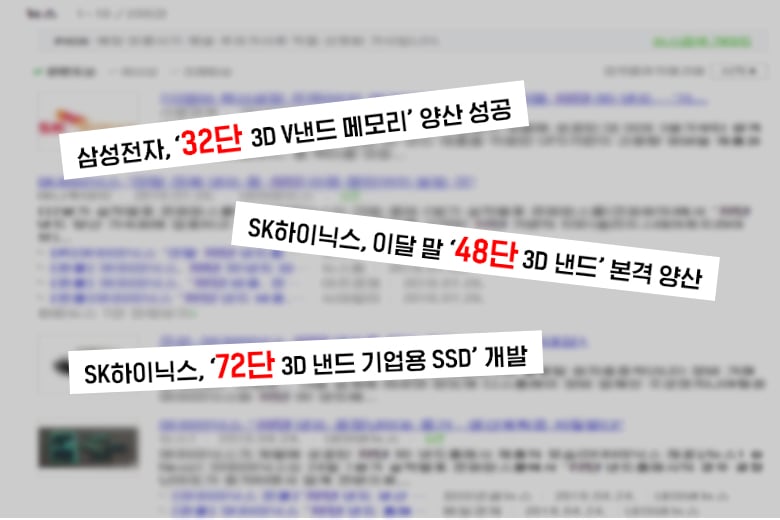

32단, 48단, 72단,… 3D 낸드플래시 단수의 비밀!?

뉴스를 보면 낸드플래시의 적층 수가 점점 높아지는 것들을 볼 수 있는데요. 여기서 궁금한 점이 하나 생깁니다. 3D 낸드플래시의 단수는 왜 8의 배수일까요? 50층이나 60층, 70층을 쌓을 수도 있을 텐데요.

메모리 용량을 결정하는 인자는 WL 적층수와 In/Out 단자 (3D NAND에서는 bit Line)입니다. 용량은 Byte 단위로 1Byte는 8bit 이기 때문에 8의 배수로 하나의 셀을 구성한 것으로 볼 수 있습니다. 또한 메모리 셀 내에 있는 Block안에는 String이라는 단위가 있고, 하나의 String에 몇 개의 Plug가 들어가는지에 따라 용량이 결정되기도 합니다.

3D 낸드플래시 초기에는 8의 배수로 적층되었습니다. 하지만 최근에는 plug 공정 기술 위주로 개발이 이뤄져 92단과 같은 적층수로도 양산되기도 하죠. 간단히 말해 8의 배수는 필수가 아닌 선택적인 요소이며, 적층수 결정의 기준은 plug etch 기술이라고 볼 수 있습니다.

고난이도 기술이 필요한 ‘층 쌓기’

반도체 소자를 원하는 만큼 높이 쌓을 수 있다면 더없이 좋겠지만, 이 과정에는 여러 가지 어려움이 따릅니다. 무엇보다 Plug 공정의 어려움이죠. Plug 공정은 Oxide/Nitride (ON Stack)을 겹겹이 쌓은 것을 뚫는 공정을 의미합니다. 먼저 적층 수를 증가시키려면 동일한 plug size로 더 깊은 plug를 뚫어야 한다는 고충이 있습니다. 이때 Plug 내부에 소자 동작을 위한 반도체 박막을 형성해야 하는데, 깊이가 깊을수록 균일한 박막의 두께와 형태를 확보하기 어려워집니다.

따라서 높이 적층할수록 고도화된 기술이 뒷받침돼야 합니다. 그리고 이는 결국 장비 개발이나 신물질을 필요로 하게 되고, 적층 구조에 의한 제조 원가 감소와 기술 고도화에 의한 원가 증가라는 문제가 상충됩니다.

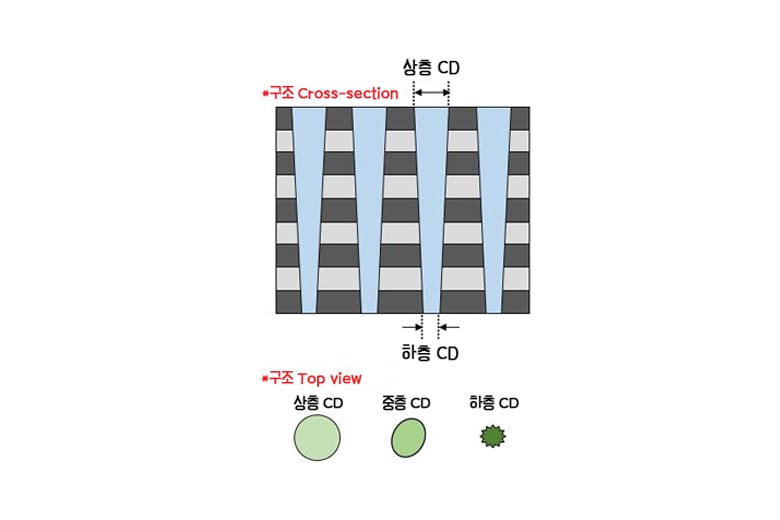

▲ Plug의 상/하층부 형태 변화 및 하부층의 스트레스 증가

두 번째는 소자 특성이 열화되는 문제입니다. 아무리 정교한 Etch 기술이어도 상층과 하층부 간에는 회로선폭(Critical Dimension, CD) 차이가 발생하게 되는데요. CD가 다르면 소자 동작이 어렵고 복잡해집니다. 그리고 소자 동작은 상층에서 하층 순으로 동작하는데, 이 경우 하층부 소자에 지속적인 전기적 신호 스트레스가 인가되어 의도치 않게 소자 상태에 변화가 생깁니다.

이 같은 기술적 어려움이 있기 때문에 3D 낸드플래시의 적층 수 선정은 기술적으로 다양한 검토가 필요합니다. 가장 중요한 요소는 무엇보다 ‘Plug etch를 안정적으로 할 수 있는가?’입니다. 3D 낸드플래시에서 중요한 적층 수 확보를 위해서는 Plug Etch를 비롯한 공정 요소 기술 개발과 원천적인 소자 기술의 이해가 더욱 중요하다고 볼 수 있습니다.

4차 산업혁명 시대, 적층 기술은 필수!

▲ SK하이닉스 72단 3D 낸드플래시는 ‘36×2’의 구조로 이루어져 있다.

영상 기술의 발전으로 고화질 미디어의 보급률이 높아지면서 자연스레 데이터의 크기도 증가하고 있습니다. 천문학적인 양의 데이터를 처리해야 하는 빅데이터 시대에서 저장 매체의 용량의 증대는 끊임없이 요구되고 있죠. 또한 적층 기술이 고도화될수록 다양한 파생 제품을 만들어낼 수 있기 때문에, 제조 기술 측면에서 적층 기술의 개발은 꼭 필요하답니다.

4차 산업혁명 시대에서 ‘황금알’이라 불리는 3D 낸드플래시, 그리고 이 3D 낸드플래시의 성장을 돕는 적층 기술은 우리 생활을 윤택하게 만들어주는 아주 중요한 기술이라고 할 수 있습니다.

오늘은 흔하게 접하지만, 자세히는 알지 못했던 3D 낸드플래시의 적층 기술에 대해 살펴보았는데요. 우리가 대용량 데이터를 저장하고, 초고화질 콘텐츠를 감상할 수 있었던 것에는 바로 이 적층 기술의 도움이 컸다는 것을 알 수 있었던 시간이었습니다. <궁금한 반도체 WHY> 시리즈는 반도체 관련 주제에 대한 여러분의 궁금증이 해소되는 그날까지 함께 합니다. 3탄도 많이 기대해주세요~!