현재 3D 낸드 메모리는 전하 포획 질화막(이하 CTN)*으로 알려진 실리콘 질화막에 전하를 가두어 데이터를 저장한다. 그러나 3D 구조의 CTN 낸드는 셀 간 간섭과 수직으로 인접한 셀 사이의 스페이서 산화물의 두께 때문에 셀을 적층해 메모리를 확장하는 데 한계가 있다. 업계에서는 이러한 한계를 극복하기 위해 3D CTN 낸드 기술의 대안을 모색했는데, 3D 구조의 강유전체* 낸드(이하 Fe-낸드)가 잠재적인 차세대 기술 중 하나로 떠올랐다.

이번 기고에서는 SK하이닉스 RTC*가 지난 6월 VLSI(Very Large-Scale Integration, 세계 3대 반도체 학회 중 하나) 심포지엄에서 발표한 연구 내용으로 강유전체 산화하프늄(HfO2)*을 활용해 3D Fe-낸드 트리플 레벨 셀(이하 TLC)* 동작을 처음으로 시연[관련기사]한 이후 업데이트된 최신 연구 내용으로 구성하였다. SK하이닉스 RTC는 3D 낸드 테스트 구조*를 활용하여 최초로 3D Fe-낸드 쿼드 레벨 셀*(이하 QLC)의 동작 가능성을 보여줬다.

* CTN(Charge Trap Nitride): 우선 Nitride(질화)는 질소(N)로 만들어진 화합물을 뜻함. Si3N4(실리콘 질화)로 예를 들면, 질소와 실리콘(규소)과의 화학 결합물을 의미함. 과거 2D 낸드는 플로팅 게이트라는 도체에 전하를 가두어 정보를 저장했으나, 3D 낸드부터 부도체에 전하를 가두는 방식으로 개선됐다. CTN은 질화 규소(Silicon Nitride) 화합물로 만들어진 부도체 층을 뜻함

* 강유전체(Ferroelectric, Fe): 외부 전기장 없이도 자연 전기분극을 나타내는 물질로서 적절한 전기장이 가해지면 방향을 바꿀 수 있는 물질

* RTC(Revolutionary Technology Center): SK하이닉스 미래 기술 연구 조직으로 ‘ORP(Open Research Platform)’를 기반으로 활발한 연구 협력과 학술 활동을 통해 차세대 기술을 연구함 [관련기사]

* 산화하프늄(HfO2): 고유전율(High-k) 유전체로서 높은 유전상수, 열역학적 안정성과 증착의 단순성으로 인해 반도체 재료에 적용되는 물질

* 트리플 레벨 셀(Triple Level Cell, TLC): 낸드 플래시 메모리의 한 형태로서 메모리 셀당 최대 3비트의 데이터를 저장할 수 있음

* 테스트 구조(Test Vehicle): 장치 특성을 평가할 목적으로 제작한 구조

* 쿼드 레벨 셀(Quad Level Cell): 낸드 플래시 메모리의 한 형태로서 메모리 셀당 최대 4비트의 데이터를 저장할 수 있음

P/E 윈도우 확장을 위한 이상적인 셀 구조 찾기

3D Fe-낸드에서 TLC와 QLC 동작을 구현하려면 P/E 윈도우(Program/Erase Window)*를 추가적으로 확장해야 했다. 최근 RTC가 연구한 새로운 3D Fe-낸드 셀 구조의 셀 적층 최적화를 통해 P/E 윈도우를 최대 10.54V(볼트)까지 확대하여 QLC 동작 가능성을 확인했다.

* P/E 윈도우(Program/Erase Window): 셀의 삭제와 쓰기 처리를 위해 전자가 이동하면서 발생되는 문턱 전압(Vt)의 범위

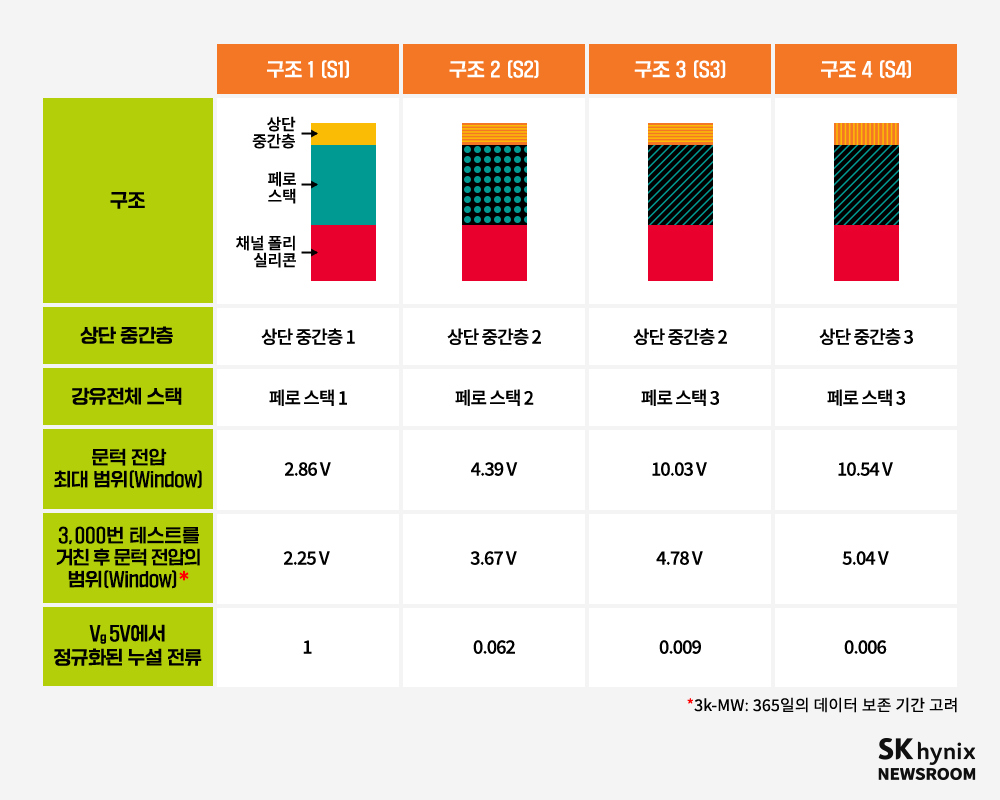

▲ 그림 1. Table showing key characteristics of four cell stack structures (S1–S4)

<그림 1>은 이번 연구에서 평가된 4가지 유형의 셀 구조(S1~S4)를 요약한 것으로 표준 P/E 윈도우, 삭제와 쓰기 동작을 3,000번 반복 테스트한 이후 P/E 윈도우와 채널-게이트 누설 전류 등을 포함한 전기적 특성을 비교한 것이다.

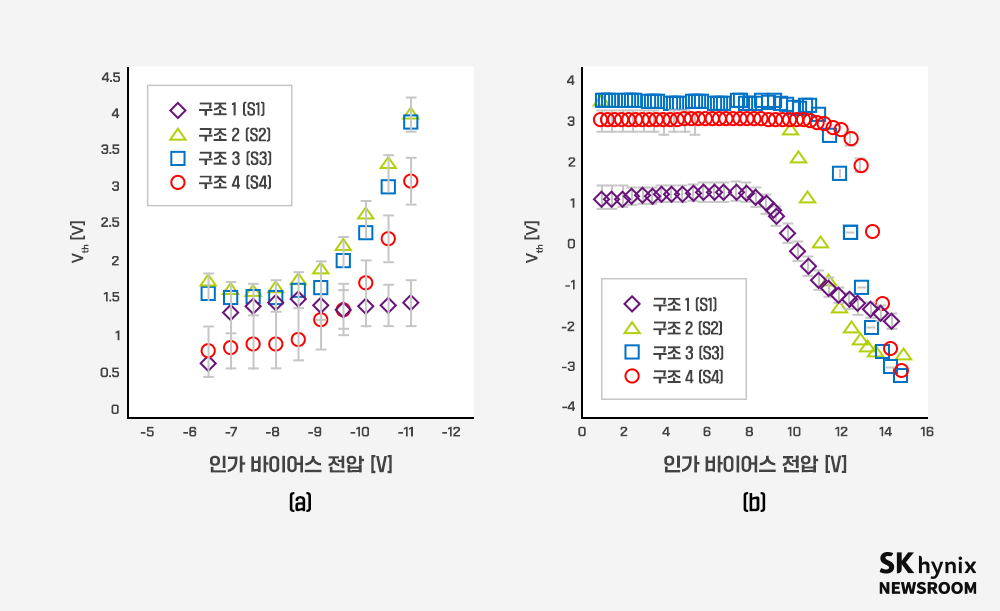

▲ 그림 2. Graphs comparing the (a) erase and (b) program performances of S1–S4

<그림 2> (a)와 (b)는 RTC가 기존 ISPE*와 ISPP*방법을 활용해 셀을 삭제하고 프로그래밍함에 따른 4가지 셀 구조의 전달 특성을 보여준다. 특히, S4는 누설 전류를 줄이고 강유전체 적층과 상부층간의 셀 구조를 최적화하여 10.54V로 P/E 마진 확보에 성공했다.

* ISPE(Incremental Step Pulse Erase): 전압 또는 펄스를 단계적으로 소량 늘려 메모리 요소를 특정 상태로 프로그래밍하거나 삭제 상태로 설정하는 메모리 프로그래밍 방법

* ISPP(Incremental Step Pulse Programming): 크기가 증가하는 일련의 프로그래밍 펄스를 메모리 셀 선택에 적용하여 임계 전압을 점차 높이는 메모리 프로그래밍 방법

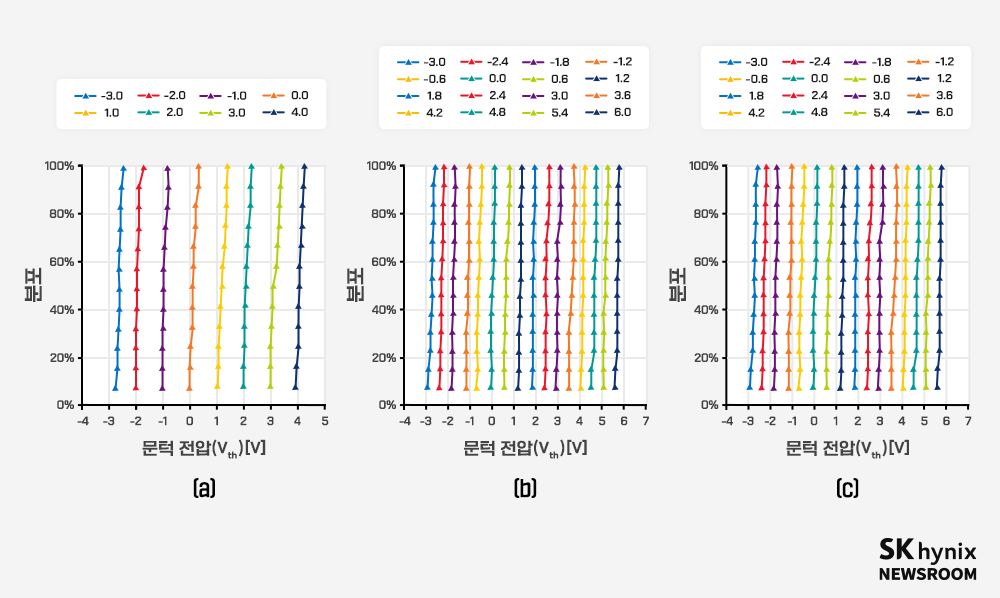

▲ 그림 3. Line graphs for S4 showing its (a) TLC Vth distribution (b) QLC Vth distribution and (c) post 3k cycle Vth distribution

S4에서는 TLC와 QLC 동작을 모두 수행했다. <그림 3> (a)는 S4의 TLC 검증 결과로 인접한 두 문턱 전압(Vth) 상태 간에 최소 갭 마진*이 0.45V임을 보여준다. 이는 RTC에서 과거 보유한 데이터인 최소 갭 마진 0.11V 대비 크게 개선된 것이다. 또한 <그림 3> (b)는 S4에서 P/E 윈도우가 확장되어 최소한 0.24V 이상의 갭 마진을 가져 QLC 동작 가능성이 있음을 보여준다. <그림 3> (c)에서는 삭제와 쓰기를 3,000번 반복하는 사이클링 스트레스 이후에도 최소한 0.14V 이상의 갭 마진을 가져 QLC 동작 가능성이 있음을 보여준다. 셀 적층 엔지니어링을 통해 P/E 윈도우 확장은 물론 삭제와 쓰기를 3,000번 반복하는 사이클링 스트레스 이후에도 QLC 동작이 가능한 수준으로 내구성 개선이 가능함도 보여줬다.

* 갭 마진(Margin): 결함, 오류 등이 발생된 지점을 제외한 안정된 영역을 말하는 것으로, 시스템이 동작하기 위한 여유 전압이나 전류를 뜻함

새로운 시대를 개척하는 3D Fe-낸드

SK하이닉스 RTC는 위와 같이 산화하프늄(HfO2) 기반 3D Fe-낸드 제작을 통해 현재의 3D CTN 낸드의 한계 극복 가능성을 살펴봤다. 이를 통해 셀 적층 구조를 최적화하여 확장된 P/E 윈도우를 제공함과 동시에 QLC 동작 시연을 통해 3D Fe-낸드가 차세대 낸드 소자로서 가능성이 있음을 확인할 수 있었다.