- 반도체 패키지를 칩 크기와 같게 초소형으로 구현한 제품

- 원가절감 및 전체 반도체 제작 공정기간 단축 효과 기대

- 시스템 작동시 발생 열의 원활한 배출로 제품 고성능화 추구

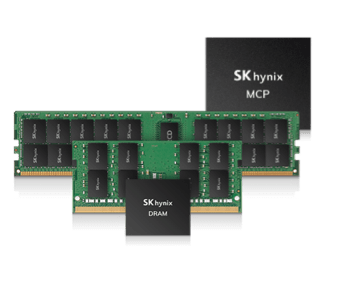

현대전자(대표 朴宗燮)가 노트북 및 이동통신기기에 쓰이는 초소형 256MB 반도체 모듈을 개발했다고 4일 발표했다. 현대전자가 이번에 개발한 모듈은 미국 FormFactor社와 기술협력한 WLCSP(Wafer Level Chip Scale Package) 기술을 이용해 만든 제품으로, 반도체 패키지(Package)를 칩(Chip) 크기와 같게 초소형으로 구현한 제품이다.

이 제품의 핵심인 WLCSP 기술은 반도체 부품의 탑재 면적을 가능한 한 칩 크기로 소형화하려는 CSP(Chip Scale Package) 기술을 웨이퍼 공정에서 일괄 처리할 수 있게 실현한 기술로, 웨이퍼 단위로 모든 패키지 공정이 이루어지며 최종 소자 분리(Die Sawing) 공정에 의해 개별 패키지로 분리되는 기술을 말한다.

기존의 TSOP(Thin Small Outline Package) 기술을 이용해서는 패키지의 크기가 커서 소자를 모듈에 8개(128MB)까지 밖에 탑재할 수 없지만, 이 기술을 이용하면 동일 소자를 양면으로 16개 탑재할 수 있어 256MB까지 지원할 수 있다. 이에 따라 현대전자는 기존 탑재면적 대비 29%의 매우 작은 면적에서도 탑재가 가능하여 원가절감을 꾀할 수 있으며, 웨이퍼 상에서 직접 패키징(Packaging)을 구현하기 때문에 전체 반도체 제작 공정기간을 단축시키는 효과가 있을 것으로 기대하고 있다.

또한 제품 특성 측면에서도 동작 주파수(Frequency) 및 신호 처리속도(Signal Setup Time)가 기존의 TSOP 패키지로 제작한 모듈에 비하여 우수한 성능을 보였으며, 시스템 작동시 발생하는 칩의 열을 더욱 원활하게 배출할 수 있어 제품의 고성능화를 꾀했다.

WLCSP기술은 D램, S램, 플래쉬 메모리(Flash Memory) 소자 등에 광범위하게 적용이 가능하며, 특히 메모리 소자와 기판 간의 전기적 연결을 가장 짧게 연결할 수 있고 패키지 크기가 칩 크기와 동일해 램버스 D램, DDR SD램 등 고속 메모리 소자와 노트북 및 이동통신기기용 제품에 적합한 차세대 패키지 방법으로 활발히 연구되고 있다.

현대전자는 내년 1월까지 이번 제품의 샘플(Engineering Sample)을 주요 고객들에게 배포해 적용 여부를 검토받을 예정이며, 후속 제품 개발을 위해 연구에 진력하고 있다.

최근 현대전자는 미국의 '씨티그룹'과 손을 잡고 재무구조 개선 및 기업지배구조 개선에 대한 공동 작업에 착수하였다. 현대전자의 재무 경영자문역(Financial Advisor) 으로 선임된 '씨티그룹'은 현재 씨티은행과 살로먼스미스社를 중심으로 국내외 금융시장에서 현대전자의 자금조달과 보유 유가증권 및 자산 매각의 창구역할을 수행하고 있다.

2000년 12월 4일(月)

-끝-

■ 용어 설명

- TSOP(Thin Small Outline Package) : 패키지의 양 측변으로부터 리드핀(lead pin)이 갈매기 날개모양인 L자상으로 나와 있는 패키지로, 패키지가 얇고 크기도 작아 소형 시스템에 사용되는 반도체 패키지 제품의 일종.