반도체 Fab 공정에서 트랜지스터(Transistor, TR)의 구조를 세우는 FEOL(Front End Of Line, Fab 전공정)이 완료되면 BEOL(Back End Of Line, Fab 후공정)을 진행합니다. BEOL 단계에서는 주로 배선과 절연막을 디자인에 따라 안배하고, 최종적으로 반도체 칩 표면에 보호막을 씌우는 패시베이션(Passivation)을 하면 Fab 공정이 모두 마무리되지요. FEOL에서 구성한 트랜지스터의 단자들과 BEOL에서 만든 배선 사이는 실리콘과 금속의 접합으로 연결되는데, 실리콘-금속의 단순한 화학적 접합으로는 트랜지스터가 본연의 기능을 수행하지 못합니다. 이때 실리사이드(Silicide)라는 새로운 중간 형태의 접합 층을 두어 실리콘과 금속 사이에서 정상적으로 전압에 비례하는 전류가 흐르도록 유도해야 합니다.

이번 장에서는 반도체 구조에서 나타나는 접합의 종류를 구분하고, 실리콘-금속 접합에서 필연적으로 나타나는 쇼트키 특성(Schottky Junction)에 대해 알아보겠습니다. 그리고 이를 해결하기 위해 실리사이드를 두어 쇼트키 특성이 저항 특성(Ohmic Contact)으로 변할 수 있도록 하는 과정과 두 개의 특성 차이를 함께 살펴보도록 하겠습니다.

1. 반도체 구조에서 나타나는 다양한 접합면

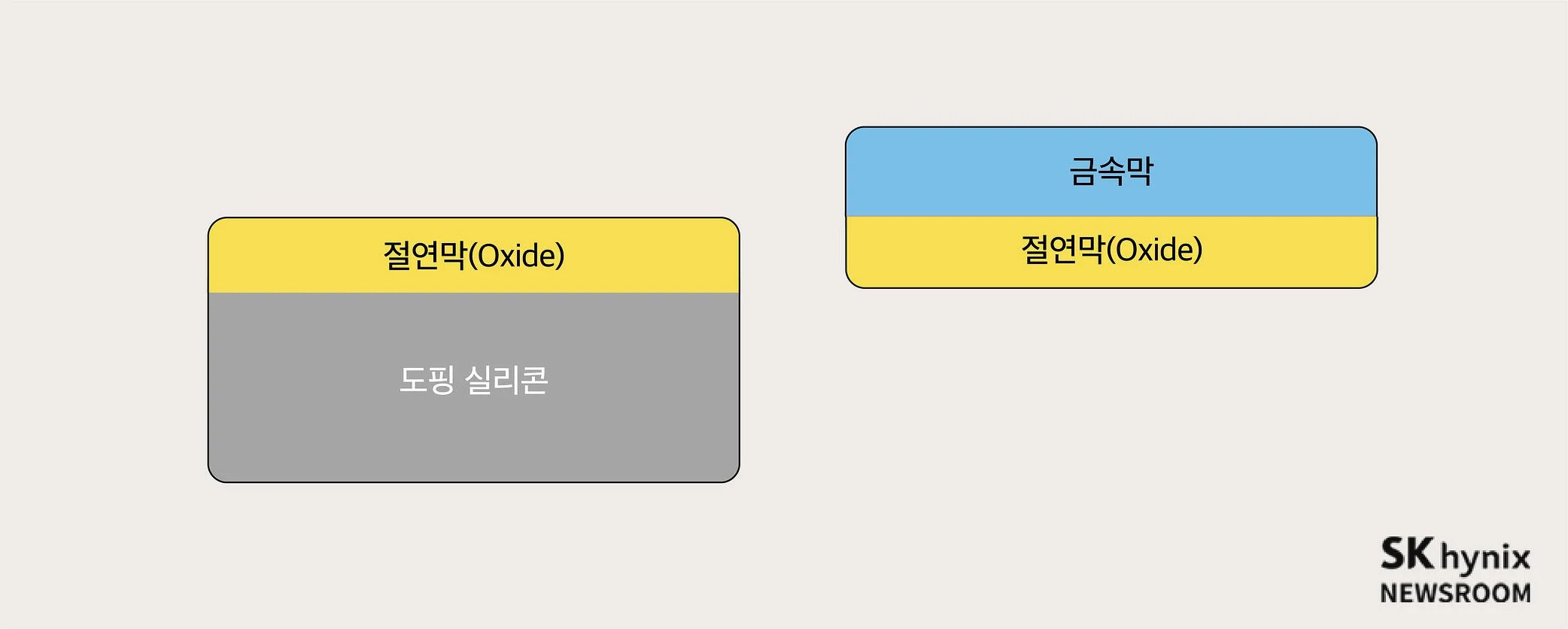

<그림1> 다양한 접합(Junction)면

1-1. 실리콘과 절연막

13족 혹은 15족으로 도핑(Doping)된 실리콘 표면에 산화공정(건식or습식) 혹은 증착(Deposition, CVD) 방식으로 옥사이드(Oxide) 막을 형성합니다. 실리콘과 절연막(이산화실리콘, 이산화하프늄, 이산화지르코늄 등)이 접합(Junction)돼 있으면, 실리콘 혹은 절연체 내부에서 어떤 반응이 일어날까요? 당연히 외부에서 어떠한 방향으로 전압(바이어스)을 가해도 혹은 인가하지 않고서도 아무런 반응도 발생하지 않습니다. 실리콘이 일정한 농도의 불순물 원소로 도핑되었다 해도 옥사이드 절연체의 절연성이 높아 활성화 에너지 또한 높아져 있으므로, 절연체 내부로 파고 들어갈 에너지가 상대적으로 너무 낮기 때문이지요. 또한 도핑된 실리콘이 많은 양의 캐리어(Carrier, 전자나 정공)를 보유했다고 해도, 절연체의 강력한 분자 결합을 뚫고 들어가 유효충돌을 발생시킬 수는 없습니다. 반대로 절연막에서도 실리콘(중성)으로 들어가 유효충돌을 발생시킬 입자가 발생하지 않지요.

1-2. 금속막과 절연막

절연막 위에 PVD(Physical Vapor Deposition, 물리기상증착) 방식으로 금속층을 증착시킨 경우에는 어떨까요? 금속이 절연체와 접합된 경우, 외부에서 어떠한 방향의 전압을 인가해도(혹은 인가하지 않아도) 역시 아무런 반응도 일어나지 않습니다. 도체에서는 상온에서 전자가 발생하지만, 바로 재결합(실리콘과 절연체 모두 동일)하여 금속 자체는 중성 상태를 유지합니다. 이러한 절연체와의 접합은 외부에서 매우 큰 에너지를 가해 파괴될지언정, 금속과 절연막이 상호 반응해 어떠한 특성을 발생시키지는 않습니다.

2. 금속막-절연막-실리콘의 3중 접합: MOS(Metal-Oxide-Semiconductor)

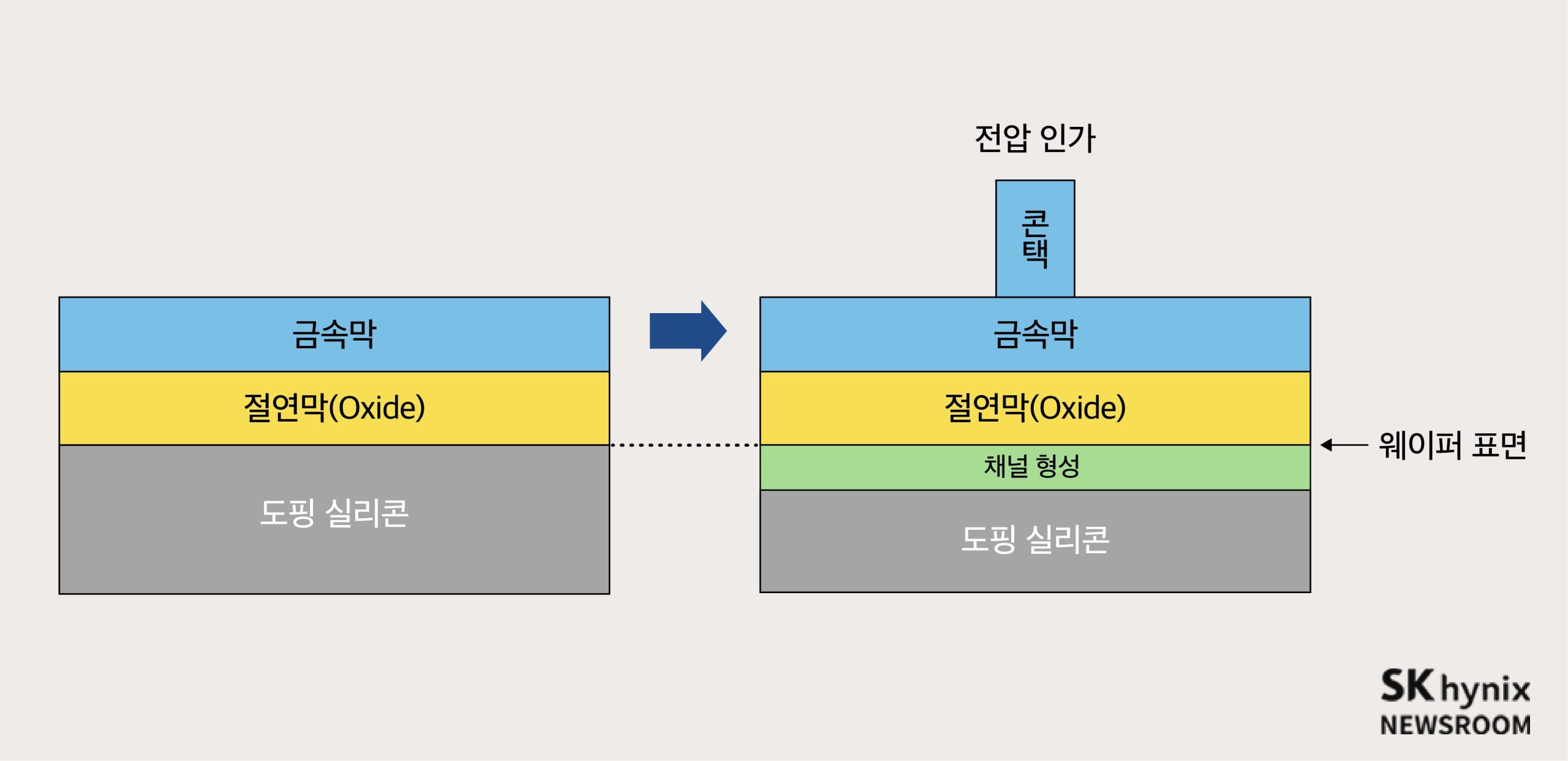

<그림2> 금속-절연체-실리콘 접합 (MOS)

이번에는 금속(Metal)막과 도핑된 실리콘(Silicon)이 절연막을 가운데 두고 구성된 MOS(Metal-Oxide-Silicon) 상태의 접합 구조를 살펴보겠습니다. MOS는 MOSFET를 수직축으로 본 구조이지만, 금속막에 전압이 가해지지 않는 한 모두 중성 상태를 유지합니다. 도핑된 실리콘 타입에 맞춰 금속막에 알맞은 전압이 가해질 경우, 이번에는 전압이 절연막을 넘어서서 실리콘에 영향을 끼치므로 절연막-실리콘 접합에서 접합면 방향으로 도핑된 실리콘의 소수 캐리어가 모여들어 캐리어 구름다리를 형성합니다. 기판이 P-Type 실리콘인 경우, 금속막에 플러스(+) 전압을 가해 소스 캐리어 전자가 모여들게 합니다. 그러나 이때 모여든 소수 캐리어들은 일반적으로 절연체와의 경계면에서 절연체 쪽으로 넘지 못하고 실리콘 경계면에 모여들 뿐이지요(이때 터널링 전자, 트랩 전자 등이 발생하지만 이러한 간헐적인 현상은 제외합니다). 이들은 드레인 전압 인가 조건에 한하여, 전자들이 소스 단자에서 드레인 단자로 통과하는 통로로 활용됩니다. 기판이 N-Type 실리콘인 경우에도 마이너스(-) 전압을 인가할 때 유사한 현상이 나타납니다. ▶ <[반도체 특강] 수직축으로 본 전자들의 여행:MOSFET> 편 참고

3. 금속과 실리콘(Metal-Semiconductor)의 접합

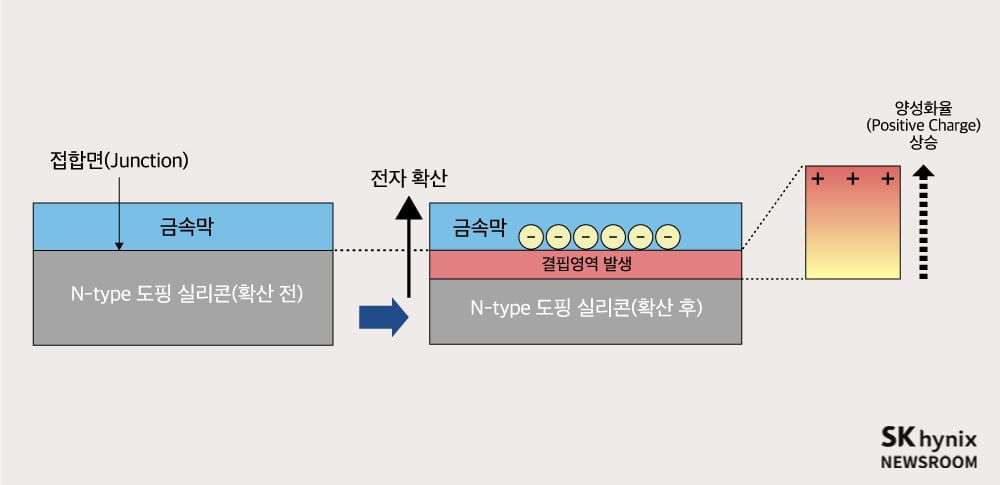

<그림3> 금속-실리콘 접합 (Metal-Semiconductor Junction)

다음으로 금속과 N-Type 실리콘이 접합된 경우를 살펴보도록 하겠습니다. 이는 MOS 구조에서 중간에 절연막이 없는 형태이지요. 금속-실리콘의 물리적 접합은 두 가지 경우 중 한 가지 특성을 나타냅니다. 실리콘에서 금속 쪽으로 전자들이 한 방향으로만 이동하거나(쇼트키 접합, Schottky Junction) 혹은 양방향으로 전자들이 자유롭게 이동(저항 접합, Ohmic Contact)하는 형태입니다. 쇼트키 접합은 PN 접합과 저항 접합의 중간 형태라 볼 수 있습니다. 조건에 따라 금속-실리콘 접합은 다이오드성(쇼트키) 기능을 하거나 혹은 저항성(일반 금속 연결) 기능을 하지요.

3-1. 쇼트키 접합(Schottky Junction)과 쇼트키 장벽(Schottky Barrier)

쇼트키 장벽(Schottky Barrier)은 금속-실리콘 접합에서 나타나는 현상으로, 전자들이 실리콘에서 금속으로는 흐르되 금속에서 실리콘 방향으로는 흐르지 못하게 막는 역할을 합니다. 이러한 장벽 특성을 나타내는 금속-실리콘 접합을 쇼트키 접합(Schottky Junction)이라고 합니다. 즉 쇼트키 접합은 실리콘에서 금속 방향으로는 저항 성분이 매우 낮고, 금속에서 실리콘 방향으로는 저항이 매우 높기 때문에 금속에서 실리콘 방향으로 캐리어(전자)가 이동하지 못하지요.

3-2. 결핍영역

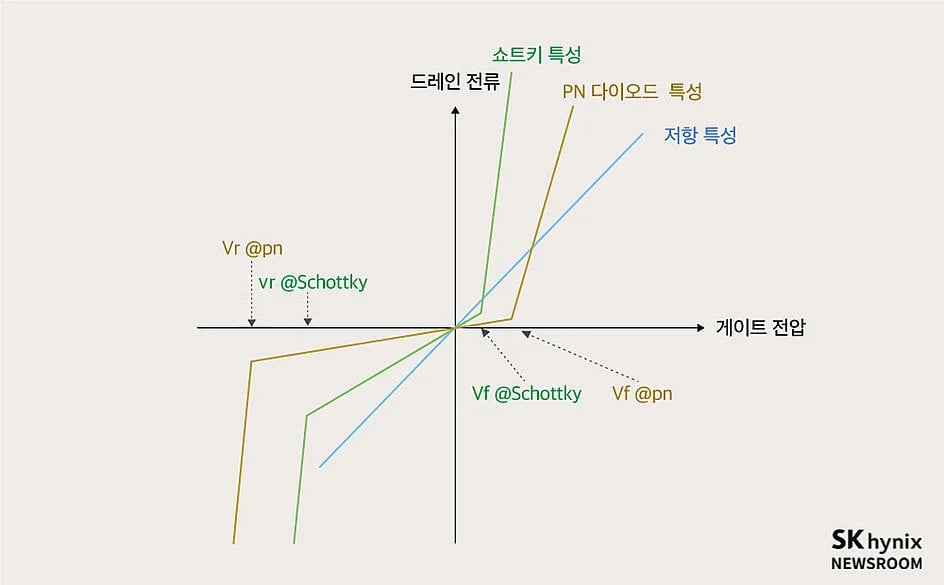

외부에서 인가전압이 없는 경우 실리콘은 도펀트(Dopant)에 의해 도핑되어 다수 캐리어가 확보된 상태이며, 금속에 접합(화학적)되면 다수 캐리어가 금속으로 확산 방식으로 들어갑니다. 이때 실리콘 영역에서는 캐리어들이 빠져나가므로 결핍영역이 발생하는데, 경계면에 가까울수록 잉여전자들이 많이 떨어져 나가므로 양성화율(Positive Charge)이 높습니다. 금속막으로 경계면을 넘어 온 전자들이 얇게 몰려 있는 전자층(금속막)과 결핍영역 사이에 전계가 형성되어 커패시터(Capacitor) 기능을 합니다. 이는 일정 시간이 지나면 전자가 양방향으로 이동하려는 것을 방해하지요. 그중 전자가 금속에서 실리콘 쪽으로 이동하는 것을 더욱 높은 저항으로 막아섭니다. 그러나 결핍영역이 한쪽만 형성되어 있으므로 PN 접합보다는 약하지요. 외부에서 전압 인가 시 결핍영역은 도핑된 실리콘에서만 형성되는 만큼, 쇼트키 접합이 PN 접합에 비해 순방향 전압강하(Vth)와 역방향 전압강하(Vr) 모두 낮습니다(도체에서는 없음).

4. 쇼트키 접합(Schottky Junction)의 다이오드(Diode) 기능

<그림4> 저항 vs 쇼트키 vs PN다이오드 @ 특성 차이

쇼트키 장벽이 발생하는 주원인은 실리콘에서 생긴 결핍영역과 금속 영역에서 매우 짧은 폭으로 형성되는 전자층(실리콘에서 금속으로 넘어간 전자들의 모임)의 영향입니다. 즉 금속의 전자들이 실리콘 쪽으로 흐르지 못하도록 전자층이 막아서고 있으며, 이를 뚫고 들어간다 해도 농도가 짙은 결핍영역에 전자들이 모두 소멸해 유효 전자들이 전류를 형성하지 못합니다. 또한 N-Type으로 도핑된 실리콘 내 전자들이 금속막 쪽에서 밀려오는 전자들을 밀어내기도 하지요. 외부에서 순방향 전압을 인가할 때에는 금속막에는 N-Type 실리콘의 다수 캐리어인 전자를 막는 결핍영역이 없으므로 PN 접합보다 매우 높은 전류가 흐르게 됩니다. 반면 역방향 전압을 인가할 시 금속 내 전자들이 PN 접합보다 쉽게 생성되므로 누설 전류가 급증하며 Breakdown 전압(Vr)이 낮아지는 효과가 있습니다. 쇼트키 접합의 역방향 전압-전류가 나타내는 성질을 보면, PN 접합의 다이오드와 저항 사이의 중간 특성을 보이면서 다이오드 특성 쪽으로 기울어진 형태를 보이지요.

5. 실리사이드(Silicide) 접합의 저항(Ohmic) 기능

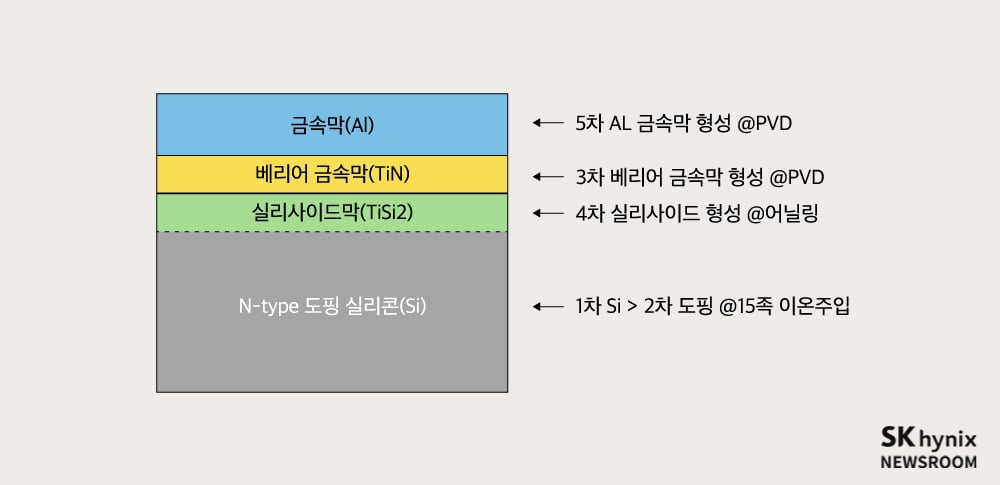

<그림5> 실리사이드(Silicide)층 형성

반면, 실리사이드를 형성해 쇼트키 장벽을 낮추어 낮은 비저항(면저항)을 가진 저항 접합 구조에서는 전자가 금속에서 실리콘 쪽으로 혹은 실리콘에서 금속 쪽으로 흐를 수 있습니다. 금속-실리콘 접합에서 쇼트키 장벽이 나타나지 않도록 해야 하는 이유는, TR의 각 단자(소스, 드레인)와 금속을 연결할 때 쇼트키 다이오드 효과가 나타나게 되면, TR의 드레인 정션/소스 정션의 다이오드 효과와 겹쳐져 TR이 정상적으로 동작할 수 없기 때문입니다.

쇼트키 접합을 피하기 위해서는, 금속-실리콘 접합을 낮은 저항성 동작으로 바꿔주도록 금속막의 접합면 부근의 금속 재질을 변경(비저항이 낮은 것으로)하는 일련의 실리사이드(TiSi2) 작업을 거쳐야 합니다. 실리사이드는 금속과 실리콘의 중간다리로써 능동 소자 역할을 하는 쇼트키 기능을 수동 소자 기능을 하는 면저항 성분으로 변경하고, 면저항값 자체를 의도하는 레벨까지 낮춰주지요. PVD공정으로 금속막을 형성하기 전에, 실리콘 사이에 두께가 매우 얇은 베리어 금속막(TiN)을 형성시킨 뒤 어닐링(Annealing)을 진행하면, 금속 성분이 실리콘으로 파고들어 가 실리사이드가 형성됩니다. 그러면 실리사이드-금속 접합면이 형성될 때 나타내는 쇼트키 특성이 저항 특성으로 변하게 되지요. 마지막으로 베리어 금속막 위에 필요한 금속막(알루미늄, 구리 등)을 PVD, 전해도금 등으로 여러 개 층(M1, M2, M3 등)을 구분해 증착합니다.

반도체 내 대부분의 접합은 금속-절연체 혹은 실리콘-절연체의 접합으로 이뤄져 있으며, 금속-실리콘 접합은 일부분입니다. 하지만 여기서 다룬 금속-실리콘 접합은 시그널(Data)과 전원 전압이 반도체 칩 내부 회로로 진입(Access)할 수 있는지를 결정하는 매우 중요한 기능을 하지요. 금속-실리콘의 화학적 접합(Junction) 자체만으로는 능동소자인 쇼트키 다이오드(Schottky Diode) 특성을 나타내어 트랜지스터의 기능을 마비시키지만, 실리사이드라는 층을 새롭게 만들어 TR이 고유의 기능을 할 수 있도록 합니다. 실리사이드는 음식에 뿌리는 후추 같은 역할을 한다고 볼 수 있지요.

※ 본 칼럼은 반도체/ICT에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.