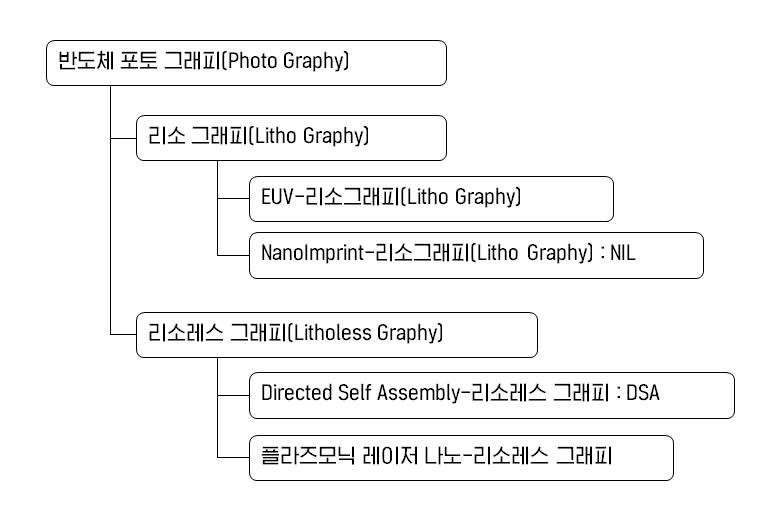

반도체의 용량 증가와 성능 개선은 서로 트레이드오프(Trade Off) 관계라고 할 수 있습니다. 일반적으로 용량을 늘리면 성능이 떨어지고, 성능을 향상시키면 용량이 줄어드는 쪽으로 작용하기 때문입니다. 반도체 공정에서 이렇게 상반되는 두 가지 요소를 한꺼번에 개선하기는 어렵습니다. 하지만 시장은 언제나 두 가지 모두 크게 진전되기를 요구하죠. 포토공정에서 Mega bit 단위의 저용량시의 리소그래피 방식은 어느 정도 이 두 가지를 한꺼번에 만족시키는 데 일조했다고 볼 수 있는데요. 이제는 Giga bit, Tera bit 단위의 반도체 회로를 그릴 때, 마스크(Mask)를 사용하는 리소그래피 방식인 NIL뿐 아니라 마스크를 사용하지 않는 리소레스 그래피 방식인 DSA, 혹은 플라즈모닉 레이저 방식 등이 검토 및 응용되고 있습니다. 그리고 향후에는 더욱 개선된 방안들이 나타날 것으로 보입니다.

포토공정과 리소그래피

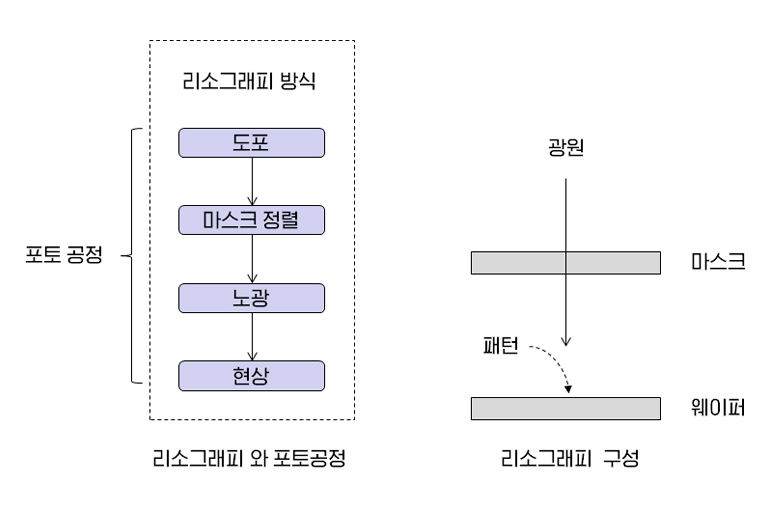

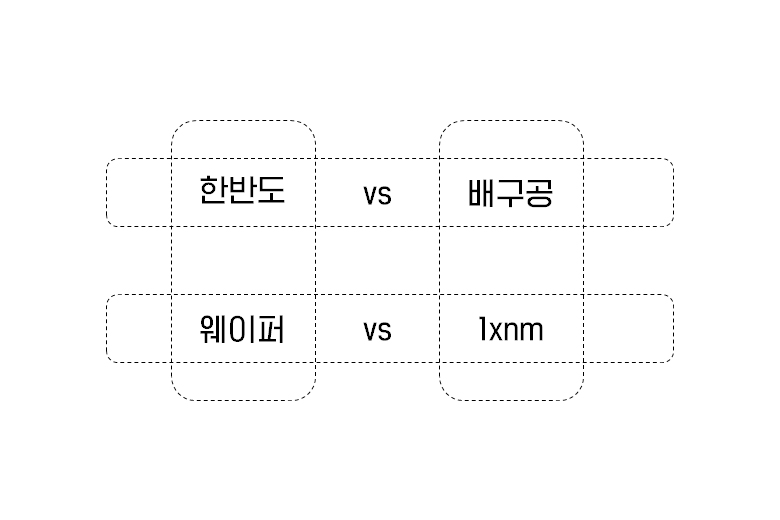

▲ 포토 공정과 포토-리소그래피 방식

반도체 팹의 포토공정은 웨이퍼 상의 회로 패턴을 구현하기 위한 공정입니다. 팹공정에서는 먼저 방식이 정해지면, 방식을 전개하기 위한 공정들이 설정됩니다. 리소그래피는 ‘공정’이 아닌 ‘방식’이라고 볼 수 있으며, 마스크를 이용하는 방식을 포토-리소그래피(Lithography)라고 합니다. 반면 Mask를 사용하지 않는 포토 공정은 포토-마스크리스 그래피(Maskless graphy) 방식이라 하는데요. 이는 포토-리소레스그래피(Litholess graphy)라고 할 수 있습니다. 포토공정은 회로 패턴을 만들기 위한 리소그래피 방식을 전개하기 위해 도포(coating), 마스크 정렬(mask alignment), 노광(exposure), 현상(development) 등의 세부공정으로 진행됩니다. 포토공정에 이어서 식각(etching)과 세정(cleaning)공정을 실시하면 반도체의 회로 패턴이 완성됩니다. 리소레스 그래피 방식의 포토 공정들은 마스크 정렬 공정 등이 없어지고 다른 공정들이 추가될 것입니다(엄밀히 말하면 NIL의 스탬프는 Litho와 Litholess의 중간 형태라고 볼 수 있습니다).

포토-리소그래피(Photo-Lithography)의 의미

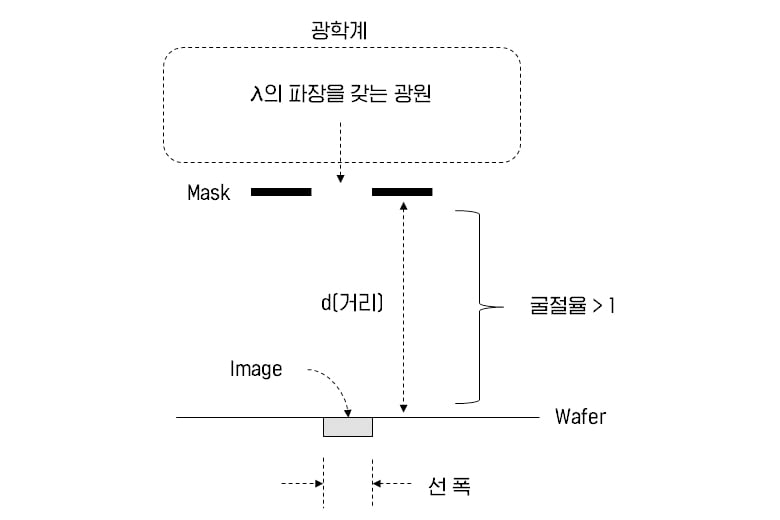

▲ 포토-리소그래피 방식의 세부

웨이퍼 위에 MOSFET를 구성하려면 기본적인 트랜지스터(Transistor, Tr) 형태가 구조적으로 형성되어야 합니다. 웨이퍼 상에 몇 천억 개의 Tr을 한꺼번에 구성하기 위해 빛과 마스크(레티클)를 사용하여 일괄적으로 회로를 형성하는 방식을 포토-리소그래피라고 합니다. 여기서 Litho는 석판(Mask)을 의미하고, Photo graphy는 빛을 이용하는 그래프를 뜻하지요. 따라서 빛을 사용한 석판인쇄술을 Photo-Lithography라 합니다. 이때 빛은 석판의 모양을 축소하여 웨이퍼 상에 정확하게 옮겨 놓는 노광 역할을 합니다. 또, 리소그래피는 사진식각 기술이라 불리기도 하는데요. 이는 웨이퍼 상에 패턴을 형성하기 위한 사진기술과, 패턴을 최종적으로 형성하기 위해 식각하는 기술을 합한 것입니다.

회로 패턴(Pattern)과 파장

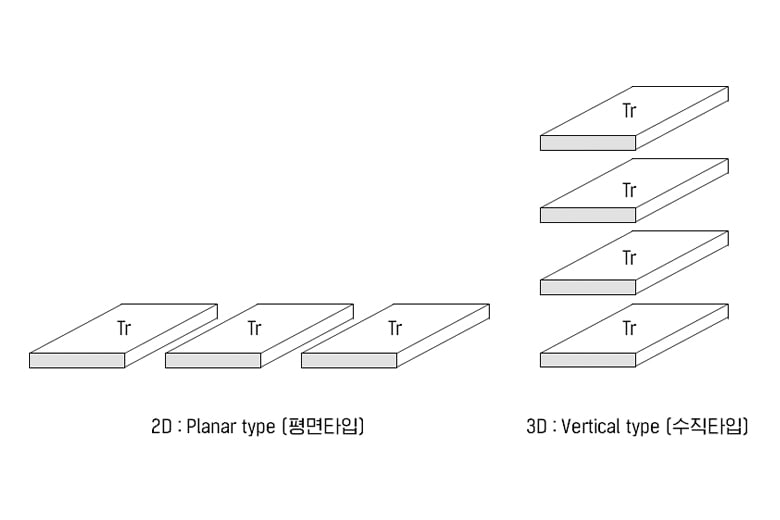

▲ 웨이퍼와 도선 폭인 1xnm의 크기 비교

직경이 12인치(300mm)인 웨이퍼가 한반도 전체 면적이라면, 최근 웨이퍼 상의 회로 패턴 폭인 1xnm급은 배구공 직경 정도의 비율이라고 볼 수 있습니다. 테크놀로지가 축약(Shrinkage)될수록 회로의 패턴 폭이 작아지고, 회로 선 폭이 줄어들면 포토 공정 시에 사용하는 포토 마스크의 개구(Mask aperture)도 줄어듭니다. 그에 따라 빛(노광)의 파장도 줄어들어야 하죠. 혹은 사용하는 광원의 파장이 짧아지기 때문에 제반 장치 여건이 그에 따라 변경되기도 하는 구조입니다. 현재까지 파장을 줄이고 줄여 극초단파장EUV를 성공적으로 접목시키고, DPT(Dual patterning technology) 등 일부 팹공정상의 기법들을 발전시킴으로써 drop될 수도 있었던 리소그래피 방식이 어느 정도 롱런할 수 있었습니다. 리소그래피의 정밀도는 광소스에서 발생하는 파의 길이(파장)이 얼마나 짧느냐가 핵심이지요.

구조의 변화 방향

▲ 구조적 발전(2D에서 3D로)

반도체 테크놀로지가 발전한다는 것은 용량이 증가한다는 측면에서는 긍정적입니다. 하지만 크기(Scale)가 줄어들수록 구조(Structure) 상 스트레스가 많아지므로 성능에는 부정적인 영향을 끼칩니다. 지금까지 성능 향상을 위한 노력은 꾸준히 이루어졌지만, 구조의 스케일다운(Scale-down) 효과에 의해 그 의미가 감쇠되어 왔습니다. 이에 따라 성능 향상과 스케일다운, 두 가지 모두를 충족시키기 위해 메모리에서는 2D 구조에서 3D 구조로 방향이 선회되었죠. 기존의 2D에서는 셀을 수평적 방향으로 늘어놓았다면, 3D는 수직축 방향으로 셀을 쌓는 것(Cell Stacking)을 의미합니다. 스케일 다운은 2D방향이므로, 3D를 적용하여 테크놀로지 측면으로 여유가 발생되어서 리소그래피 타입을 일정기간 계속 사용할 수 있도록 3D가 디딤돌 역할을 하고 있는 셈입니다.

차세대 포토그래피 기술, 포토-리소레스 그래피(Photo-Litholess graphy)

마스크를 사용하는 포토-리소그래피 공정은 EUVL(EUV Lithography)와 NIL(Nano Imprint Lithography) 로 나눌 수 있습니다. 포토 공정 시 마스크를 사용하지 않는 포토-마스크리스그래피 혹은 포토-리소레스그래피 방식에는 DSA(Directed Self-Assembly)와 플라즈모닉 레이저 응용 방식 등이 해당되는데요. NIL은 웨이퍼 상에 코팅한 PR(Photo Resist) 위에 나노패턴을 도장(스템프)형식으로 찍어내는 방식을 말합니다(스템프가 마스크 역할). 이는 EUV 장비보다 경제적이지만 패턴을 여러 가지 유형으로 변형하는 능력이 EUV리소그래피 방식에 비해 떨어지고, PR과의 접촉 방식으로 오염 등의 문제점이 발생할 수 있습니다. DSA는 패턴을 화학적으로 형성하여 활용하는데, 공정수를 다수 줄여 원가 절감에 유리하지만 활용기술적으로는 NIL보다는 뒤처집니다(DSA의 핵심적인 프로세스에서는 마스크를 사용하지 않음). 레이저를 이용한 방식은 마스크 위에서 레이저를 투과시키는 레이저-마스크-리소그래피 방식에서 발전한 것으로, 마스크가 없는 플라즈모닉 레이저로 패턴을 만드는 방식(플라즈모닉-레이저-나노그래피)입니다. 이는 회로 패턴을 자유자재로 변경할 수는 있지만, 아직 분해능이 EUV리소그래피에 미치지 못하는 단점이 있습니다.

포토 공정의 핵심은 정확한 회로 패턴을 형성하는 것입니다. 하지만 파(波)의 회절현상으로 인하여 30nm 이하의 회로선폭을 구현하는 데 한계를 겪었죠. 이를 극복하기 위해 여러 가지 방안이 도출되었고, 성공 여부에 따라서 반도체 장비를 만드는 기업들의 생사가 갈리기도 했습니다. 아직까지는 마스크를 사용하는 리소그래피 방식이 마스크를 사용하지 않는 리소레스그래피 방식에 비해 광 분해능이 월등히 높기 때문에 더 많이 쓰이고 있습니다. 리소그래피 방식은 EUV 방식이 접목되면서 파의 분해능의 한계인 30nm을 뛰어넘어 13.5nm의 파장을 구현하였고, 패턴 구현의 공정 방식인 DPT와 QPT 기술과 접목되면서 10nm 미만의 회로선폭이 가능하게 되었습니다. 앞으로 차세대 기술들과 리소그래피 방식이 결합되고 병행 사용되면서 xnm인 꿈의 선폭이 웨이퍼 위에 화려하게 회로를 그려나갈 것입니다.

※ 본 칼럼은 반도체/ICT에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.