1965년 4월, 인텔의 공동 창립자인 고든 무어는 ‘일렉트로닉스’ 잡지에 이와 같은 말을 했습니다. “반도체 칩에 들어갈 수 있는 트랜지스터 수는 2년마다 2배씩 늘어날 것이다!” 이후 이 말은 ‘무어의 법칙’이라 불리게 되었고 인텔뿐만 아니라 전 세계 반도체 업체들은 이 법칙에 따라 반도체를 개발해 왔습니다. 그런데 51년이 지난 지금, 향후 반도체 기술 동향을 예측하고 반도체 및 관련 산업이 발전해나가는 방향을 제시하는 비상업적인 순수 로드맵, ITRS에서는 무어의 법칙이 더는 유효하지 않을 것이라 예상하는데요. 그 이유가 과연 무엇인지 알아볼까요?

반도체 개발의 정석, 무어의 법칙이란?

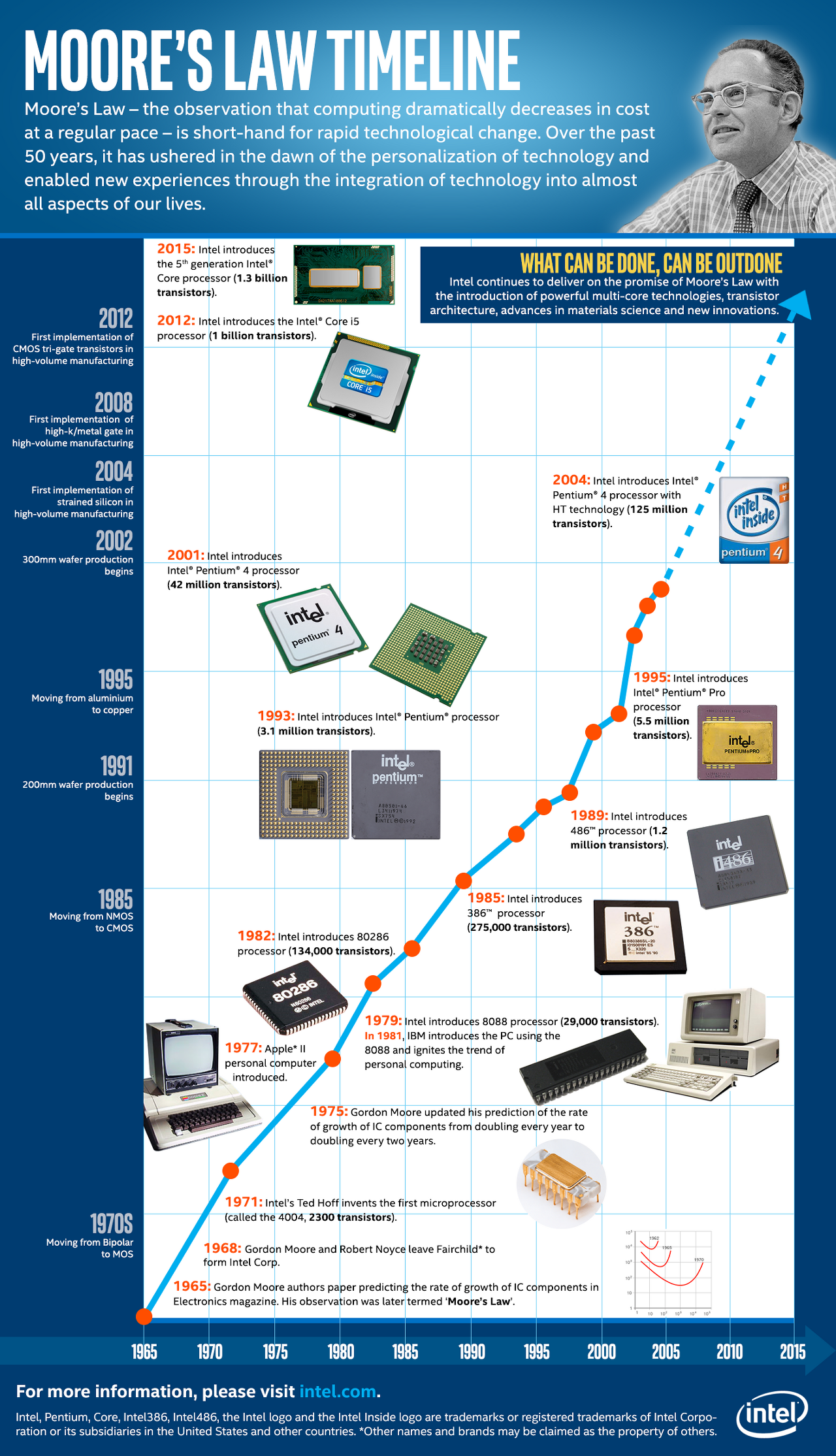

무어의 법칙이란, 반도체 칩의 성능이 2년마다 두 배씩 좋아지는 것을 말하는데요. 1965년부터 지금까지 반도체 칩에 들어가는 트랜지스터의 숫자는 2년마다 두 배 혹은 그 이상씩 증가했습니다. 1989년, 120만 개에 불과했던 트랜지스터 숫자는 현재 19억 개에 이르는데요. 트랜지스터의 크기를 줄이고 촘촘하게 붙여 넣은 모습이 마치 공동 주택가 혹은 밀집한 아파트 단지의 모습과 비슷하지 않나요?

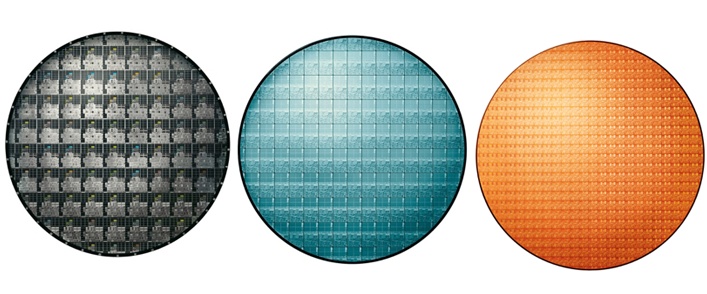

▲ 세대를 거듭할수록 작아지는 트랜지스터의 모습 (출처: Intel 홈페이지)

무어의 법칙, 한계에 다다른 이유

이러한 무어의 법칙이 1965년부터 지금까지 약 50년간 지켜질 수 있었던 이유는 무엇이었을까요? 바로 전 세계의 반도체 업계가 법칙을 지키기 위해 부단히 노력했기 때문입니다. 하지만 이러한 노력에도 불구하고 2000년대 초반부터는 개발 시기가 점점 늦어지고 있으며 실제로 한계에 다다랐다고 하는데요. 그 이유를 살펴보도록 하겠습니다.

▲ 약 50년간 지켜져 왔던 ‘무어의 법칙’ (출처: Intel 홈페이지)

하나. 양자 터널 효과에 따른 누설 전류 현상

앞서 말씀 드렸듯이 ‘트랜지스터의 수가 2년마다 두 배씩 증가한다’는 무어의 법칙 대로라면 현재 14nm반도체 미세 공정을 내년에는 10nm 공정으로 줄여야 하는데요. 더 이상 그 주기를 지키기 어려운 가장 큰 이유는 바로 미세화의 한계 때문입니다.

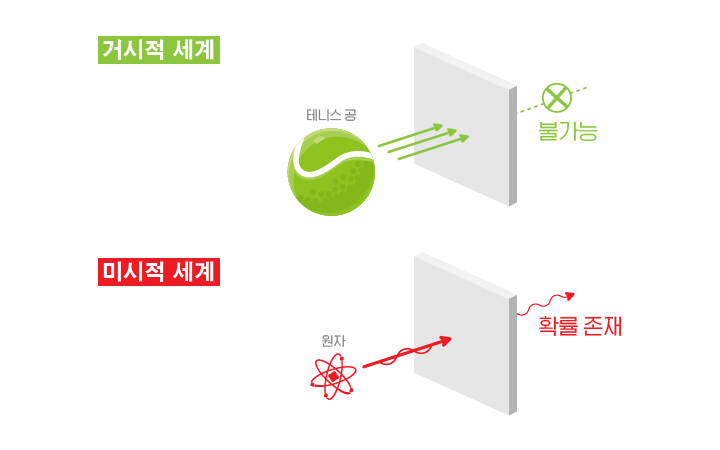

먼저 기본적인 양자역학적 원리를 한가지 소개하겠습니다. 우리가 알고 있는 거시적 세계에서는 테니스 공이 단단한 벽을 뚫고 다른 방으로 넘어가지 못합니다. 하지만 나노미터 단위로 깊이 들어가 원자들의 세계를 들여다보면, 상황은 조금 달라집니다. 이런 미시적 세계에서는 벽이 아주 얇다고 가정해보면 전자들이 다른 방으로 뚫고 갈 확률이 존재합니다. 이와 같은 경우를 바로 ‘양자 터널 효과’라고 하죠.

▲ 미시적 세계에서 원자는 벽을 뚫고 지나갈 수 있는 확률이 존재한다.

전류의 통로가 10nm 정도로 미세한 공간에서는 전자가 양자 터널 효과를 보이기 때문에 전류가 새는 ‘누설전류’가 생기게 됩니다. 한 개도 아닌 수십억 개의 트랜지스터에서 누설전류가 생긴다면, 당연히 반도체가 제 기능을 못하게 되겠죠? 이를 보완할 만한 대책이 있긴 하지만, 실리콘 기반의 트랜지스터는 가장 근본적인 물리학적 문제 때문에 무한정 작아질 수 없다는 점! 기억해주세요.

둘. 미세한 회로 폭, 더 높아지는 열

반도체 데이터 용량이나 처리 속도 등 성능이 중요해짐에 따라 작은 칩 공간 안에 고성능 구현을 위해 반도체 회로 선폭을 줄여 더 많은 회로를 담았는데요. 이로 인해 누설 전류가 늘어나 발열이 심해지는 문제도 발생하고 있다고 합니다. 이를 해결하기 위해 소재와 설계 등을 바꾸는 노력들을 지속적으로 해왔는데요. 공정이 점점 더 미세화 됨에 따라 해결하기 어려운 문제로 다가오고 있습니다.

셋. 기존보다 늘어나는 제조 비용

만일 미세 공정의 기술적인 문제가 해결되어 웨이퍼 당 더 많은 반도체를 만들 수 있다고 하더라도 또 다른 문제가 발생 되는데요. 그것은 바로 제조 비용의 문제입니다.

매우 미세한 공정을 진행하기 위해서는 추가적으로 장비도 더 필요하게 되며, 공정 과정도 더욱 복잡해집니다. 그로 인해 반도체 제조비용은 급격하게 상승합니다. 즉 성능은 좋아지면서 가격은 저렴해진다는 무어의 법칙의 근본 원리가 무너지게 되는 것이죠. 다시 말해 반도체를 작게 만들어서 얻게 되는 원가 절감 효과가 줄어들게 됩니다. 그리고 이 문제는 미세화 되면 될 수록 더욱 커지게 됩니다.

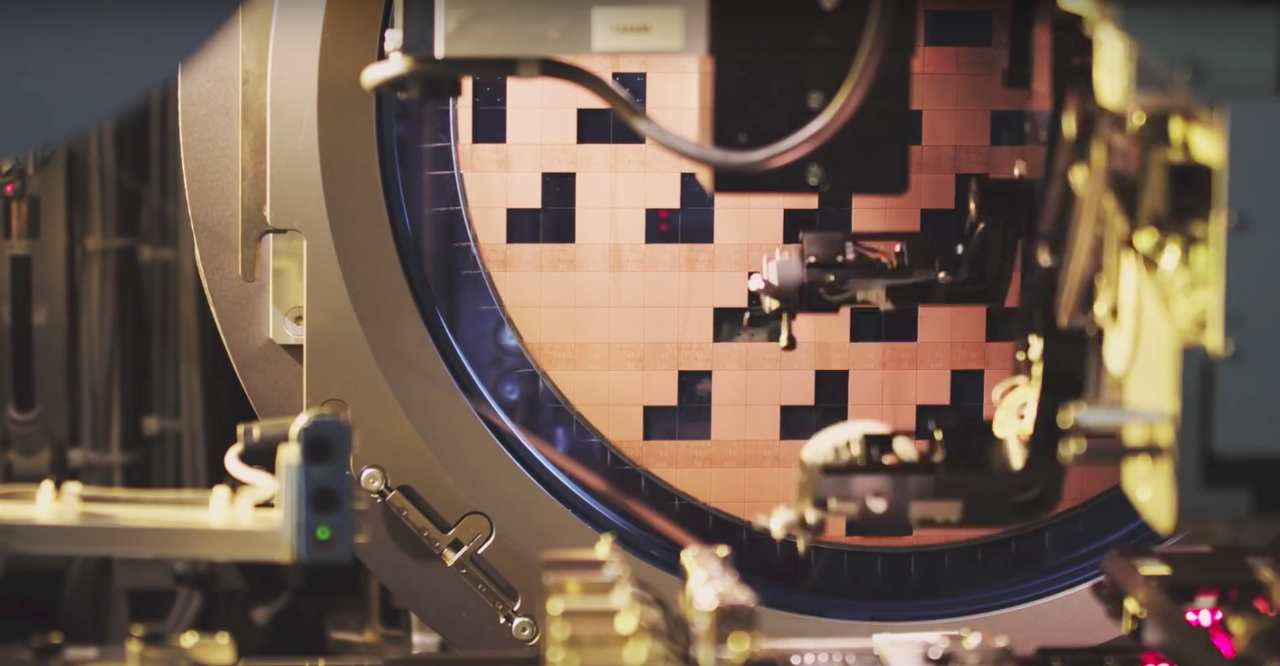

▲반도체 공정 과정 (출처: Youtube ‘intel’ 채널)

반도체 개발 기술, 현재는 어떤 방향으로?

지금까지는 무어의 법칙을 기반으로 반도체 칩 크기는 더 작게, 성능은 더 좋게 개발해왔습니다. 하지만 크기를 더 작게 만드는 것만이 능사는 아닌데요. 경제적 측면이나 물리학적 한계를 통해 살펴봤을 때, 반도체를 더 작게 만드는 개발의 경쟁시대는 더 이상 어려울 것으로 보입니다. 물론 앞으로도 반도체의 성능 향상은 계속 될 테지만, 그건 다른 방식으로 일어날 수도 있습니다. 지금 반도체 업계는 기존의 주 재료인 실리콘이 아닌 새로운 물질, ‘그래핀’과 ‘탄소나노튜브(CNT)’를 이용한 반도체를 개발 중입니다. 또 저장 능력과 계산 능력이 뛰어난 양자를 반도체 소자의 재료로 사용하기 위해 끊임없이 개발하고 있습니다.

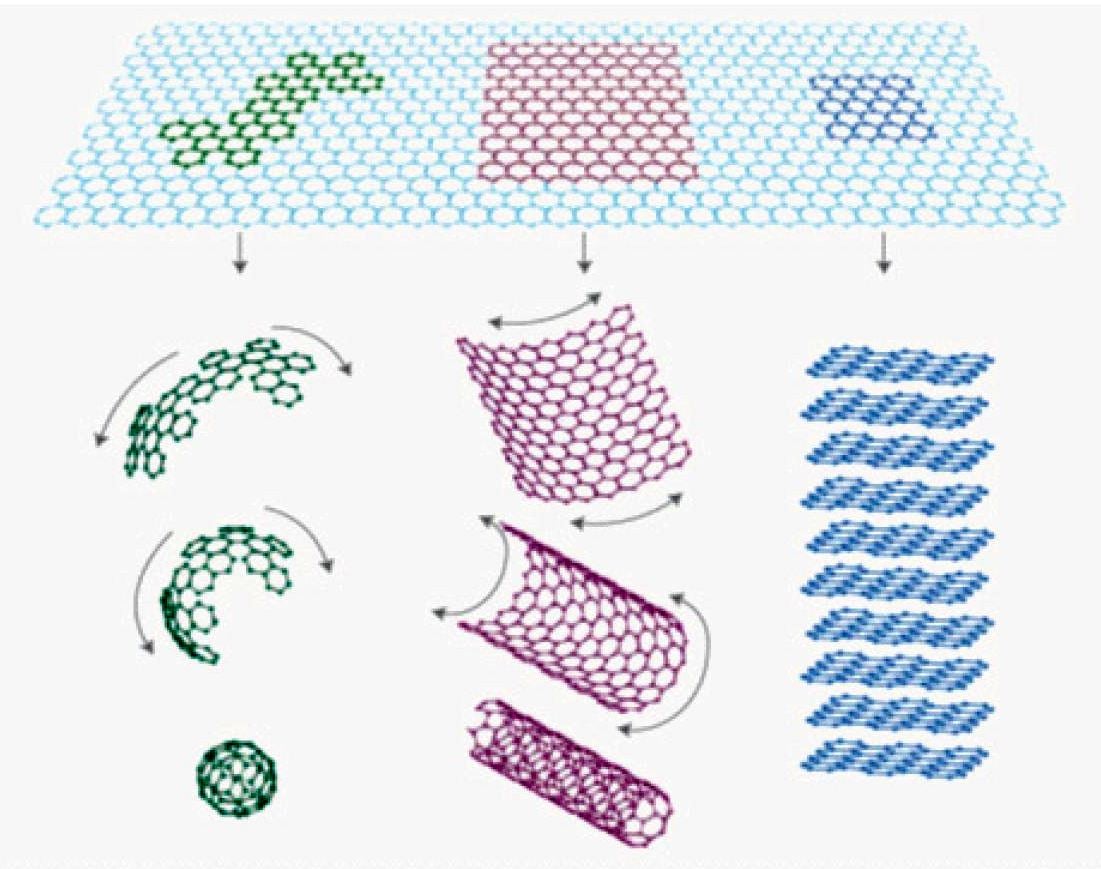

▲그래핀과 탄소나노튜브 (출처: 위키피디아)

하나. 새로운 물질, 그래핀과 양자

흑연은 탄소가 벌집처럼 육각형 모양으로 배열된 평면이 여러 층으로 쌓여 있는 구조인데요. 이 흑연의 한 층을 ‘그래핀’이라고 말합니다. 이런 이유로 그래핀을 세상에서 가장 얇은 물질이라고 말하기도 합니다. 그래핀은 굉장히 얇기 때문에 유리보다 투명하며, 구조 특성상 신축성이 좋고 강철보다 10배 이상 강도가 좋아 10nm이하의 미세 공정 도입도 가능합니다. 또 탄소의 결합 특성상 전기 전도성도 실리콘보다 훨씬 좋은데요. 그렇기 때문에 실리콘 반도체보다 처리속도를 100배 이상 높일 수 있는 장점이 있습니다.

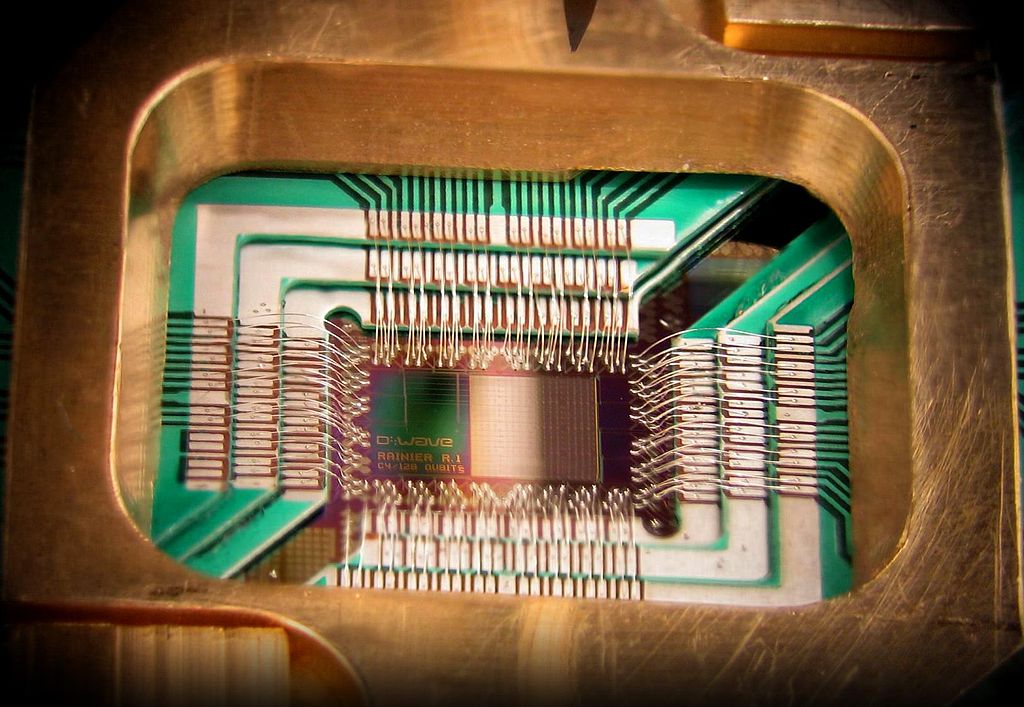

더는 나눌 수 없는 최소량의 단위, 양자를 이용해 만든 반도체는 아직 연구개발이 많이 필요한 미래 기술입니다. 하지만 연구개발이 완료되고 상용화가 된다면 기존의 슈퍼컴퓨터보다 훨씬 빠른 계산을 할 수 있는 양자컴퓨터를 만나게 될 것입니다.

▲양자 컴퓨터 (출처: 위키피디아)

둘. 차세대 메모리 개발

그래핀과 양자 등 새로운 재료로 만든 반도체 이외에도 차세대 메모리 개발을 통해 공정 미세화 한계를 극복하고자 노력하고 있는데요. SK하이닉스도 미래 기술 경쟁력 강화를 위해 차세대 메모리를 개발을 진행하고 있으며, 향후 개발 성숙도와 시장 상황 등을 고려해서 양산 시기를 결정할 계획이라고 합니다. 그럼 차세대 메모리에 대해 간단하게 한 번 알아볼까요?

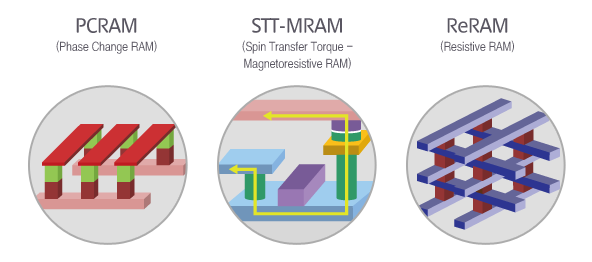

▲ SK하이닉스에서 개발 중인 차세대 메모리 3종 (출처: SK하이닉스 블로그)

1. PC RAM (Phase-Change RAM)

GST라는 상변화 물질에 온도를 가하면 물질의 일부분이 결정질 상태에서 비정질 상태로 변하는데요. 이에 따른 저항의 차이를 이용해 데이터를 기록할 수 있습니다.

2. STT MRAM (Spin Transfer Torque Magnetic RAM)

자성의 변화에 따른 특성을 이용해 데이터를 저장합니다. 자화의 뱡향과 Spin 방향이 같은 전자는 저항이 낮은 상태가 되어 전류량이 증가하고, 자화의 방향과 Spin 방향이 다른 전자는 저항이 증가하여 전류량이 감소하는 원리로 데이터를 저장합니다.

3. ReRAM

Resistive RAM의 약자로 전기적 신호에 따라 저항이 큰 부도체 상태에서 저항이 작은 도체 상태로 바뀌는 메모리 특성을 이용하여 정보를 저장합니다. ReRAM은 두 개의 금속전극 사이에 절연막을 삽입한 매우 간단한 구조의 메모리 소자로 전기적인 신호에 따라 저항이 크게 변하는 원리를 이용한 차세대 메모리인데요. 추후 NAND Flash의 역할을 대체할 것으로 여겨집니다

무어의 법칙과 더불어 반도체의 미래에 대한 부분까지 알아봤는데요. 무어의 법칙은 깨졌지만, 반도체는 지금도, 앞으로도 계속 발전할 것입니다. 이제는 단순히 2년마다 두 배씩 트랜지스터의 집적도만 높이는 데 열중할 것이 아니라 더 근본적으로 반도체의 한계를 뛰어넘는 혁신이 필요한데요. 무어의 법칙을 넘어 제품의 요구에 맞는, 새로운 패러다임으로 생산된 반도체의 만남, 앞으로가 더 기대되지 않으신가요?