메모리 반도체의 신뢰성(Reliability) 문제는 대부분 일정 시간이 흐른 뒤 발생하는 불량 유형입니다. 낸드 소자를 구성하는 일정 부분이 열화를 받아 제 기능을 못하는 상태를 말하지요. 반도체의 회로 선폭이 좁아지고 용량이 커질수록, 신뢰성 중 교란성(Disturbance) 및 간섭성(Interference) 불량이 많이 발생하게 됩니다. 특히 높은 전압을 사용해 프로그램을 동작(데이터를 저장)시킬 때 문제가 더욱 자주 나타나지요. 지난 시간에는 비휘발성 메모리 2D 낸드를 중심으로 반도체의 네 가지 신뢰성 중 보존성(Retention)과 내구성(Endurance)에 대해 살펴봤는데요. 오늘은 지난 편에 이어 교란성(Disturbance)과 간섭성(Interference)까지 함께 알아보도록 하겠습니다.

1. 교란성 불량이란?

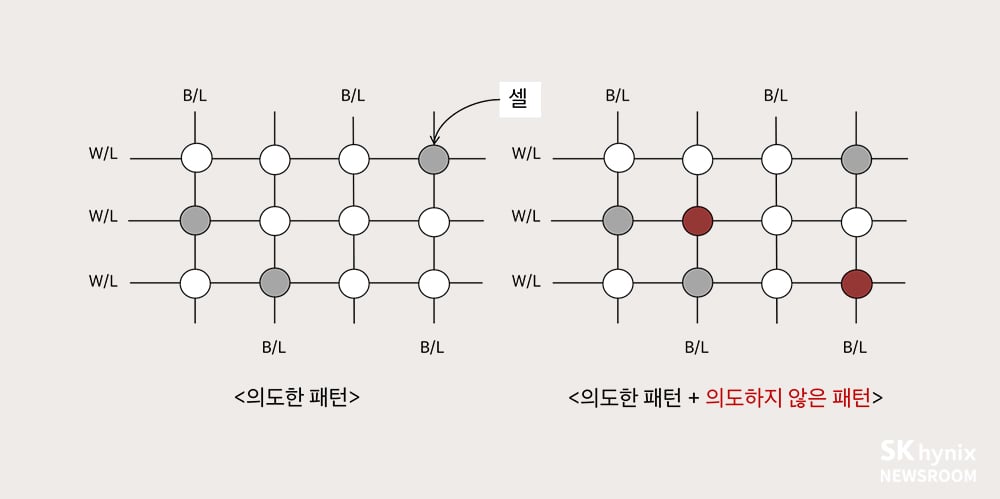

<그림1> 비어 있어야 할 셀에 전자가 유입되어 데이터 오류가 발생하는 경우

교란성 불량이란 선택되지 않은 셀에 일시적으로 혹은 장시간 많은 전자가 유입(Charge)돼 발생하는 문제를 말합니다. 전자가 잘못된 위치의 셀에 유입될 경우 셀-패턴 불량이 발생해, 정상적으로 저장돼 있던 데이터가 엉뚱한 데이터로 바뀌게 되지요. 예를 들어 우리가 사진을 촬영해 스마트폰에 저장하면, 데이터는 일정한 패턴으로 트랜지스터(Transistor, TR)라는 낸드 메모리 셀에 저장되는데요. 이 패턴은 전자들이 저장된 셀과 저장되지 않은 셀의 조합으로 이뤄집니다. 이때 패턴에 변형이 발생하면 데이터가 손상되어 사진이 변형되거나 사라지는 문제가 발생하게 되지요.

2. 교란성 불량의 원인

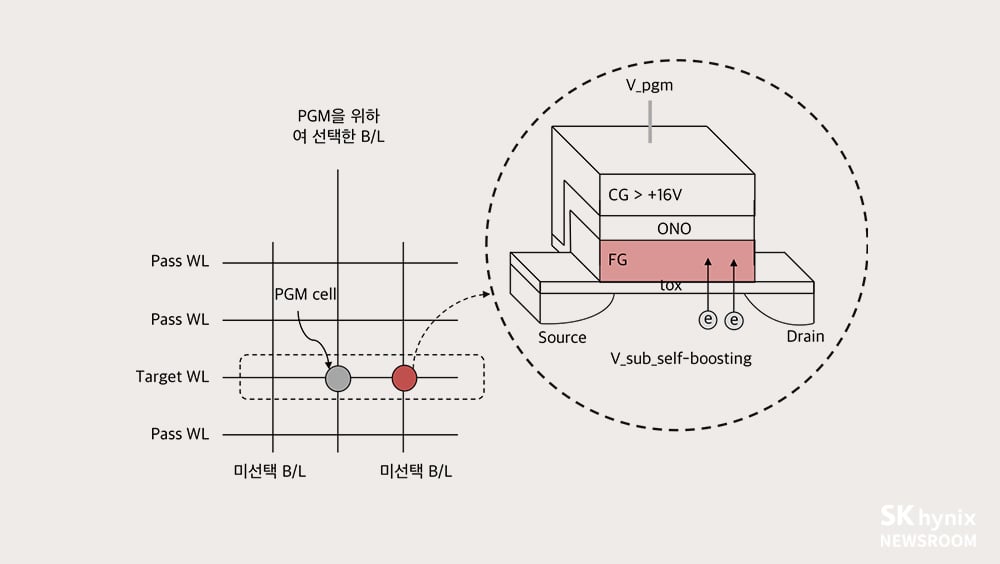

<그림2> 낸드 프로그래밍 동작 시 발생된 Disturbance @출처: NAND Flash 메모리

교란성 불량은 주로 낸드 동작 시 데이터를 저장(Program)하거나 읽는(Read) 과정에서 많이 발생합니다. 특히 데이터를 저장할 때 더욱 빈번하게 나타나지요. 낸드는 데이터 저장 시 내부전압을 VCC(Voltage Common Collector)보다 3~4배 높여 사용하는데요. 이 과정에서 선택된 셀에만 전자를 주입해야 하는데, 간혹 낮은 확률로 선택되지 않은 인접 셀에 전자가 유입되는 경우가 있습니다. 셀을 읽기할 때에는 저장할 때보다 낮은 전압을 사용하지만, 낮은 전압에서도 읽기를 여러 번 반복할 경우 의도치 않게 불필요한 셀에 조금씩 전자들이 누적되어 불량을 야기하기도 합니다.

3. 교란성 불량 셀이 발생되는 동작 메커니즘

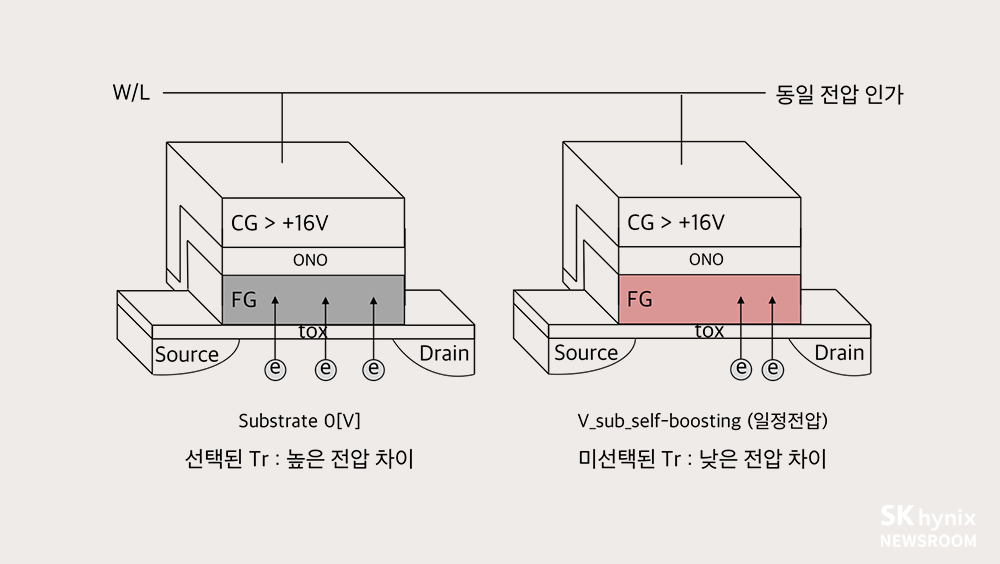

<그림3> 낸드 프로그래밍 동작 시 정상 셀과 Disturbance 셀의 비교 @출처: NAND Flash 메모리

전자를 셀에 주입할 때에는 16[V] 이상의 높은 전압 차를 이용해 여러 번 반복하여 프로그램을 완성시킵니다. 이때 물리적 결함이 있거나 혹은 프로그램이 잘 되는 셀에는 10[V] 이하의 전압 차에도 전자들이 플로팅게이트(Floating Gate, FG)로 주입될 확률이 높습니다. 이러한 동작이 여러 번(최대 수십 번) 반복되며 전자들이 조금씩 셀에 유입되면, 결국 데이터가 바뀌는 수준에 이르거나 혹은 데이터가 바뀔 정도는 아니지만 그 근접까지 전자들이 들어차는 경우(예를 들어 플로팅게이트에 1,000개 전자가 주입되면 데이터가 바뀌지만, 800개 정도까지 유입된 경우)도 발생하게 됩니다.

4. 보존성과 교란성

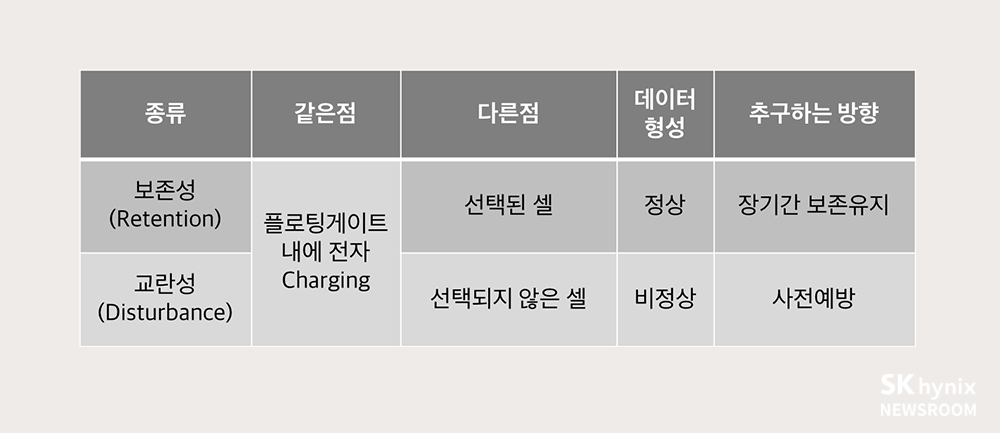

<그림4> Retention과 Disturbance의 유사 특성과 상이 특성

보존성과 교란성은 전자가 FG에 저장된다는 공통점이 있지만, 각각 추구하는 방향은 정반대입니다. 보존성은 셀에 저장돼 있는 전자가 탈출하지 않도록 잘 유지시켜야 하는 반면, 교란성은 저장되지 않아야 할 셀에 전자가 유입되지 않도록 막아야 하지요. 교란성 전자들은 한 번 유입되면 잘 빠져나가지 않아 해결하는 데 어려움이 따릅니다. 따라서 애초에 셀에 불필요한 전자가 유입되지 않도록 사전 방지 조치를 취할 필요가 있습니다.

5. 간섭성 불량이란?

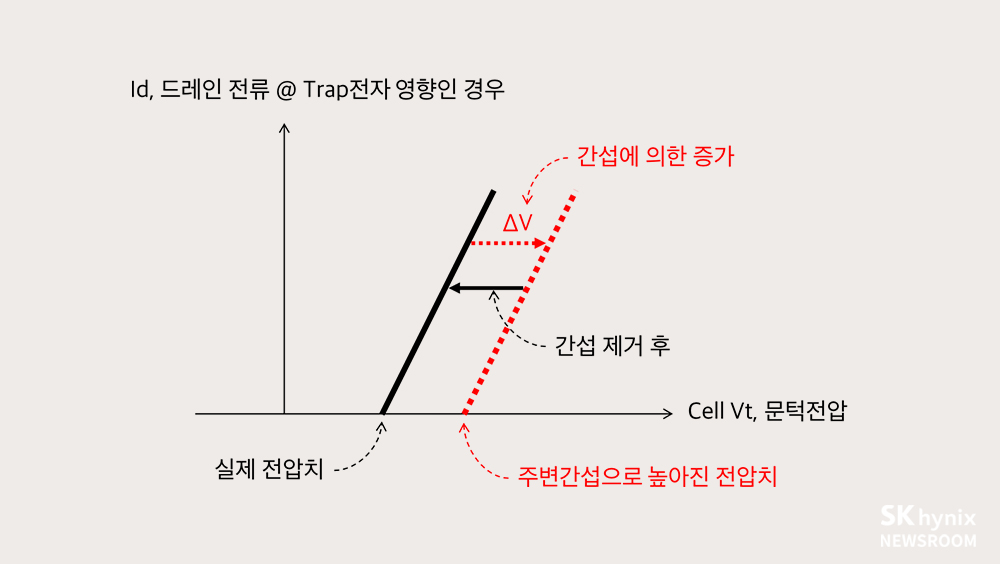

<그림5> 주변 간섭(Trap된 전자)으로 인한 Victim Cell의 전기적 변화 @출처: NAND Flash 메모리

앞서 언급한 교란성은 불필요한 전자가 직접 FG 내 저장되어 전하량을 변화시키는 현상입니다. 반면 간섭성은 Victim 셀(인접한 셀들로부터 영향을 받는 셀)과 일정 거리를 두거나 혹은 셀 밖에서 Victim 셀에 간섭을 끼치는 모든 현상을 말하지요. 이는 셀의 동작에 간접적으로 영향을 끼쳐 데이터, 특히 문턱전압 값을 실제와 다르게 오인(誤認)하게 만듭니다. 간섭성 불량은 전자가 저장된 셀(Program Cell)이건, 전자가 소거된 셀(Erasure Cell)이건 무차별적으로 모든 셀에 셀 주변에서 끼친 전하량만큼 영향을 줍니다. 이는 임시로 트랩(Trap)된 전자들에 의한 유동성이 높기 때문에, 원인(트랩)이 제거되면 당연히 간섭현상도 사라지겠지요. 따라서 교란성 불량은 사전 예방이 중요한 반면, 간섭성 불량은 사전 예방과 더불어 사후 개선 조치도 중요하답니다.

6. 간섭성 불량의 원인

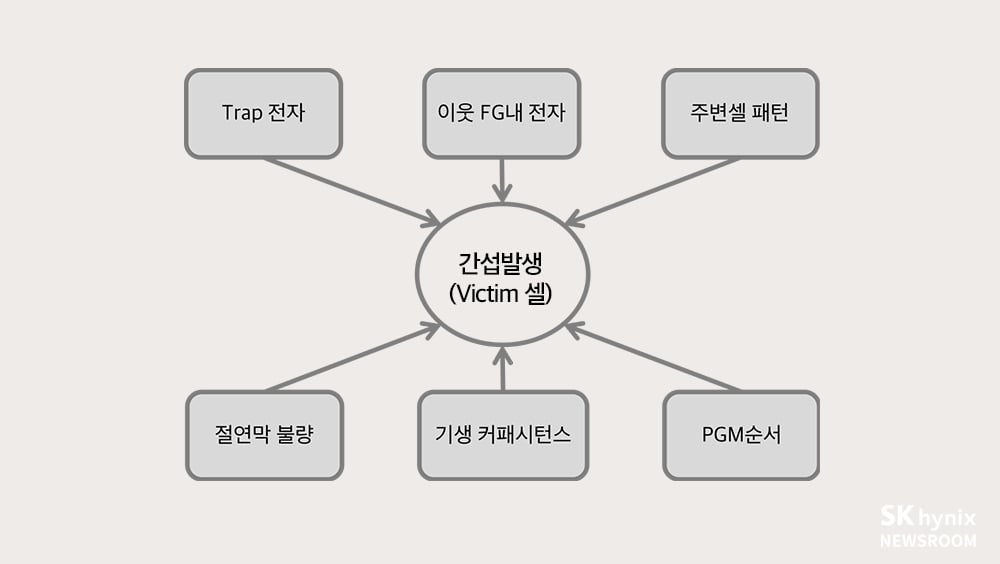

<그림6> Interference의 원인

아직까지 간섭성 불량의 모든 원인을 분명하게 밝히기는 어렵습니다. 또한, 발생 원인은 CD(Critical Dimension)의 피치가 좁아짐에 따라 상대적(같은 전하량일지라도 CD가 클 때는 간섭이 없다가 CD가 작아지면 간섭을 발생시킴)이지요. 지금까지 밝혀진 것에 따르면, 낸드 메모리의 정상적인 동작인 PE사이클링(데이터를 저장하거나 저장된 데이터를 없애는 동작) 후 FG 주변에 남아있거나 트랩된 전자집단, 이웃 FG에 충전된 전자집단, 인접 셀의 패턴에 의해 간섭을 받습니다. 그 외에도 Victim 셀 외부로부터 크랙(Crack)을 타고 들어오는 파동에너지, 워드라인(Word Line) 혹은 비트라인(Bit Line)에 포진된 셀의 형태, 타깃 셀과 주변 셀 간 발생하는 기생 커패시턴스(Capacitance, 정전용량) 혹은 주변 FG 내로 전자가 축적되는 양의 변화도 불량의 원인에 포함됩니다.

7. 간섭을 줄이기 위한 향후 방향

셀과 셀 사이의 간격이 좁아짐에 따라 커패시턴스는 더욱 높아지고 있으며, 이는 셀 간 간섭에 영향을 줍니다. 따라서 절연성 물질을 변화시켜 유전률을 낮추는 것도 해결 방법 중 하나입니다. 또, 절연물질의 크고 작은 파괴가 존재할 경우 절연체 내로 전자들의 트랩이 쉬워지는데요. 이러한 트랩 전자를 줄이기 위해 게이트옥사이드(Gate Oxide)와 기판 사이 계면 처리 및 게이트옥사이드의 데미지 감소를 위한 다양한 방법들이 시도되고 있습니다. 물론 원인을 제거하는 방법도 중요하지만 원인 제거가 불가능하다면, 보상의 차원으로 간섭을 받은 만큼 읽기 동작 시 문턱전압을 +/-하여 읽어내는 스킬을 사용하기도 합니다.

앞서 이야기했듯 교란성 및 간섭성 불량의 원인은 아직 모두 밝혀지지 않았습니다. 반도체 기술이 발전하고 제품이 다변화됨에 따라 잠재돼 있던 불량이 새롭게 수면 위로 떠오르고 있으며, 그에 따라 꾸준하게 원인을 규명하는 작업이 전개되고 있지요. 간섭성 불량과 교란성 불량은 서로 영향을 끼치는 관계이므로, 두 가지 불량을 동시에 해결하는 방법을 찾을 필요가 있습니다.

※ 본 칼럼은 반도체/ICT에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.