반도체 산업의 경쟁력을 높이는 첫 발걸음은 당연히 반도체에 대한 지식을 공유하는 것이다. 이에 본인 역시 반도체 산업에 몸담았던 일원으로서 반도체에 대해 관심이 있거나 반도체 산업에 종사하고자 하는 취업준비생들을 위한 지식을 공유하고자 한다.

인터넷이나 교재에서 찾아볼 수 있는 기술에 치중된 지식이 아니라 각 기술이 가지는 연관성을 통한 관계의 중심으로 반도체를 설명하고자 한다. ‘컴퓨터와 트랜지스터’의 주제를 시작으로 공정과 산화, 포토, 식각, 증착, 금속배선 등 총 6편의 시리즈로 반도체 기술에 대한 설명을 이어갈 예정이다.

이를 읽는 독자 여러분은 개별 용어에 너무 얽매이지 말고 ‘관계’에 주목하길 바란다. 글을 읽다 보면 갑작스럽게 전문 용어들이 등장할 수 있지만, 이해가 되지 않는다면 그냥 넘어가도 좋다. (필자 주)

증착 : 물질 추가하기

우리는 앞서 쿠키를 만들어 가는 과정을 조금씩 살펴봤다. 쿠키 사이에 초코 시럽을 넣기 위해 쿠키 일부를 깎아 냈으므로, 그다음에는 초코 시럽을 바르고 다른 쿠키를 덮어야 함을 알 수 있다. 초코 시럽을 바르는 과정과 다른 쿠키를 덮는 과정이 바로 증착이다.

▲ 그림 1 : 초코 시럽을 바르고 쿠키를 위에 덮는 모습

증착의 진행 과정은 매우 직관적이다. 처리하고자 하는 웨이퍼를 준비한 뒤, 증착 기기에 투입하고 표면에 충분한 두께의 박막이 생기기를 기다리는 것이다. 박막이 생성되고 나면 필요 없는 부분들을 제거한 뒤, 다음 공정을 시행한다.

웨이퍼 표면 물질을 제거하는 공정이 식각 이외에도 여러 종류가 있었듯, 웨이퍼 윗면에 물질을 추가하는 공정 역시 증착 이외에도 많이 있다. 예를 들면, 포토 공정에서 살펴본 포토레지스트 도포 또한 웨이퍼 위에 각종 막질을 씌우는 과정이며, 산화 공정에서 웨이퍼(규소)를 산화시키는 것 역시 웨이퍼 윗면에 물질이 추가되는 과정이다. 그렇다면 증착 공정만을 특별히 중요하게 언급하는 이유가 무엇일까?

바로 반도체 미세화 때문이다. 전자제품의 성능 및 저전력 요구가 높아짐에 따라 반도체에 미세화가 진행돼야 했다. 더 작고 에너지 소비가 적은 반도체를 도입하면 기기에 더 많은 기능을 추가할 수 있기 때문이다. 반도체 미세화가 진행되니 내부에는 각기 다른 역할을 하는 다양한 물질로 구성된 얇은 막이 필요해졌다. 그중 하나가 금속 피막이다. 과거 반도체 회사들은 칩 내부의 금속 배선으로 전도도*가 높은 알루미늄을 사용했는데, 알루미늄의 미세화가 한계에 다다르자 대체 배선 물질로 알루미늄보다 전도도가 높은 구리를 사용하려 했다. 문제는 구리 원자는 알루미늄과는 달리 반도체 회사들이 원치 않는 곳(이산화규소, SiO2)까지 뚫고 확산하는 성질이 있다는 것이다. 이를 방지하고자 구리 배선을 도포할 영역에 구리가 통과하지 못하는 일종의 보호막을 씌우는데, 여기에 고품질 박막이 필요했다.

* 전도도 : 전기가 잘 통하는 성질. 금속 등의 물질이 전도도가 높다.

머리카락 두께 수천분의 일밖에 되지 않는 반도체의 핵심 소자층과 배선층을 만들기 위해서는 굉장히 얇으면서도 균일하게 물질을 추가해야 한다. 증착 기술이 중요할 수밖에 없는 이유다. 본 편에서 언급하는 증착은 일반적으로 반도체 회사에서는 박막(Thin film) 공정으로 불리니 참고 바란다.

박막의 종류와 역할

물질을 추가하는 과정은 반도체 제조에서 매우 중요하다. 반도체는 순수한 실리콘만으로는 작동하지 않는다. 간섭받으면 안 되는 두 영역을 구분 지어야 하고, 연결돼야 하는 곳들은 전선을 통해 연결해야 한다. 필요한 경우, 특정한 막질을 이용해 전기장의 힘을 강하게 주거나, 약하게 주기도 하며, 다음 단계 공정을 쉽게 하기 위해 얇은 막질을 미리 생성하는 등 많은 경우에 필요하다. 이번에는 박막들의 역할 몇 가지를 알아보도록 하자.

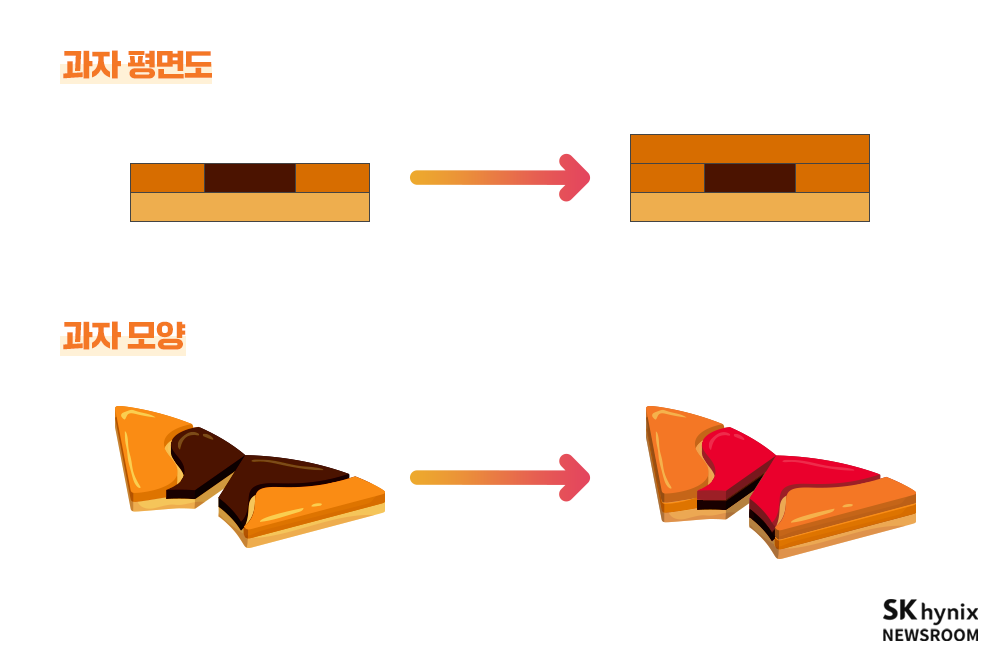

반도체 내 중요한 박막 중 하나는 각종 방어막이다. 회로 간의 경계를 만들어 줌으로써 반도체 핵심 소자들의 간섭과 전류의 누설을 막아 동작 신뢰성을 높이는 것이다. 필요한 경우, 칩을 외부의 충격으로부터 방어하는 막을 제조 공정 마지막에 씌우기도 한다. 혹은 제조 과정에서 반도체를 층층이 쌓은 뒤 식각을 하고자 하는데, 식각 돼선 안 되는 곳이 있다면 식각을 방지하는 용도로 사용되기도 한다. 이러한 구조물의 예가 STI*, IMD*이다. 사용되는 물질들은 이산화규소(SiO2), 탄화규소(SiC), 질화규소(SiN) 등이다.

* STI(Shallow Trench Isolation): 소자 경계부 누설 전류를 방지하는 참호 형태의 보호막

* IMD(Intermetal Dieletric) : 금속 배선 층 사이에 원치 않는 전류 흐름을 막는 보호막

▲ 그림 2 : 소자 경계부의 누설 전류를 방지하는 STI의 모습

또 다른 물질은 금속이다. 반도체 하부 소자(트랜지스터) 층은 존재하는 것 만으로는 아무 의미가 없으며, 다른 소자 및 전원 등과 연결돼야 제 역할을 할 수 있다. 이들을 연결하기 위해서는 티타늄, 구리, 알루미늄 등의 금속 배선이 필요하며, 각 금속 배선과 소자들을 연결해주는 접점(Contact)을 만들어야 한다. 이는 가전제품 내부 전자기판의 소자와 소자를 연결하기 위해 전선을 납땜하는 것과 다르지 않은 과정이다. 기판에 연결된 전선은 반도체 내부의 금속 배선과 같은 일을 하며, 납땜은 반도체 내부의 접점과 같은 역할을 한다.

증착은 그 이외에도 많은 곳에 이용된다. 반도체 제조 과정에서 트랜지스터를 제조할 때 게이트 유전막을 형성하거나, 멀티 패터닝*에 사용하는 하드 마스크를 씌울 때도 사용된다. 앞서 언급한 예시에서 알 수 있듯 증착은 제조의 거의 모든 과정에서 사용된다. 또한, 기존에 증착으로 진행하지 않는 공정을 증착이 대체해버리는 경우도 있다. 이전 편에서 잠깐 설명했듯 게이트 유전막의 경우, 과거에는 산화 공정으로 만들었지만, 미세화가 진행된 현재는 증착 공정을 주로 사용하고 있다. 미세화로 인해 정밀도와 품질이 더욱 중요해졌기 때문이다.

* 멀티 패터닝(Multi Patterning) : 반도체를 더욱 미세하게 만들기 위한 기술. 노광과 식각 공정 등을 여러 번 반복하는 방법이다.

증착 주요 수치 : 균일도, 스텝 커버리지, 갭 필

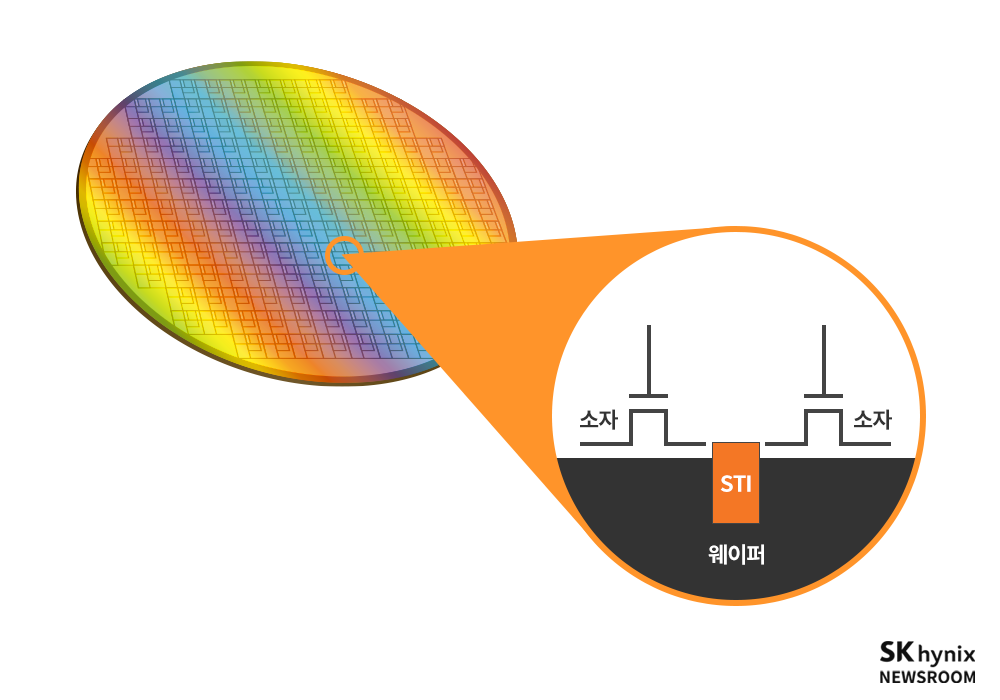

▲ 그림 3 : 높은 균일도와 낮은 균일도의 예시

들어가기에 앞서, 증착 공정의 품질과 관련된 각종 수치를 알아보자. 아마도 단어들을 듣다 보면, 식각 공정에서 들었던 단어들과 상당히 유사함을 알 수 있을 것이다. 첫 번째 단어는 균일도다. 균일도는 증착 과정에서 물질이 얼마나 균일한 두께로 생성됐는지를 표현하는 수치다. 증착 역시 식각과 마찬가지로 웨이퍼 전체를 기기에 넣고 진행하기 때문에, 웨이퍼 지점별로 두께가 다르게 생성될 수 있다. 균일도가 높을수록 전 웨이퍼 영역에 골고루 물질이 도포된다고 생각하면 된다.

다음 수치는 스텝 커버리지다. 산화나 식각 공정에서도 보았듯, 웨이퍼 표면에 단차나 뾰족한 부분이 존재할 경우 박막의 두께가 균일하게 생성되지 않을 수 있다. 스텝 커버리지는 증착이 이뤄지는 울퉁불퉁한 표면의 상단 부분 막질과 하단 부분 막질의 두께 차이, 혹은 상단 부분 막질과 측벽 막질의 두께 차이를 말하는 것이다. 스텝 커버리지가 1에 가까울수록 상단부와 하단부의 차이가 적다는 것이며, 스텝 커버리지가 1보다 작은 경우 하단부나 측벽의 두께가 얇게 생성된다는 의미다.

▲ 그림 4 : 스텝 커버리지(위)와 갭 필 예시 모습(아래)

마지막으로 볼 것은 갭 필(Gap fill)이다. 이름에서 알 수 있듯 빈 공간(Gap)을 얼마나 잘 채우는지를 나타내는 특성이다. 그림에서 볼 수 있듯 제조 중인 반도체 위에는 수많은 요철이 있으며, 증착 과정에서 이 영역들을 꽉 채울 수 있다는 보장이 없다. 갭 필 특성이 좋지 않으면 내부에 공동(Void)이 생기게 되고, 추후 구조물이 무너질 수 있다. 식각에는 원치 않는 부분까지 깎여 나가는 등방성이 있었다면, 증착에는 원하는 곳이 메꿔지지 않는 특성인 갭 필이 있다고 생각하면 된다.

증착의 종류

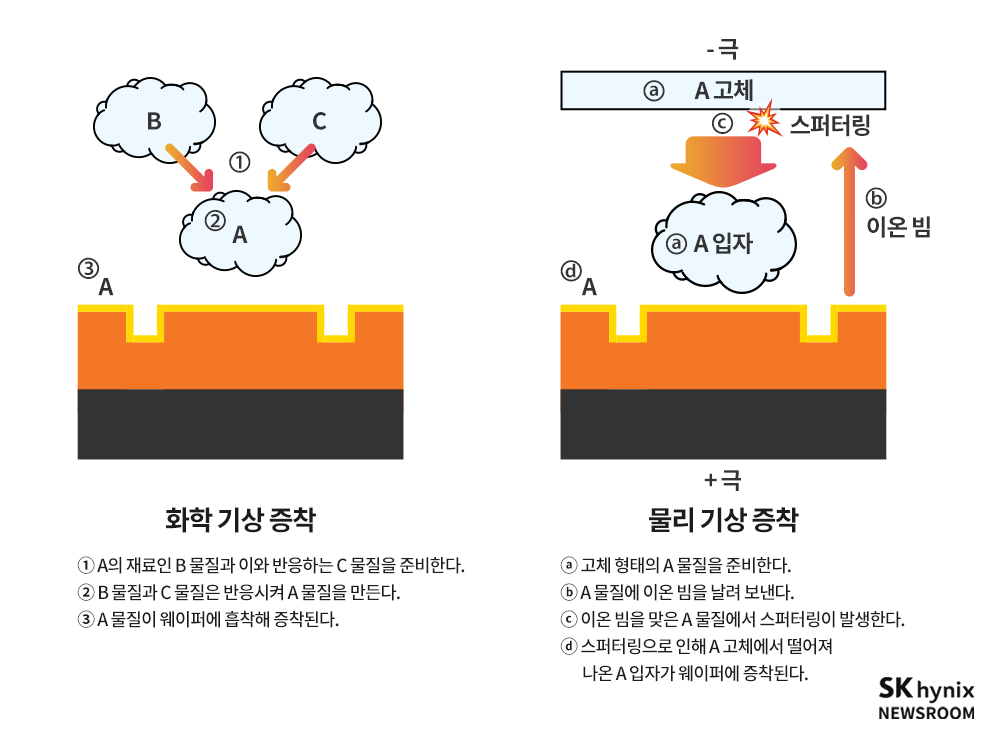

앞에서 봤던 수많은 과정과 마찬가지로, 증착 역시 화학 기상 증착(Chemical Vapor Deposition: CVD)과 물리 기상 증착(Physical Vapor Deposition: PVD)으로 나뉜다. 화학 기상 증착은 웨이퍼 표면에 화학적 방법을 통해 물질을 씌우는 것을 포괄하는 방법이다. 가장 흔한 방식은 혼합 기체에 에너지를 가해주는 방식이다. 표면에 물질(A)을 증착해야 한다고 하면, A를 생성할 수 있는 두 기체(B와 C)를 주입한 뒤, 반응을 일으키기 위해 에너지 등 반응을 촉발하는 무언가를 가해주는 것이다. 즉 아래와 같은 방식으로 물질을 만들어 낸다.

B + C + (에너지 등) → A + 부산물

화학적 방식의 경우 공정 속도가 빠르며, 웨이퍼 위에서 반응이 일어나기 때문에 스텝 커버리지가 우수하다. 하지만 반응 과정에서 부산물 기체가 끊임없이 생겨나며, 이를 공정 진행 과정에서 완벽히 제거할 방법이 없기 때문에 각종 불순물이 섞일 수 있다는 단점이 있다. 각종 불순물이 포함될 수 있기에, 특성 제어가 매우 세밀해야 하는 영역보다는 각종 소모성 막질(하드 마스크)이나, 각종 두꺼운 차단막 생성에 사용된다.

▲ 그림 5 : 화학 기상 증착과 물리 기상 증착의 증착 방법

물리 기상 증착(Physical Vapor Deposition: PVD)은 웨이퍼 표면에 증착하고 싶은 물질을 직접 날려 보내 달라붙게 하는 방법이다. A라는 물질을 증착하고 싶다면, A 물질을 그대로 기화시켜 웨이퍼에 달라붙게 하는 것이다. 주로 사용되는 방식은 식각에서도 살펴봤던 스퍼터링(Sputtering)*이다. A 물질 덩어리인 표적(Target)에 가속된 이온(주로 불활성기체)을 날려 보냄으로써 A 입자가 떨어져 나오게 하는 것이다. 떨어져 나온 A 입자는 반대 방향으로 가속돼 웨이퍼에 증착되게 된다.

* 스퍼터링(Sputtering): 높은 에너지를 특정 물질에 충돌시켜 물질 표면이 떨어져 나가게 하는 물리적 방법

이 방식의 장점은 부산물 기체라는 것이 없으므로 물질의 순도가 매우 높다는 것이다. 또한 반응성이 없는 순수 물질들도 증착할 수 있다. 예를 들면, 순수한 텅스텐(W), 코발트(Co) 등도 증착이 가능하다. 이러한 특성 덕분에, 물리 기상 증착은 순수 물질이 많이 사용되는 금속 배선을 만들 때 주로 사용된다.

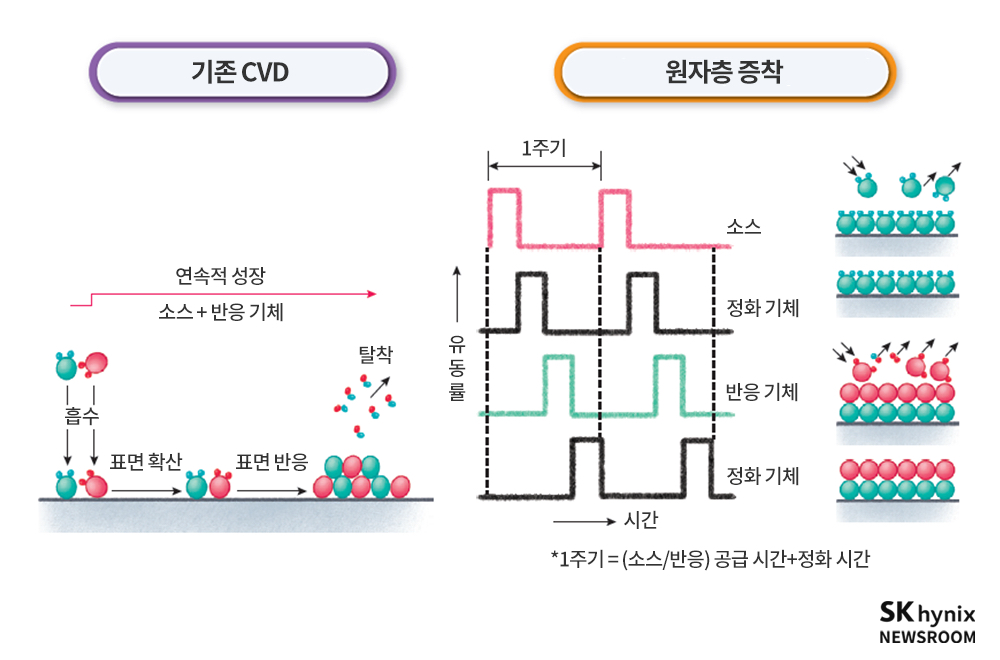

한 가지 독특한 예로 원자층 증착(Atomic Layer Deposition: ALD)이 있다. 우리가 위에서 살펴본 공정들은 활성화된 기체를 웨이퍼 표면에 화학적으로 붙이거나, 이온을 강하게 가속해 강제로 붙이는 방법이었다. 하지만 ALD 공정은 이것과는 조금 다른 방식으로 이뤄진다. 물질 A를 매우 얇게 웨이퍼 표면에 증착하고 싶다고 가정해보겠다. 이를 위해 A의 재료인 반응물질 2개(B와 C)를 준비한다. 단, 여기서 B는 웨이퍼 표면에 흡착이 잘 되는 물질(전구체, Precursor)이며, C는 반응성이 높은 물질이다. 일단 웨이퍼 표면에 B를 흡착시킨다. 만약 B가 자기들끼리는 잘 달라붙지 않는 특성이 있다면, B 물질은 원자 1개 층만 웨이퍼 표면에 남을 것이다. 이후에는 잔여 B 기체를 제거해준 뒤, C 기체를 투입한다. 그러면 B와 C가 반응해 A가 생기고, 부산물 가스가 생긴다. 이후 A와 부산물 가스를 제거한다. 이 과정을 반복하면 막의 두께를 원자 단위로 제어할 수 있다.

▲ 그림 6 : 기존 화학 기상 증착(CVD)과 원자층 증착(ALD)의 개념 (출처:㈜도서출판한올출판사 [반도체 제조기술의 이해 293p])

이 방식은 균일도와 스텝 커버리지가 우수하다는 큰 장점이 있다. 전구체 물질의 특성상 수직, 수평 등 다양한 곳에 달라붙을 수 있을 뿐만 아니라, ALD 한 주기당 단 1개의 원자층만 생성되기 때문이다. 하지만 원자층 단위로 작업을 하므로, 진행 속도가 느리다는 단점 역시 존재한다. 이런 특성 때문에 ALD 공정은 D램의 커패시터 등 종횡비*가 높은데 고품질의 막질이 필요한 부위에 주로 사용된다.

* 종횡비: 기둥 아랫면과 높이의 비율. 종횡비가 높다는 것은 구조물의 폭이 좁은데 높다는 의미

위의 예시를 보면 증착 역시 다른 공정들과 유사한 상충관계가 나타남을 알 수 있다. 균일도 등의 정밀성을 높이는데 필요한 특성을 개선하기 위해서는 처리 속도를 포기해야 한다는 것이다. 반도체 제조는 정밀도와 처리 속도 사이에서 끊임없이 고민해야 하며, 이는 증착 공정도 피해 갈 수 없다.

압력과 온도

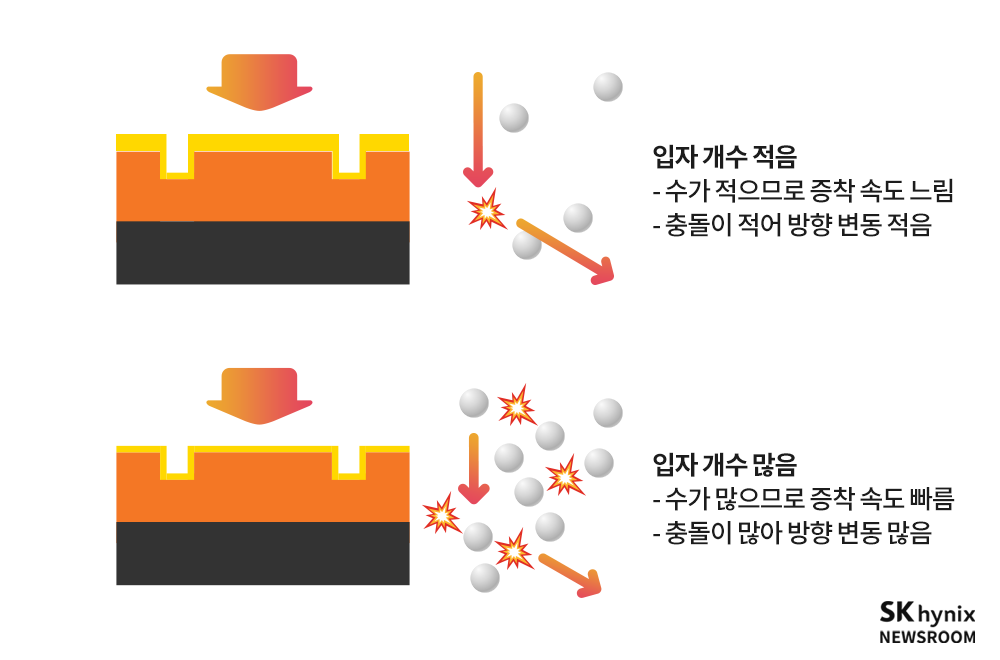

식각과 마찬가지로, 반도체 회사들은 증착 과정에서 온도와 압력 등 다양한 요소들을 제어함으로써 원하는 품질의 막을 얻어낸다. 예를 들면 증착 과정에서 낮은 기압을 사용하면 막의 생성 속도가 느려지는 대신, 막의 수직 방향 증착을 강화할 수 있다. 기압이 낮다는 것은 기기 안에 반응 기체 개수가 적다는 의미이기 때문이다. 기체의 수가 적다면 기체 간의 충돌도 적어지므로 직진성이 높아지는 것이다. 높은 온도를 사용할 경우 막의 순도가 높아지지만, 알루미늄과 같이 녹는 점(550도)이 낮은 금속이 전 단계 공정에서 사용됐다면 문제가 생기게 된다.

▲ 그림 7 : 압력이 증착에 미치는 영향

이러한 특징으로 인해 같은 물질이더라도 필요에 따라 완전히 다른 방식으로 증착하기도 한다. 예를 들어, 같은 이산화규소(SiO2)더라도 게이트 절연막을 만들 때와 STI를 만들 때 원하는 특성이 다르다. 게이트 절연막은 핵심 소자 부위이기 때문에 고품질을 위해 고온, 저압 공정을 사용하지만, STI는 두 소자 경계부에서 절연체의 역할만 하면 되기 때문에 저온, 고압의 공정을 사용해 빠른 처리 속도에 집중한다.

소재 선택의 어려움

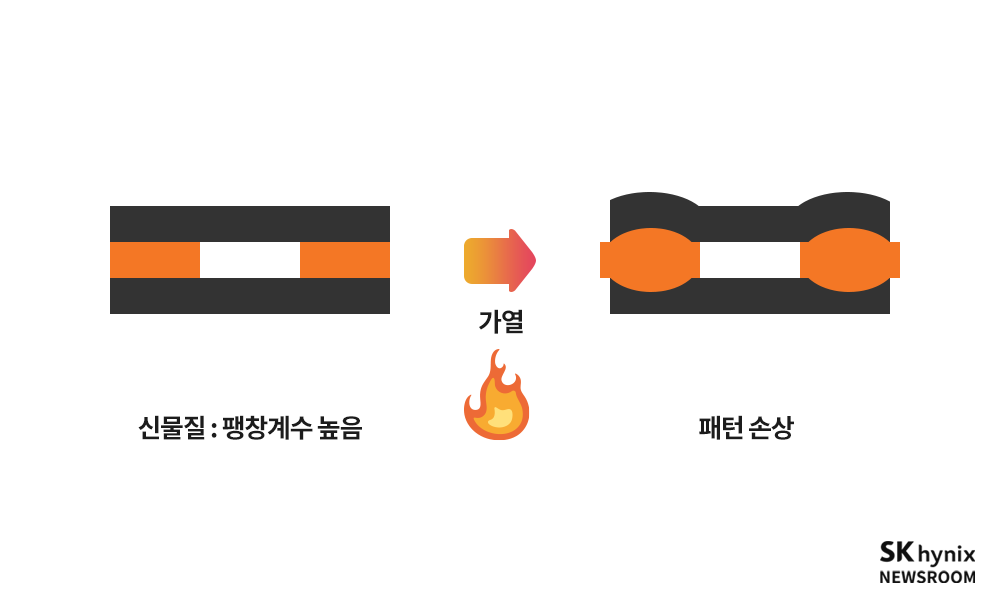

때때로 우리는 ‘특성이 OO 배 좋은 신물질을 발견했다.’ 등의 뉴스를 보곤 한다. 뉴스의 내용만 봐서는 반도체의 혁신이 일어날 것 같지만, 뉴스에 등장한 신기술이 현장에 적용되는 예는 생각보다 많지 않다. 그 이유는 개별 소재의 좋은 특성이 반드시 좋은 반도체로 이어지지는 않기 때문이다. 증착 기기에 요구되는 특성만큼이나 증착 소재에 요구되는 특성도 매우 다양하다. 이번에는 소재의 특성들이 제조에 미치는 영향을 일부 살펴보도록 하자.

▲ 그림 8 : 열팽창으로 인한 패턴 손상

물질은 열을 받으면 조금이라도 크기가 변하는데, 이를 열팽창이라고 한다. 전철 선로 사이에 틈이 있는 이유는 열팽창으로 인해 여름에 선로가 휘어지는 것을 막기 위해서이다. 반도체 제조 역시 현실 세계에서 이뤄지는 일이므로 열팽창이 생긴다. 문제는 각 소재들이 열팽창을 일으키는 정도가 다르다는 것이다. 예를 들면, 알루미늄의 열팽창 계수는 산화 실리콘의 40배가 넘는다. 극단적 예로 산화 실리콘 위에 알루미늄 박막을 만들었는데, 이후 고온 공정이 적용될 경우 증착 시에는 잘 만들어졌던 내부 구조가 휘면서 망가질 수 있다. 기존에 특정 박막에 쓰던 물질을 팽창 계수가 크게 다른 물질로 바꿀 경우 고온에서 제조 수율이 크게 변할 수 있는 것이다.

▲ 그림 9 : 일렉트로마이그레이션의 개념

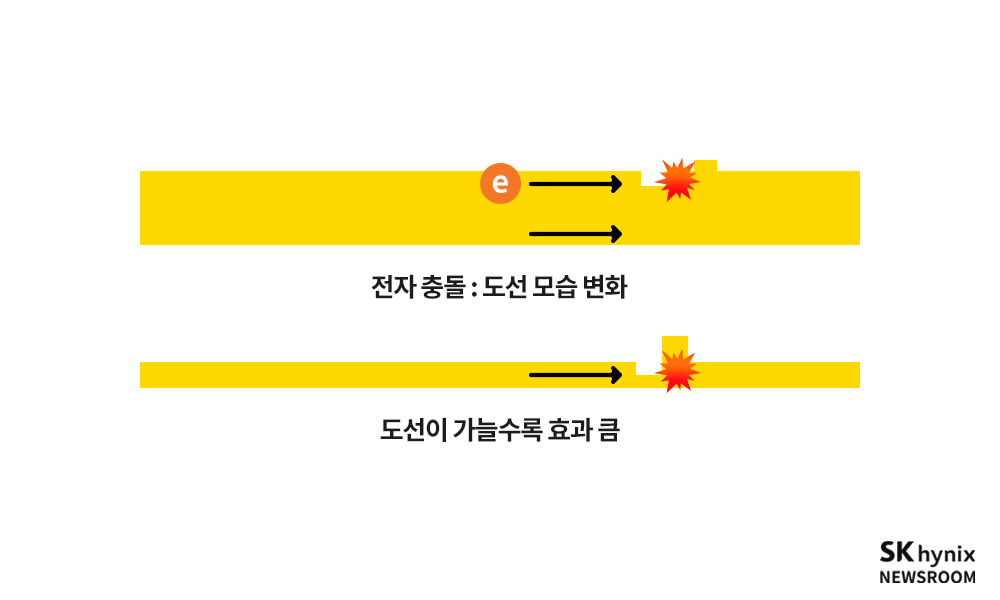

일렉트로마이그레이션(Electromigration, EM)이라는 현상도 존재한다. EM은 금속배선에 전류가 흐를 때, 움직이던 전자들이 금속배선 원자를 때려 위치를 바꿔버리는 현상이다. 이런 현상은 알루미늄 등 경금속 배선에서 주로 발생한다. 이 현상을 피하고자 구리 배선을 도입했고, 이 과정에서 위에서 살펴봤듯 확산 방지막이 필요해지는 등 온갖 추가 공정이 생겨났다. 미세화가 더 진척되자 EM은 구리 배선에서도 나타났으며, 이를 해결하기 위해 인텔은 금속층에 코발트 배선을 사용하기도 했다. 핵심 배선층의 물질이 변화했으니 해당 층의 위아래 층에서 어마어마한 공정 변화가 발생했을 것이다. EM 특성을 개선하고자 했더니 공정에 큰 변화가 필요해진 것이다.

반도체 제조는 수백 개 프로세스가 매우 밀접하게 조합돼 돌아가는 것임을 잊어서는 안 된다. 신소재가 좋은 물질인지 아닌지는 소재 자체의 특성뿐만 아니라, 그 이후에 사용해야만 하는 다른 공정들과의 관계도 고려해야 한다. 증착된 물질은 홀로 존재하지 않는다.

결론 : 다양한 방법으로 만들어지는 물질

여러분이 여기까지 잘 따라왔다면, 아마 흥미로운 점 몇 가지를 발견했을 것이다. 일단 가장 눈에 띄는 것은, 한 가지 물질을 만드는 데 여러 가지 방법을 사용할 수 있다는 것이다. 이산화규소(SiO2)는 산화 공정으로도 만들 수 있지만, 증착을 통해서도 만들 수 있다. 같은 물질이라도 다른 과정을 통해 반도체에 추가되면, 물리적 특성 등이 완전히 달라지기 때문이다.

산화, 식각, 증착 등 완전히 다른 과정으로 생각했던 공정들이 생각보다 많은 것을 공유하고 있다는 것 역시 알 수 있다. 물리적 식각에서 사용된 스퍼터링은 증착에서도 사용된다. 차이가 있다면 ‘스퍼터링으로 웨이퍼 자체를 깎아 내느냐?’ ‘스퍼터링으로 한번 깎아낸 물질을 웨이퍼에 가져다 붙이냐?’의 차이뿐이다. 화학적 식각에서 중요한 요소 중 하나는 식각 기체와 반응 물질이 만나 생긴 부산물이 기화되는지 아닌지였다. 화학 기상 증착에서 발생하는 부산물 역시 기화가 잘 되고 배출이 용이해야 공정 진행이 유리하다.

미래의 후배님들이 이 글을 읽고 있다면, 연구개발 과정에서 위와 같은 점들을 염두에 뒀으면 한다. 반도체 회사가 선호하는 신물질은 단순히 특성 물성이 좋은 물질이 아니다. 물질 증착 속도와 순도 등을 통제하기 쉬울수록 공정에서 선택지가 많아진다. 그리고 증착된 물질은 원할 경우 식각, CMP* 등을 통해 쉽게 제거되는 편이 좋다. 물질 증착 과정에서 지나치게 높은 온도가 필요하면 기존에 증착된 물질을 변화시킬 수 있으며, 온도에 지나치게 민감한 물질을 사용할 경우, 다음 단계 공정에서 열을 쓰기 힘들어지게 된다.

* CMP : 물리, 화학적 연마 공정. 웨이퍼 표면을 갈아 내서 물질을 제거하는 공정

반도체 제조는 수백 개의 제조 공정을 모아 하나의 제품을 만드는 과정이다. 이를 잘 해내기 위해서는 연관 조직 업무에 대해 이해해야 할 뿐만 아니라, 타인과 자연스럽고 정확하게 소통하는 능력 등이 필요함을 알 수 있을 것이다. 많은 사람이 함께하는 협업인 만큼 힘들지만, 그 가치는 매우 높고 보람찰 것이다.

※ 본 칼럼은 반도체/ICT에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.