AI(인공지능)의 활용이 확대되면서 데이터센터를 비롯해 AI 서버 등에서는 차세대 메모리 제품 수요가 늘어나고 있다. 차세대 메모리 제품은 고용량, 고속 연산, 고성능, 저전력의 특성이 있으며, SK하이닉스를 비롯한 세계적인 메모리 기업들은 역동적이고 혁신적인 차세대 메모리 제품을 개발하며 선의의 경쟁을 펼치고 있다. 특히 SK하이닉스는 D램과 낸드플래시(NAND flash, 이하 낸드) 두 분야에서 최고 수준의 기술 경쟁력을 갖추고 있는데, 이는 지난 2년간 메모리 가격이 내려갔음에도 불구하고 과감한 R&D 투자와 기술개발을 위한 노력이 있었기에 가능한 결과라고 생각한다. 이번 기고문에서는 2편에 걸쳐 D램과 낸드의 기술 동향을 살펴보고 도전적인 과제와 전망도 함께 이야기할 예정이다.

D램의 기술 동향과 전망

40여 년의 역사가 있는 D램 기술은 다양한 곳에서 활용되고 있다. 제품별로 구분해 보자면 ▲컴퓨터의 메모리로 사용되거나 DIMM(Dual In-line Memory Module) 디바이스에 적용되고 있는 DDR5 ▲더 낮은 전력을 사용하는 모바일용 D램인 LPDDR5/5X ▲그래픽 전용 D램인 GDDR6/6X ▲AI 등에 활용되고 있는 고대역폭 메모리 HBM3/3E ▲동작 속도를 증가시킨 LLDRAM(Low Latency DRAM) ▲캐시 메모리용 D램인 eDRAM(embedded DRAM) 등이 있다.

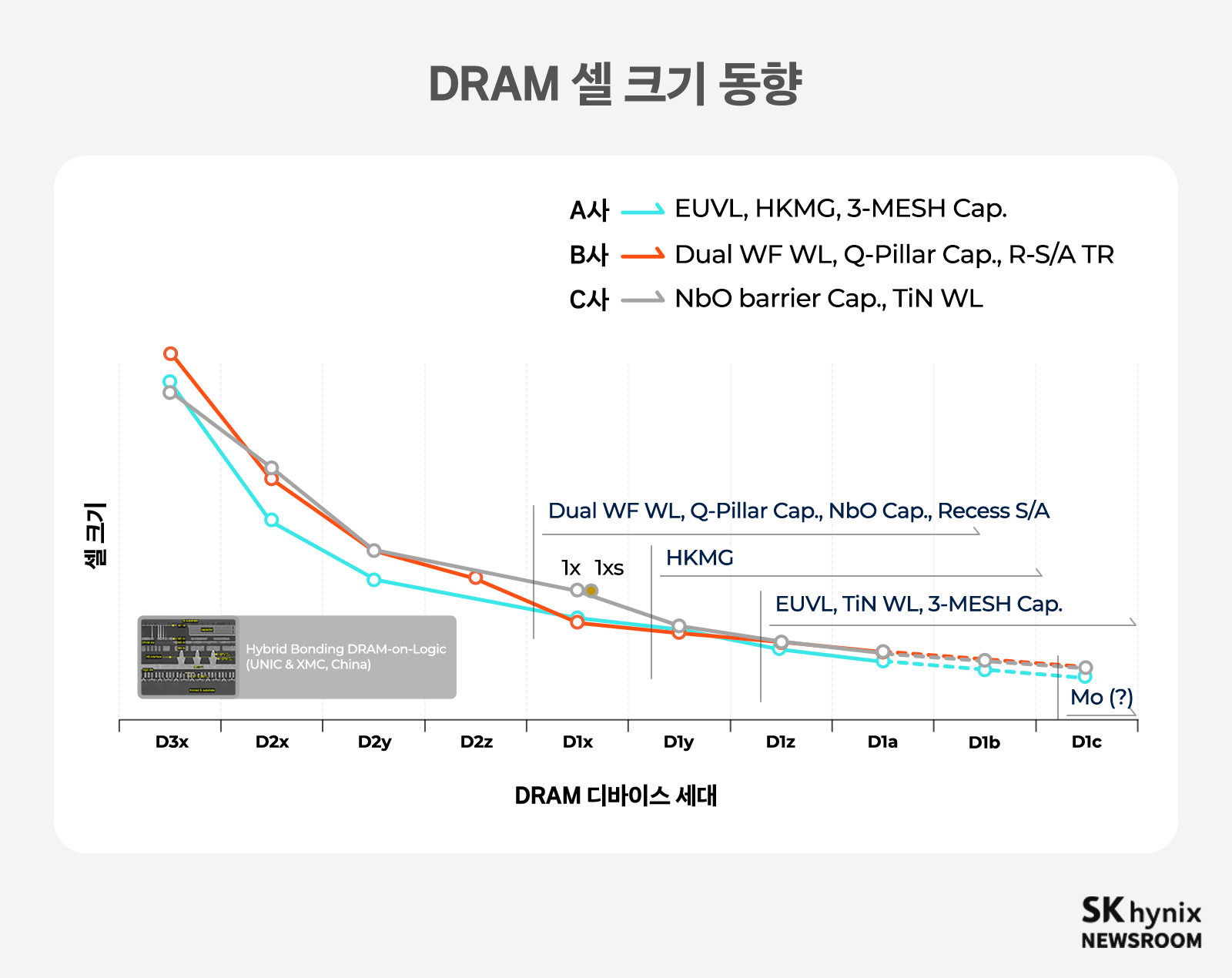

D램 회사들은 지속해서 셀 디자인 룰*을 줄여 왔으며, 현재는 1a(1-alpha, 14nm급)와 1b(1-beta, 12~13nm급) 제품을 상용화했다. 또한 1c(1-gamma, 11~12nm급) 이하의 제품 개발도 진행하고 있으며, 비트(bit) 밀도 증가, 비트라인(Bit Line, BL) Sensing Margin(ΔVBL) 개선, 셀 정전용량(Cell Capacitance, CS) 증가, 기생 용량(Parasitic Capacitance) 감소, 한 자리 수 노드(Node) 향(向) 3D D램과 4F2 셀과 같은 새로운 아키텍처 개발을 위한 노력도 이어지고 있다.

* 디자인 룰(Design Rule, D/R): 물리적인 회로 구조에서 설계의 기준이 되는 최소 치수

현재의 6F2 D램 셀 디자인(실제 셀 크기 = 7.8F2)의 미세화(Scaling)를 위해 각 회사는 제품별 세대마다 혁신적인 신기술을 적용해 왔다. 예를 들어, ▲EUV Lithography(EUVL)* ▲High-K Metal Gate(HKMG)* ▲Dual Workfunction(WF) Word Line* ▲One-Sided(or Quasi-pillar) 캐패시터 공정* ▲Recessed 채널 Sense Amplifier(S/A) Transistors* ▲NbO Barrier Adoption* ▲TiN Word Line* 등은 최근 몇 년간 적용되어 온 혁신 기술들이다.

* EUV Lithography(EUVL): 극자외선 노광 기술

* High-K Metal Gate (HKMG): 유전율(K)이 높은 물질을 D램 트랜지스터 내부의 절연막에 사용해 누설 전류를 막고 정전용량(Capacitance)을 개선한 차세대 공정

* Dual Workfunction(WF) Word Line: 이중 일함수 박막으로 구성된 워드라인. 여기에서 일함수는 진공준위-자유전자의 위치 에너지와 페르미 레벨의 에너지 차이, 즉 물질의 전자를 떼어내 전류가 흐를 수 있게 하는 자유전자로 만들 수 있는 에너지의 양을 말한다.

* One-Sided(or Quasi-pillar) 캐패시터 공정: 기존의 실린더형 캐패시터는 실린더의 내부 면과 외부 면을 모두 활용하지만, 해당 공정은 내부 면은 사용하지 않고 실린더의 외부 면만을 셀의 캐패시터로 사용한다.

* Recessed 채널 Sense Amplifier (S/A) Transistors: 함몰형 채널 구조를 갖는 감지 증폭 트랜지스터

* NbO Barrier Adoption: 니오비움 옥사이드 확산방지막 채택

* TiN Word Line: 타이나이트라이드 막질로 구성된 워드라인

이러한 여러 신기술 중에서 Dual WF Word Line, One-Sided 캐패시터 공정, 그리고 Recessed 채널 S/A Transistors가 D램 제품에 적용되고 있으며, EUVL 기술 역시 본격적으로 적용되기 시작했다. 또한 워드라인(Word Line)과 비트라인(Bit Line)의 저항 감소와 공정 개선을 위해 루테늄(Ru), 몰리브덴(Mo) 등을 포함한 여러 신재료의 개발이 진행되고 있다. 하지만 이러한 노력에도 불구하고 현재의 BCAT 셀*에 대한 미세화는 7~8nm 기술 노드에 해당하는 0b(8~9nm급) 또는 0c(7~8nm급) 급에서 한계에 이를 것으로 예측된다. 이 때문에 추가적인 개선 방안과 함께 새로운 D램 아키텍처가 절실하게 필요한 상황이다.

* BCAT 셀(Buried Channel Array Transistor Cell): 채널의 길이를 증가시켜 주기 위해 소스와 드레인 사이에 매립형 또는 함몰형 채널을 만들고 이를 활용한 기술

이를 위해, High-NA EUV 도입, X-D램을 포함한 여러 종류의 3D D램, 4F2 Cell*, Capacitorless D램* 등의 구조 평가와 공정 통합이 주요 메모리 반도체 기업들을 중심으로 개발되고 있다. 물론, 새로운 구조 평가 이외에도 제품의 성능 향상과 전력 개선을 위해 추가적인 클록킹 기능 개선 등 회로, 설계 및 동작 개선도 병행하고 있다.

* 4F2 Cell: 1T1C(한 개의 트랜지스터와 한 개의 캐패시터로 구성된) D램 셀을 레이아웃 상에 디자인할 때 워드라인 방향으로 최소선폭(F, Feature 크기라고 함)의 두 배인 2F, 그리고 비트라인 방향으로 최소선폭의 두 배인 2F를 각각 사용한 방법을 의미한다. 현재는 워드라인 방향으로 3F를 사용하는 6F2 Cell을 사용하고 있다.

* Capacitorless D램: 1T1C(한 개의 트랜지스터와 한 개의 캐패시터로 구성된) D램 셀에서 캐패시터를 사용하지 않고 트랜지스터만으로 셀을 구성하는 1T (또는 2T) D램을 의미한다.

▲ 그림 1: D램 셀 크기 동향 및 BIG-3의 세대별 주요 D램 기술 개발 동향 (출처: TechInsights Report AME-2304-801 published on July 17, 2023)

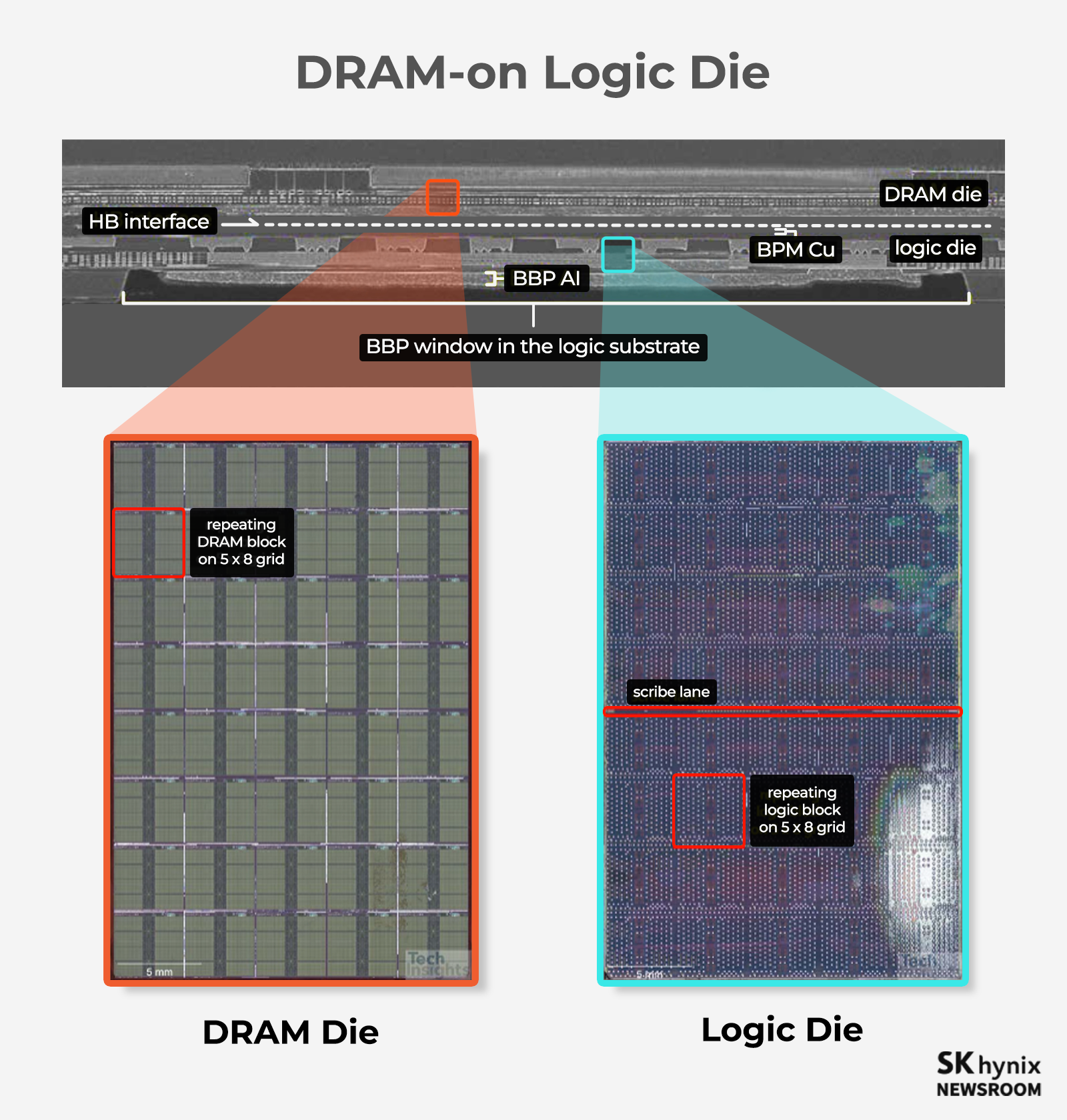

D램 공정 개발 측면에서 ▲지속적인 셀 크기 감소 ▲HKMG를 포함한 페리 영역의 게이트 공정 ▲셀 워드라인 및 비트라인의 신재료 적용 ▲EUVL 패터닝 적용 확대 ▲캐패시터 고유전율 막질 개선 및 신물질 개발 ▲차세대 3D D램 또는 4F2 D램 셀의 안정적 공정 확보 등이 단기적인 중점 과제 항목이 되고 있다. 중장기적으로는 ▲고용량 하이브리드 본딩* D램 칩 개발과 ▲고층 HBM D램 다이 패키지기술 개발 등이 더욱 필요한 상황이다. 하이브리드 본딩 D램-온-로직(DRAM-On-Logic) 구조는 이미 ‘Sunlune Bitcoin ASIC JASMINER-X4 BRICK Ethereum Miner’ 제품에 적용돼 상용화되기도 했다. 물론 여기에 사용된 CMOS 로직 칩은 중국 업체의 40nm급이며 D램 칩은 27nm급이 적용돼 상대적으로 과거의 제품들이 적용됐지만, 하이브리드 본딩 기술을 D램에 적용해 상용화했다는 점에서 의미가 크다고 할 수 있다.

* 하이브리드 본딩(Hybrid Bonding): 두 가지 유형의 계면(면과 면 사이의) 본딩**이 동시에 형성되는 것을 말하기 위해 사용된다. 하나는 산화물 면과 면 사이의 본딩이고, 다른 하나는 구리와 구리 사이의 본딩이 동시에 일어난다.

** 계면 본딩(Interfacial Bonding): 상호 접촉하는 두 물체의 표면이 분자 간 힘에 의해 결합하는 본딩 형태를 뜻한다.

▲ 그림 2: D램-온-로직 하이브리드 본딩 기술을 적용한 ‘Sunlune Bitcoin ASIC JASMINER-X4’ (출처: TechInsights Report AME-2304-801 published on July 17, 2023)

최근 AI에 대한 관심이 높아지면서 함께 주목받는 HBM은 저전력과 고대역폭이 특징인 D램 제품이다. 뛰어난 성능으로 수요가 폭발적으로 늘어나면서 ‘프리미엄 메모리’로 불리고 있다. HBM 제품 개발 및 시장 점유율 측면에서는 SK하이닉스가 지속해서 시장을 주도하고 있다. 주요 SoC 업체에서 출하되는 많은 AI GPU 제품에 SK하이닉스의 HBM이 적용되고 있다.

HBM 관련 기술에는 TSV* 기술, 균일한 전력 배분, 발열, 마이크로 범프* 인터페이스 공정, I/O 수 증가 등이 있으며, HBM 메모리 패키지 측면에서 보면 메모리와 프로세서 코어 사이의 신호 이동 거리를 줄이는 기술과 전력 사용 감소, 사이클 당 소요 시간 감소 역시 지속해서 개발해야 하는 과제들이다. 특히, TSV 기반의 TC NCF*와 MR-MUF* Interconnection 기술에 하이브리드 본딩 기술을 접목할 수 있다면 앞으로 한층 뛰어난 성능의 제품을 개발할 수 있을 것으로 전망된다. 또한, 기존 컴퓨팅의 근간이 되는 폰 노이만 구조*의 한계를 뛰어넘을 수 있도록 하는 PIM(Processing-In-Memory), CiM(Computing-in-Memory), AiM(Accelerator-in-Memory)과 같은 제품의 개발을 확대하고 있는 현재 상황에서는 더 향상된 기술이 필요하다. HBM 및 GDDR 기반의 AI 향 메모리 패키지 기술과 CXL-메모리 등의 고속 메모리 기술도 함께 개발돼야 할 필수 기술로 꼽히는 이유다.

* TSV(Through-Silicon Via): D램 칩에 수천 개의 미세 구멍을 뚫어 상하층 칩의 구멍을 수직 관통하는 전극으로 연결하는 기술. SK하이닉스는 TSV 기술을 활용해 최대 1.15TB/s(초당 1.15테라바이트) 데이터 처리 속도를 가진 HBM3E를 개발했다.

* 마이크로 범프(Micro Bump): 수직 적층된 칩과 회로를 연결할 때, 각 칩의 가교 역할을 하는 소재

* TC NCF(Thermal Compression Non Conductive Film): 칩 사이에 NCF(에폭시와 아크릴 소재가 섞인)라는 절연 필름을 덧대고, 이를 열과 압력을 가해 위쪽을 꾹 눌러서 붙여 절연 필름이 녹아 접착되는 공정

* MR-MUF(Mass Reflow Molded Underfil): 반도체 칩을 쌓아 올린 뒤 칩과 칩 사이 회로를 보호하기 위해 액체 형태의 보호재를 공간 사이에 주입하고, 굳히는 공정

* 폰 노이만 구조(Von Neumann Architecture): 메모리와 연산 장치, 입출력 장치 등 전형적인 3단계 구조로 이루어진 프로그램 내장형 컴퓨터 구조. 오늘날 사용하고 있는 일반적인 컴퓨터의 기본 구조