반도체 메모리 디바이스의 대표주자, 디램(DRAM)과 낸드플래시(NAND Flash). 각각 저장 방법에 따라 응용 분야는 다르지만 데이터를 되도록 많이 저장하고, 빠르게 처리해야 한다는 목표는 동일합니다. 하지만 이 두 가지 목표를 한꺼번에 만족시키는 최적의 디바이스란 없죠. 그럼에도 불구하고 Technology가 고도화될수록 용량과 속도, 두 Index는 개별적으로 꾸준히 개선되고 있습니다. 낸드플래시는 디램에 비해 플로팅 게이트(Floating Gate)의 기여로 집적도를 크게 올릴 수 있지만, 동시에 플로팅 게이트의 영향으로 동작 속도는 떨어집니다. 반면, 디램은 캐패시터가 MOS 트랜지스터(Tr)와 분리되어 있어 집적도는 떨어지지만 스위칭 속도는 매우 빠릅니다. 두 디바이스 모두 장점이 단점을 부르는 동시에 단점이 장점을 부르는 격이 되는 것이죠. 오늘은 디램과 낸드플래시는 어떠한 차이점을 갖는지, 두 디바이스를 서로 비교해보며 알아보는 시간을 갖도록 하겠습니다.

메모리의 스위칭 기능과 저장 기능

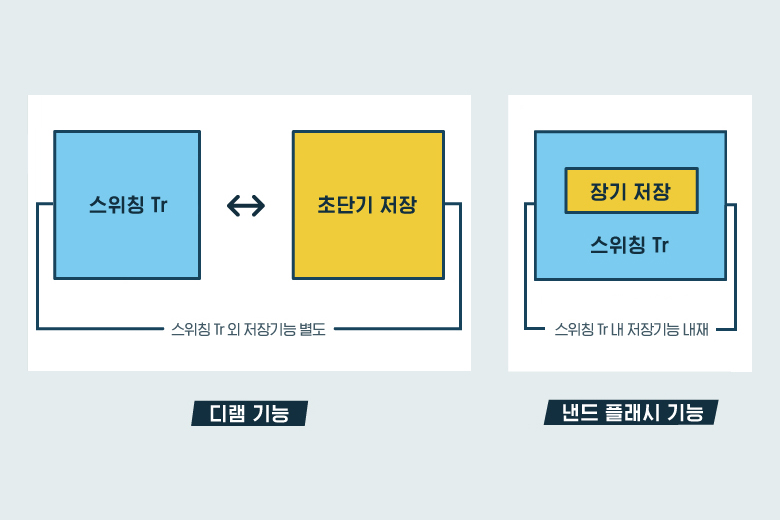

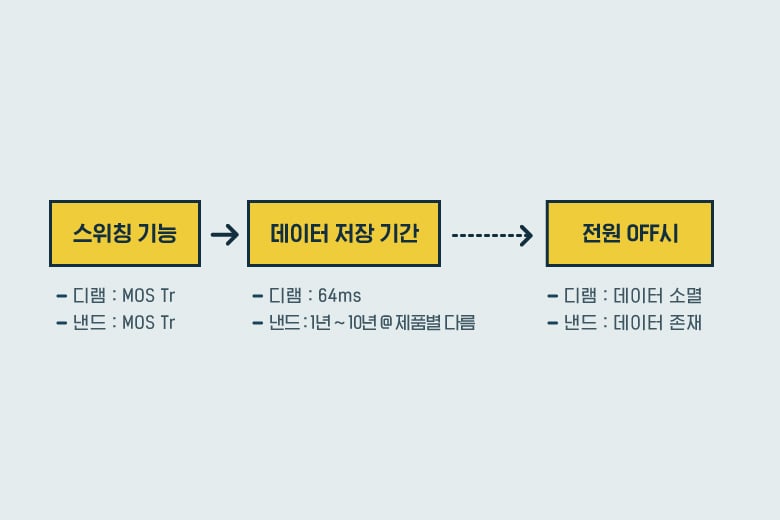

▲ DRAM과 NAND의 스위칭과 저장 기능

메모리 반도체는 어떤 디바이스든 모두 스위칭 및 데이터 저장 기능을 갖습니다. 스위칭 기능은 창고에서 데이터 집단을 받을 것인지 받지 않을 것인지의 여부를 결정하는 문(door)의 여닫이 역할을 하고, 데이터 저장 기능은 말 그대로 데이터를 쌓아두는 창고 역할을 하지요.

스위칭 동작에 있어서는 디램이 훨씬 빠르지만, 데이터 저장 기능에서는 낸드플래시가 월등합니다. 디램은 64ms(1,000분의 1초) 동안만 저장할 수 있는 반면, 낸드플래시는 디램과 비교했을 때 저장기간이 상상을 초월합니다. 제품별로 다르지만, 저장하는 Cell의 물리적인 입장에서 본다면 SLC는 약 5~10년, MLC/TLC는 약 1~2년 동안의 기간을 저장할 수 있습니다(SW 등의 보완 조치로 저장 기간을 더욱 길게 확장 할 수 있음). 그래서 낸드플래시는 전원이 꺼져도 창고라는 공간에 저장된 데이터가 존재하므로 ‘비휘발성 메모리’라고 합니다. 반면 디램은 전원이 ON일 때 일정한 주기로 새로운 refresh 전원을 계속적으로 인가해주면 데이터는 저장창고에 남게 됩니다. 하지만 전원을 OFF하면 어떤 경우든 데이터는 소멸하므로 ‘휘발성 메모리’라고 부릅니다.

디바이스 구조 비교

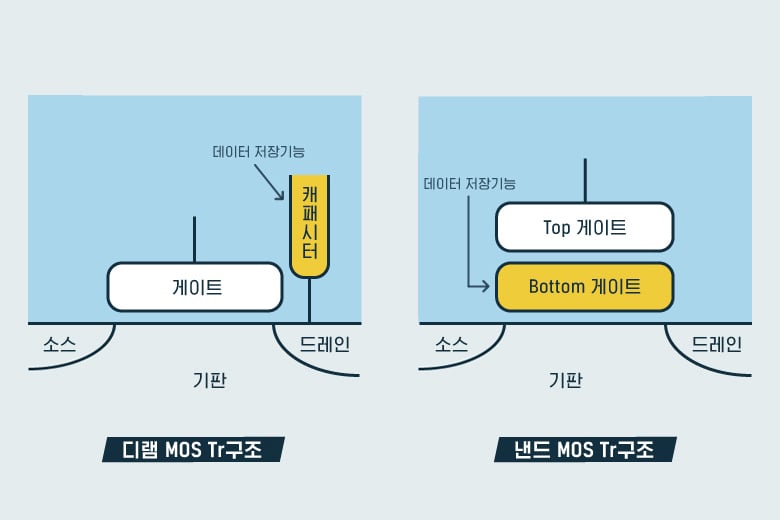

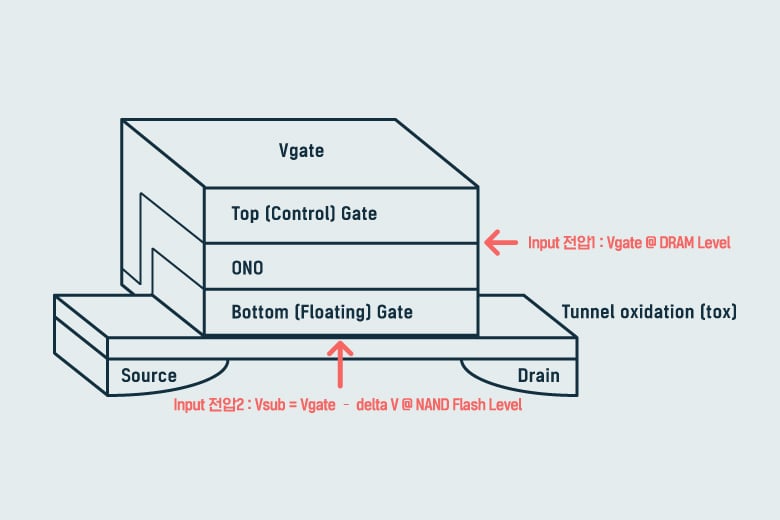

▲ 디램과 낸드 디바이스 구조 비교

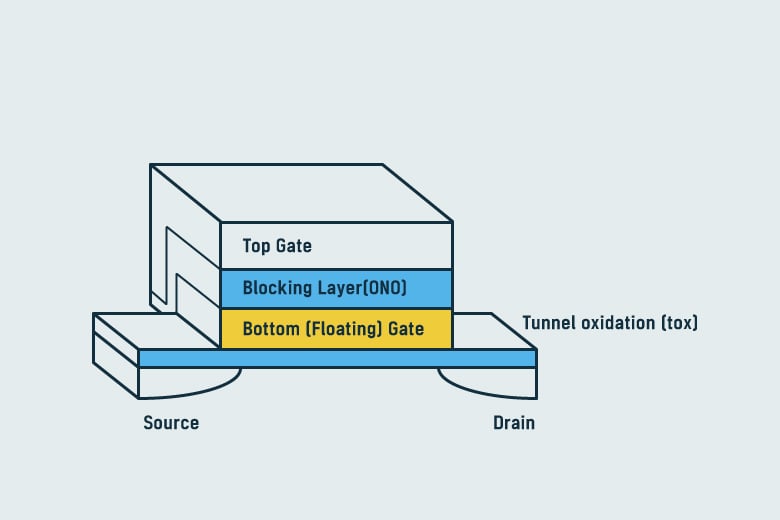

낸드플래시가 구조적으로 디램과 구분되는 가장 큰 차이점은 게이트(Gate)가 2개라는 점입니다. MOS형 트랜지스터(Tr)는 소스(Source), 드레인(Drain), 게이트 총 3개의 단자로 구성되는데요. 그중 게이트 단자가 1개이면 디램, 2개이면 낸드플래시가 됩니다. 낸드플래시의 추가된 게이트 단자는 부유 게이트, 즉 플로팅 게이트(Floating Gate)라고 부릅니다. 이는 모든 입체 영역으로부터 절연층으로 분리된 상태로 마치 섬처럼 부유하고 있다고 하여 붙여진 이름입니다. 이로 인해 낸드플래시는 읽고 쓰고 저장하는 모든 동작에서 디램과 에스램(SRAM)보다 독특한 특성을 지니게 되었는데요. 그 중 가장 핵심적인 특징이 데이터를 원하는 일정기간 저장할 수 있는 비휘발성 데이터의 저장 능력입니다. 그런데 이러한 장점을 갖기 위해서는 동작 속도 등 디바이스 특성에서 희생을 감수하고, 또 재질과 공정방법 및 설계 등에서 보완해야 한다는 단점이 다수 있습니다.

따라서 구조적으로 볼 때, 디램은 스위칭 역할을 하는 Tr 1개와 Tr 밖에 별도로 데이터를 저장하는 캐패시터 1개를 둡니다(DRAM Cell=MOS Tr 1개+Capacitor 1개). 반면 낸드플래시는 스위칭 역할을 하는 트랜지스터 속에 데이터 저장 기능을 갖는 플로팅 게이트를 같이 내포하고 있어서 MOS Tr 1개만으로 메모리로서 해야 할 여러 가지 기능을 수행합니다(NAND Cell=MOS Tr 1개). 따라서 낸드플래시는 Top gate(상판게이트 혹은 Control 게이트)와 Bottom gate(하판 게이트 혹은 부유 게이트)가 있으므로 총 2개의 게이트를 갖게 되는 셈입니다.

저장 용량(Density) 비교

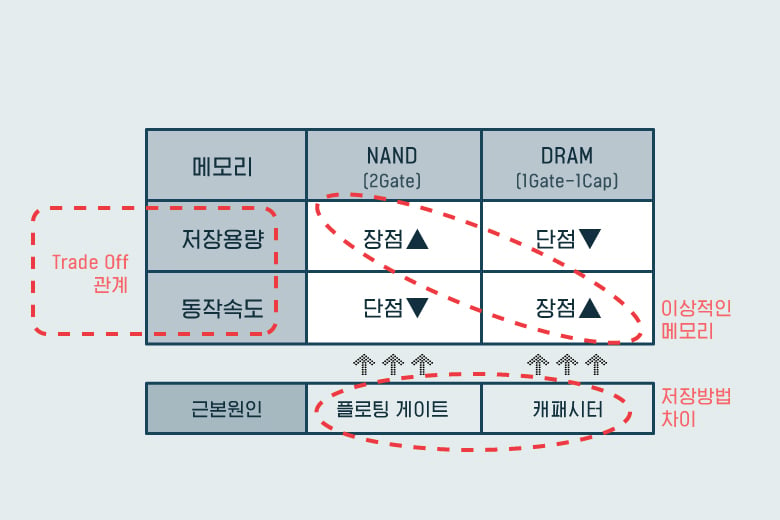

▲ 디램과 낸드 플래시의 전반적인 비교

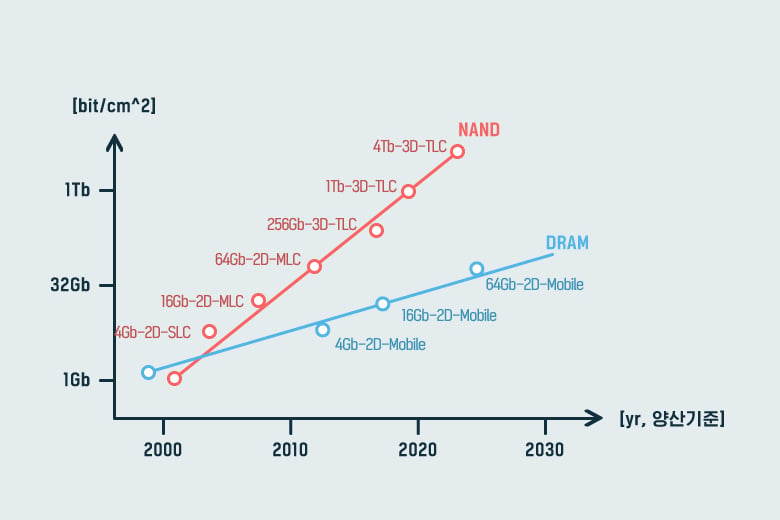

집적도 측면에서는 낸드플래시가 메모리 디바이스 중 가장 유리합니다. 표면적을 차지하는 디바이스의 점유 면적을 상대적으로 가장 작게 할 수 있기 때문이지요. 낸드플래시의 집적도가 가장 높은 근본적인 이유는 구조에서 찾아볼 수 있는데요. 디램은 저장기능을 하는 캐패시터를 Tr 밖에 별도로 두어야 하므로 2D 표면적을 많이 점유합니다. 따라서 낸드플래시의 집적도는 항상 디램보다 앞서 나가며, 3D를 적용하고부터는 집적도 차이는 더욱 커질 것으로 예측됩니다. 동일 메모리의 저장용량으로 들여다볼 때, 2D 낸드플래시의 구조적인 차이가 디램과 10년 차이를 만들어 내었고, 3D 낸드플래시는 동일 집적도 비교 시 디램과는 15년 차이를 나타낼 것으로 예측됩니다.

낸드플래시의 단점

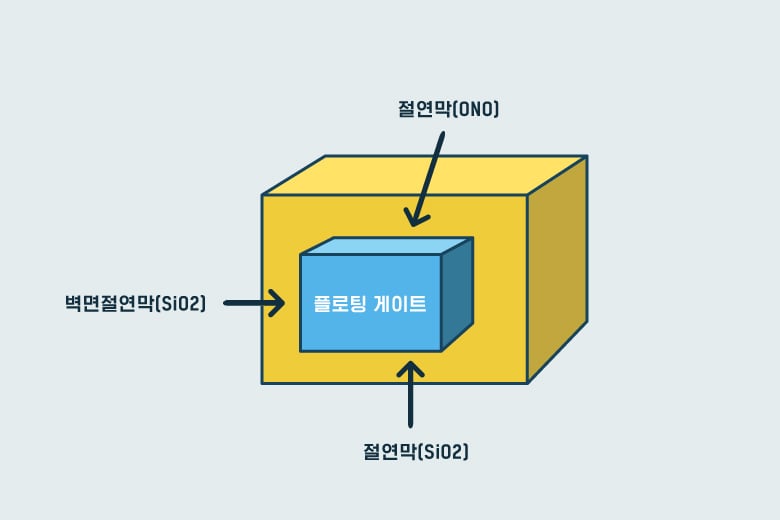

▲ 부유게이트floating gate와 절연막 @ NAND Flash

낸드플래시는 메모리 디바이스 중에 속도가 가장 느립니다. 이는 디램과는 달리 추가적으로 존재하는 게이트인 플로팅 게이트가 있기 때문인데요. 낸드플래시의 핵심 구조물인 플로팅 게이트는 낸드플래시에 전자들을 저장하는 역할을 합니다. 플로팅 게이트를 6개 면으로 둘러싸고 있는 절연막들은 그 안에 저장된 전자들이 쉽게 탈출하지 못하도록 막는 역할을 하지요. 그래서 플로팅 게이트의 위로는 Blocking Layer(ONO : 3개 절연층)가 있고, 아래로는 Tunneling Oxide(전자들이 건너가는 절연막, SiO2), 옆으로는 Sidewall Oxide(측벽절연막, SiO2)가 막아서고 있습니다. 이런 구조에서 동작 전압이 인가되면 플로팅 게이트와 아래위의 절연막들이 합작하여 여러 가지 캐패시턴스 성분을 만들고, 이런 성분들이 결국 낸드플래시의 동작 속도를 느리게 하는 요인으로 작용하게 됩니다.

게이트 전압의 비교

▲ 채널에 직접적인 영향을 끼치는 게이트 전압의 비교 @ DRAM vs NAND

MOS Tr에 인가되는 게이트 단자에 디램과 낸드플래시에 동일한 크기로 전압이 인가될 경우, 채널 형성에 기여하는 실질적인 전압은 낸드플래시에 더 작게 인가됩니다. 이는 플로팅 게이트와 플로팅 게이트 아래위로 존재하는 2개 캐패시터의 영향 때문이지요. Word line으로 게이트 전압 Vgate가 인가 시에 디램은 기판층(Substrate) 혹은 채널에 직접적인 영향(Vgate=Vsub)을 끼칩니다. ▶<채널이 만들어 내는 반도체 동작특성, 드레인 전류의 변화> 편 참고 하지만 낸드플래시에서는 기판 방향으로 직렬로 늘어서 있는 캐패시터 2개(Cono+Ctox)를 통과하기 때문에 기판에 최종적으로 인가되는 전압 Vsub(Input 전압2 @NAND)은 초창기 게이트 전압 Vgate(Input 전압1 @DRAM)에 비해 작아집니다.

드레인 전류의 비교

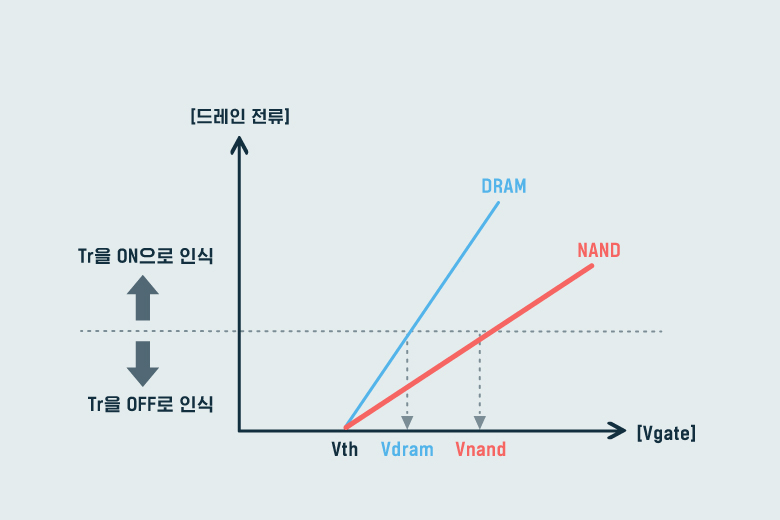

▲ 디램과 낸드의 드레인-전류 비교

트랜지스터의 스위칭 작용인 ON/OFF를 결정 짓는 드레인 전류를 비교해보겠습니다. 게이트에 전압이 동일하게 인가되는 조건(Vgate)이라면, 디램보다는 낸드플래시의 드레인 전류가 적게 흐르고 전류 Drive 능력이 떨어지므로 동작 속도도 느려집니다. 일반적으로 게이트 입력 전압을 증가시킬 경우 기판 내의 전자가 이동할 채널의 체적이 커지므로 드레인 전류(소스 단자에서 드레인단자로 이동하는 전자의 흐름)는 게이트 전압에 비례하여 증가합니다. 또, 소스와 드레인 단자 사이를 연결하는 채널도 빠르게 형성되므로 동작 속도 역시 빨라지지요.

그런데 디램과 낸드플래시의 드레인 전류 증가율을 비교해보면, 입력 게이트 전압이 높아질수록 디램에 비해 낸드 전류의 상승률이 낮습니다. 이는 실질적으로 기판의 채널에 영향을 주는 게이트 전압인 Vsub의 증가률이 낮기 때문이지요. 결국 MOS Tr이 ON/OFF 구실을 제대로 하기 위하여는 일정 전류량 이상이 확보되어야 하는데요. 따라서 낸드플래시의 경우, 드레인 전류량을 디램과 동일하게 하려면 인가하는 게이트 전압을 디램보다 높여야 하겠지요(단, 디램과 낸드의 다른 모든 조건이 동일하다는 가정).

메모리에서 저장할 데이터의 크기와 처리 속도는 디바이스 소자 특성, 설계 구조 및 공정 진행 방법에 따라서 좌우되며, 상호 간에 Trade off 관계에 있습니다. 이번 장에서는 이러한 세 가지 요소에 대해 디램과 낸드플래시의 기능과 구조 및 저장용량 등을 비교하며 대략적으로 알아보았습니다. 다음 장에서는 디램과 낸드플래시의 차이에 대한 근본적인 원인에 대하여 좀 더 구체적으로 알아보고, 제품을 쉽게 이해할 수 있도록 디바이스-구조-기능-공정을 연결하여 살펴보도록 하겠습니다.

※ 본 칼럼은 반도체/ICT에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.