뉴스룸에서는 대구경북과학기술원 교수 7명과 함께 반도체 기본 모듈과 반도체 적용 사례, 메모리, 인터페이스 회로 등을 주제로 총 7편의 칼럼을 연재하고 있다.

이번 2편에서는 전기전자컴퓨터공학부 김가인 교수로부터 입출력(I/O) 인터페이스 회로의 특징, 회로 작동 방식, 현대 시스템에서 사용되는 다양한 회로 구조와 다양한 응용 분야에 대해 알아볼 것이다.

※ 대구경북과학기술원(DGIST, Daegu Gyeongbuk Institute of Science and Technology): 반도체 융합기술, 뇌공학, 마이크로레이저 등 다양한 첨단 과학 기술을 연구하고 있다. 특히 반도체 분야에서는 전문적인 연구개발(R&D)과 함께 캠퍼스 내 반도체 제조 시설을 구축 운영하고 있다.

아침 출근 시간대에 꽉 막힌 도로를 상상해보라. 도로 위에 차들이 빈틈없이 들어차 차를 돌릴 수도 없고, 그저 가만히 기다리며 목적지까지 천천히 운전해야 하는 상황, 아마 모든 직장인에게는 악몽일 것이다.

마찬가지로 프로세서 간에 움직이는 데이터의 양은 많은데 이동할 수 있는 채널(금속 선로)은 적을 경우, 데이터도 교통 체증에 빠지게 된다. 특히 인공지능, 슈퍼컴퓨터 기술의 발전으로 데이터가 폭증하는 요즘 데이터를 정확하고 빠르게 전송할 수 있는 효율적인 입출력(I/O) 인터페이스* 회로의 필요성은 점점 커지고 있다.

* 입출력(I/O) 인터페이스: 컴퓨터와 다른 기기(주변 장치) 간의 데이터 송수신을 위한 연결 고리. 즉, 컴퓨터와 키보드, 마우스, 프린터, USB 메모리 등과 같은 다양한 외부 기기를 연결하여 데이터를 주고받는 것을 돕는 것이다.

데이터 전송에서 입출력 인터페이스 회로가 중요한 이유

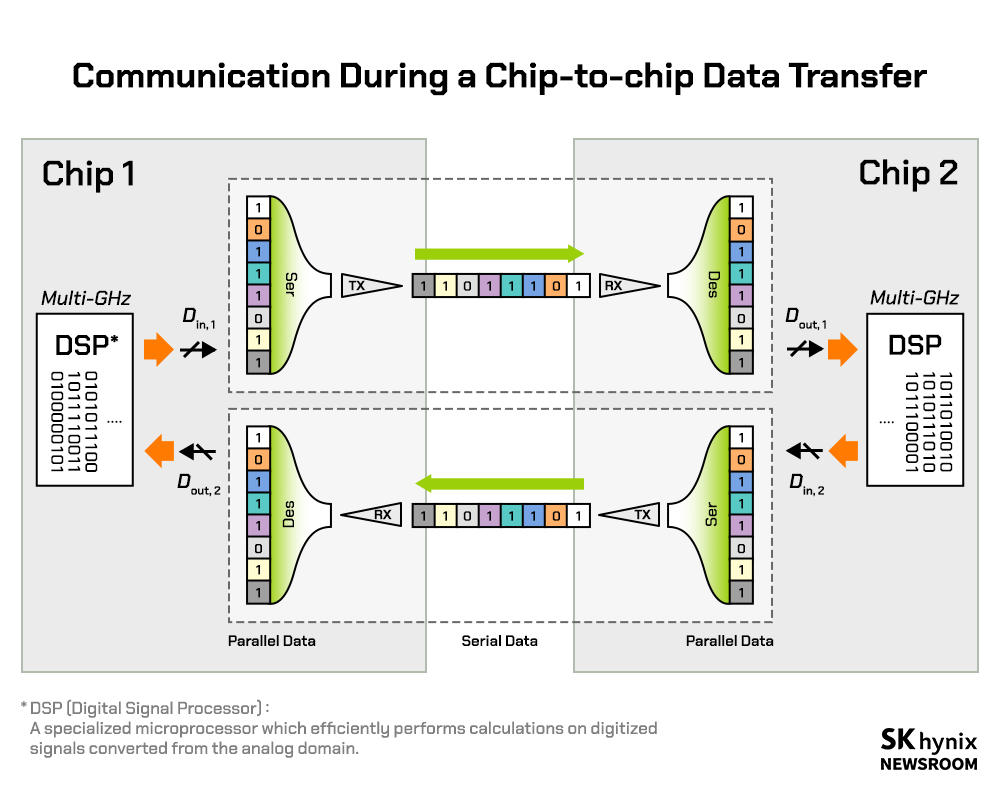

▲ 그림 1. 송신기(Transmitter, TX)와 수신기(Receiver, RX)를 통해 칩 간 통신이 이뤄지는 모습

그림 1은 두 개의 반도체 칩과 입출력 인터페이스 회로(점선 상자)를 표현한 것이다. 하나의 프로세서에서 처리된 디지털 데이터가 다른 프로세서로 전송되기 위해서는 전기 신호가 칩의 접합부인 패드에서 채널(금속 선로)을 통해 다른 칩의 패드로 전달되어야 한다. 칩 간에 데이터가 이동할 때는 병렬 데이터(Parallel Data)가 직렬 데이터(Serial Data)로 변환되며, 데이터가 다른 칩에 도착한 후에는 직렬 데이터가 다시 병렬 데이터로 변환된다.

이때 채널(금속 선로)을 통해 다른 칩으로 이동하는 전기 신호는 이진수인 ‘0’과 ‘1’의 의미를 가지는 전압 정보이다. ‘0’과 ‘1’이라 하니 단순해 보일 수 있지만, 이 ‘0’과 ‘1’이라는 신호를 전달하기 위해서는 상당히 복잡한 단계를 거쳐야 한다.

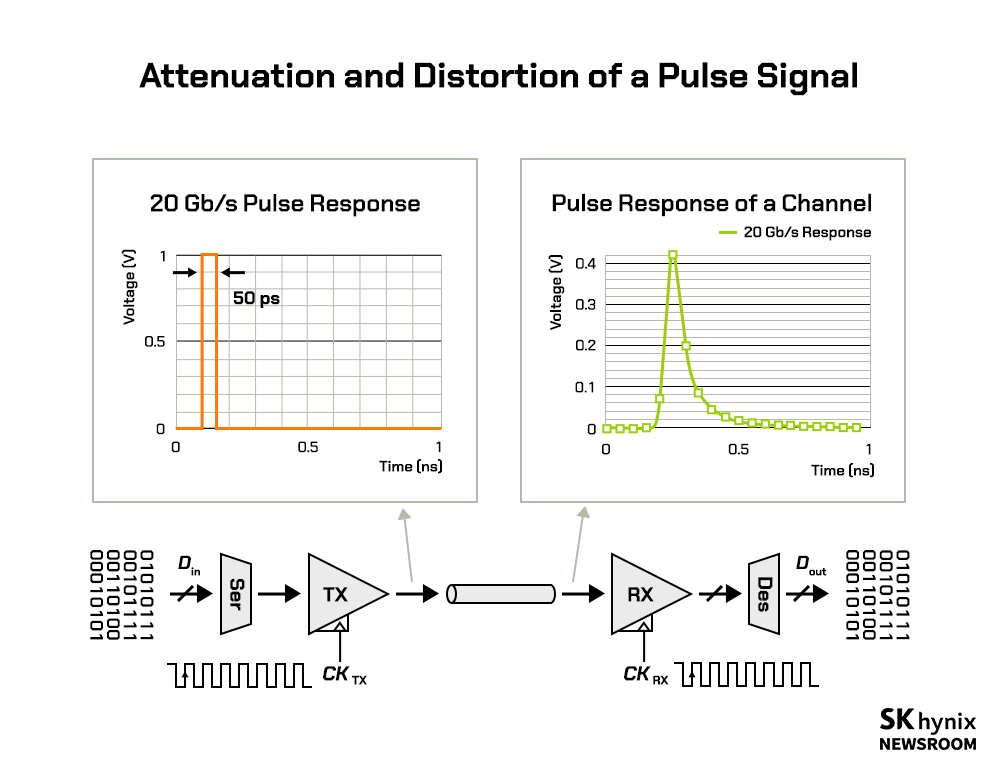

▲ 그림 2. 전형적인 펄스(Single-bit) 신호가 유선 채널(금속 선로)을 통과한 후 감쇄와 왜곡이 발생한 모습

그 이유는 칩 간 고속 통신 속도를 보장하기 위해 프로세서가 단위 시간당 처리해야 하는 이진수(Binary) 데이터의 양이 매우 많기 때문이다. 반면 칩의 내부와 외부에서 통로 역할을 하는 패드의 수는 한정되어 있다. 이는 위에 언급한 교통 체증 비유처럼 차량은 많은 데 비해 고속도로의 차선 수는 제한적인 것과 유사한 상황인 것이다.

데이터 전송 채널(금속 선로) 개수는 정해져 있는데 반해 데이터를 막힘 없이 전달하기 위해서는 개별 채널(금속 선로)에서 데이터 전송 속도를 최대로 높여야 한다. 그런데 채널(금속 선로)의 크기가 한정된 상황에서 데이터 전송 속도를 높일수록, 데이터가 다른 칩의 수신기에 도착했을 때 도달한 데이터의 ‘0’과 ‘1’의 신호를 구분하기 어려워진다. 그 이유는 그림 2와 같이 신호가 채널(금속 선로)을 통과하면서 수신기(Receiver)에 도달하면 신호가 감쇄하고 왜곡되기 때문이다. 일반적으로 채널(금속 선로)의 길이가 길어질수록 신호의 손실이 크고 왜곡의 정도가 심해진다. 이러한 문제 때문에 필요한 것이 신호의 감쇄와 왜곡을 감안하여 원래의 신호에 최대한 가깝게 복원해주는 회로인 이퀄라이저(Equalizer)다.

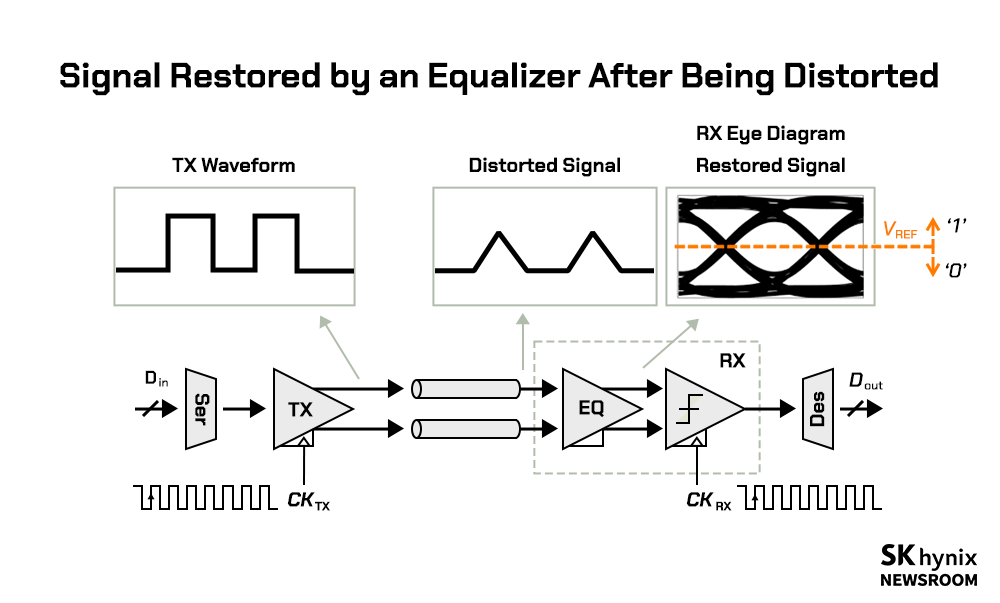

▲ 그림 3. 수신기의 이퀄라이저(EQ)는 유선 채널(금속 선로)에서 손상된 신호를 복원해 ‘0’과 ‘1’을 명확히 구분해 보여준다.

이퀄라이저는 데이터를 와이어로 보내는 송신기(Transmitter, TX)와, 채널(금속 선로)로부터 데이터를 받는 수신기(Receiver, RX)로 분류된다. 이퀄라이저를 통해 원래의 신호에 가깝게 복원된 신호는 그림 3과 같이 ‘0’과 ‘1’의 명확한 구분이 생긴다.

그런데 송신기가 보낸 ‘0’을 수신기가 ‘1’로 읽거나 반대로 ‘1’을 ‘0’으로 읽는 오류가 생길 수 있는데, 이를 ‘비트 에러(Bit Error)’라고 부른다. 이러한 비트 에러가 발생할 확률(비트 에러율)을 줄이고 주어진 채널(금속 선로)과 채널(금속 선로) 당 데이터 전송 속도에서 비트 에러율을 최대한 낮추기 위해 이퀄라이저가 사용된다. 이러한 역할을 하는 송신기와 수신기를 합쳐 직렬 링크(Serial Link)*, 유선 송수신기(Wireline Transceiver)* 혹은 SerDes(SerDes: Serializer-Deserializer)*라고 부른다. 그리고 이런 직렬 링크들이 모여 형성되는 것이 바로 입출력(I/O) 인터페이스다.

* 직렬 링크(Serial Link): 데이터 비트를 직렬로 하나씩 전송하는 통신 방식. 직렬로 데이터를 하나씩 전송하는 것이 병렬로 여러 개를 동시에 전송하는 것보다 데이터 전송 경로를 단순화할 수 있어 높은 전송 속도와 신뢰성을 보장한다.

* 유선 송수신기(Wireline Transceiver): 디지털 신호를 전기 신호로 변환하고 전송하는 송수신기. 고속 데이터 전송이 필요한 대규모 데이터 센터나 클라우드 서비스 등에서 사용된다.

* SerDes(Serializer/Deserializer, 직렬/병렬 변환기): 고속 데이터 전송을 위해 사용되는 데이터의 직렬/병렬 변환을 수행하는 장치. 직렬 데이터는 병렬 데이터로, 병렬 데이터는 직렬 데이터로 변환한다.

입출력 인터페이스는 어떻게 발전해왔나

다중 칩 모듈(Multi-Chip Module)*에서는 칩 간(Chip-to-chip) 연결이 더욱 중요한 역할을 하게 되면서, 입출력(I/O) 인터페이스의 진화는 더욱 중요해지고 있다.

* 다중 칩 모듈(Multi-Chip Module, MCM): 여러 개의 반도체 칩을 한 패키지 안에 결합하여 하나의 시스템으로 구성하는 기술. 여러 개의 소형 칩을 사용하여 단일 칩보다 더 높은 성능, 전력 소모량과 칩 크기 감소 등 다양한 장점이 있다.

▲ 그림 4. 고성능 프로세서의 설계 비교 – 단일 다이(칩)를 특징으로 하는 과거의 설계(a)와 소형 멀티 다이(칩)를 사용한 최신 설계(b)

최근 몇 년간 고성능 프로세서는 다중 칩 모듈 형태로 설계되고 있는 추세다. 그 이유는 첫째, 과거에 프로세서 제조업체들은 프로세서의 성능 향상을 위해 다이(Die)* 크기가 커지다 보니 공정에서의 수율이 감소하고 수익성이 떨어지게 되었다. 그 후로 제조업체들은 수율과 수익성을 지키면서도 성능이 향상된 프로세서를 만들기 위해 단일 다이(칩)에 코어 개수와 SRAM* 용량을 늘리는 기존 방식에서 적당한(소형) 크기의 여러 개 다이(칩)로 구성된 모듈이 마치 하나의 프로세서로 작동하게 만드는 방식을 채택했다.

* 다이(Die): 웨이퍼 위에 최종적으로 형성된 반도체 칩. 다이란 반도체로 작동하는 최소 제품 단위이며, 주로 패키징 되기 전의 칩 상태를 일컫는다.

* SRAM(Static Random Access Memory): 반도체의 기억장치로, 데이터를 보관할 수 있는 공간이다. 반도체 다이(칩) 내에 SRAM 셀을 집적할 수 있으며, 하나의 반도체 다이(칩) 내에 여러 개의 SRAM 셀을 넣을 수 있다.

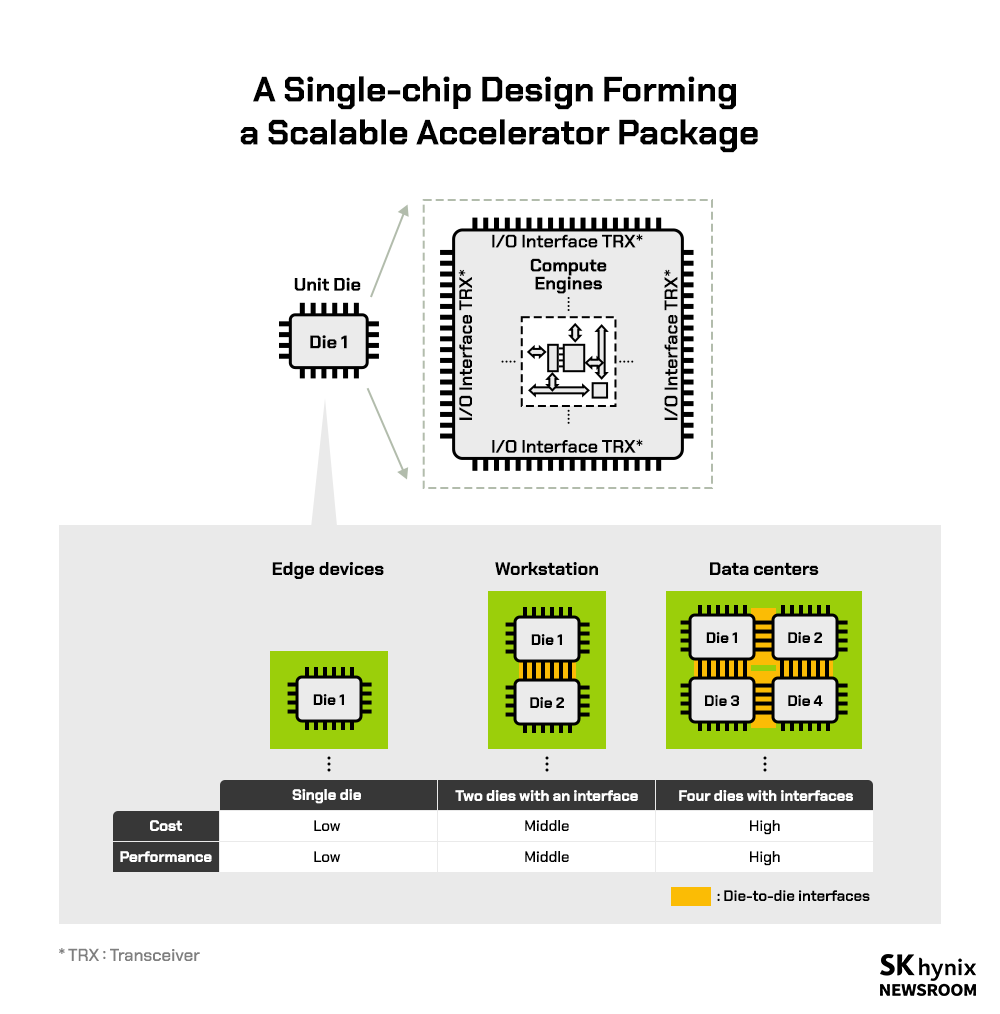

▲ 그림 5. 단일 칩 설계로 확장 가능한 가속기 패키지를 형성한 예시. 다이(칩) 사이에 지연시간이 매우 짧아야 하며, 저전력 및 고성능 광대역 인터페이스가 필요하다.

둘째, 확장성(Scalability)이다. 그림 5는 단일 칩으로 설계된 여러 연산 가속기 예시를 보여준다. 병렬 계산에서 목표로 하는 성능 수준에 따라 한 개의 패키지 안에 포함된 여러 개의 다이(칩)로 시스템을 구성할 수 있다. 이렇게 하면 제조업체는 다양한 성능의 연산 가속기 제품군을 갖추기 위해 다양한 칩 설계를 따로 구현할 필요가 없어 설계 비용과 개발 리스크를 줄일 수 있다.

이때 다중 칩 모듈의 확장성을 보장하기 위해 필수적인 것이 입출력 인터페이스다. 인터페이스에 병목현상이 발생하면, 칩 간의 소통이 느려지기 때문에 개별 다이(칩)의 성능이 뛰어나더라도 다중 칩 시스템 구성 시에는 성능 향상을 보장할 수 없다. 그래서 다중 칩 모듈 인터페이스는 채널(금속 선로)의 길이가 매우 짧고 신호의 손실이 적기 때문에 고성능 이퀄라이저의 필요성이 낮다. 하지만 다중 칩 모듈에서는 여러 개의 다이(칩)가 자연스럽게 연결되어 마치 하나의 다이(칩)처럼 유기적으로 작동해야 하기 때문에 인터페이스를 통한 데이터 송수신 지연시간(Latency)이 매우 짧아야 한다. 또 오류 수정 코드(Error Correction Code, ECC)*를 사용하지 않더라도 비트 에러율은 0에 근접해야 한다. 따라서 최근 다중 칩 모듈에서 다이(칩) 간 인터페이스는 최소한의 이퀄라이저를 사용하고 지연시간을 최소화하고, 다이 에지(Die Edge)의 단위 길이가 초당 전송할 수 있는 총 데이터 양을 증가시키는 데 중점을 두고 기술이 발전하고 있다.

* 오류 수정 코드(Error Correction Code, ECC): 비트 오류율을 줄이기 위해 데이터 전송 오류를 감지하고 정정하는 알고리즘

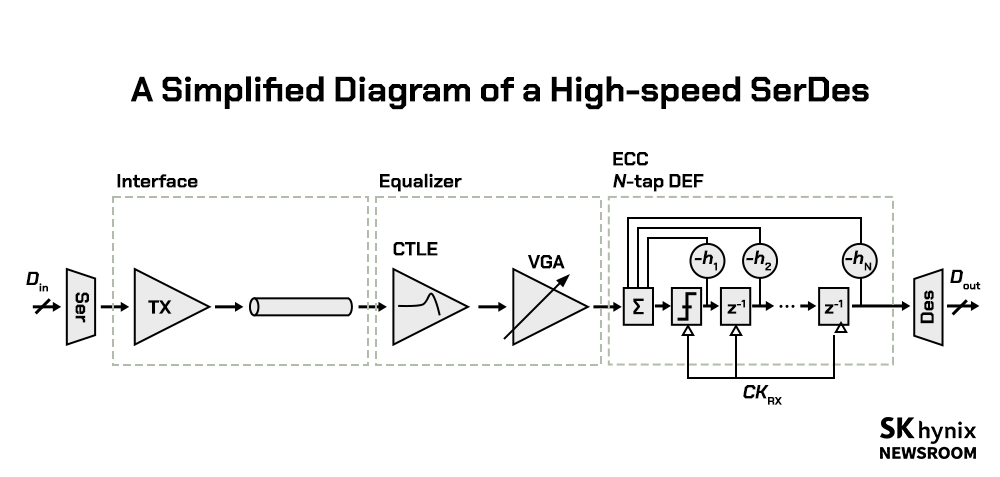

▲ 그림 6. 수신기에 CTLE, VGA 및 DFE가 포함된 고속 SerDes*를 단순화한 도표

* SerDes(Serializer/Deserializer, 직렬/병렬 변환기): 고속 데이터 전송을 위해 사용되는 데이터의 직렬/병렬 변환을 수행하는 장치. 직렬 데이터는 병렬 데이터로, 병렬 데이터는 직렬 데이터로 변환한다.

PCle* SerDes는 프로세서의 연결성 확장에 사용되며 고성능 프로세서에 사용되는 인터페이스 구조의 또 다른 예다. 인터페이스 관점에서 PCIe SerDes가 그림 4(b)와 같은 멀티 다이(칩) 설계와 다른 점은 신호 감쇄가 더 크다는 것이다. PCIe SerDes에서 패키지 범프, PCB 와이어 및 커넥터를 포함한 유선 채널(금속 선로)에서 발생하는 신호 손실은 최대 40dB이다. 신호 손실이 크므로 통신 지연시간을 줄이는 것보다 이퀄라이저가 신호를 복구하는 것이 더 중요해진다. 이 때 수신기가 최대 40dB에 이르는 높은 신호 손실을 복구해야 하므로 의사 결정 피드백 이퀄라이저(DFE)*외에 연속 시간 선형 이퀄라이저(CTLE)*, 그리고 가변 이득 증폭기(VGA)* 이퀄라이저를 활용한다.

* PCIe(Peripheral Component Interconnect Express): 컴퓨터 시스템에서 주변 기기를 연결하는 데 사용되는 고속 직렬 데이터 통신 인터페이스

* 의사결정 피드백 이퀄라이저(Decision Feedback Equalizer, DFE): 전력 소모가 많고 회로 설계가 복잡하지만 신호 복구 능력이 좋은 이퀄라이저

* 연속 시간 선형 이퀄라이저(Continuous Time Linear Equalizer, CTLE): 입력 신호의 고주파 성분을 부스팅 하여 채널(금속 선로) 왜곡을 보상하는 아날로그 이퀄라이저

* 가변 이득 증폭기(Variable Gain Amplifier, VGA): 입력 신호의 크기를 증폭하여 출력하는 회로로, 제어 코드에 따라 이득(Gain)을 가변적으로 조절할 수 있다.

PCIe는 범용성이 뛰어나며, 고속통신을 지원하는 인터페이스 중에서는 서버용 CEI*/이더넷 SerDes다음으로 빠른 고속 통신속도를 지원하며 범용성이 높다. 따라서 최근에는 PCIe PHY*를 통해 작동하는 CXL* 프로토콜 기반의 확장 카드를 사용한 컴퓨팅 시스템의 성능을 개선하기 위한 다양한 연구가 진행되고 있다. 상용화된 제품의 예를 들면 서버용 CXL 기반 DRAM 확장 솔루션이 있다. SK하이닉스의 경우 2022년 8월 PCIe에 기반을 둔 DDR5 DRAM 기반 CXL 메모리 샘플을 개발했다. [관련 기사] CXL 인터페이스는 CPU, GPU, 가속기 및 메모리의 이용 효율성 향상에 도움을 준다.

* CEI(Common Electrical I/O): 직렬 링크 인터페이스의 일종으로, 주로 고속 데이터 전송에 사용된다.

* PCle PHY(Physical Layer): PCIe의 물리적 레이어를 뜻함. 이는 PCIe 통신이 안정적으로 이뤄지도록 데이터 전송 속도와 신호 왜곡을 관리하는 하드웨어 측면의 레이어를 일컫는다.

* CXL(Compute Express Link): 고성능 컴퓨팅 시스템을 효율적으로 활용하기 위한 차세대 인터페이스. PCIe PHY를 기반으로 작동한다.

채널(금속 선로) 당 100Gb/s 이상 속도를 가진 초고속 SerDes의 경우, CTLE, VGA와 같은 아날로그 이퀄라이저뿐만 아니라 디지털 신호 처리기(DSP)* 같은 디지털 이퀄라이저를 사용해 많은 이퀄라이징 작업을 해내야 한다. 예를 들면, 데이터 센터의 CEI/이더넷 SerDes가 있으며, 많은 팹리스 회사가 최근 6세대 64GT/s PCIe SerDes 수신기에 디지털 신호 처리기를 활용하는 기술에 대한 지적 재산(IP)을 발표한 바 있다. 이때 디지털 신호 처리기를 사용하기 위한 필수적인 블럭*은 초고속 아날로그-디지털 변환기(ADC)*이다.

* 디지털 신호 처리기(Digital Signal Processor, DSP): 디지털 신호를 처리하는 특수 마이크로프로세서.

* 블럭(Block): 컴퓨터 하드웨어 설계에서 쓰이는 개념으로, 전자 회로에서 기능적으로 하나의 단위를 이루는 회로나 소자를 뜻한다. 블럭은 더 복잡한 기능을 수행하기 위해 서로 연결될 수 있으며, 이러한 블럭들의 조합으로 전체 시스템이 만들어진다.

* 아날로그-디지털 변환기(Analog-to-Digital Converter, ADC): 아날로그 신호를 표본화하여 디지털 신호로 변환하는 장치. 이를 통해 아날로그 신호를 디지털 신호로 변환한 후 디지털 신호 처리 장치에서 처리할 수 있다.

아날로그 이퀄라이저는 연속시간상에서 동작하는 반면, 디지털 신호 처리기는 기가헤르츠(GHz) 단위로 작동한다. 따라서 고속 아날로그-디지털 변환기(ADC)는 초당 수십 기가 샘플(GS/s)급으로 데이터를 샘플링하여 샘플링된 출력 데이터를 병렬화해야 한다. 병렬화된 데이터는 아날로그 이퀄라이저에 비해 지연시간이 길어지는데, 그 이유는 디지털 신호 처리기 내의 여러 디지털 신호 처리기 클럭* 주기를 통해 블럭 단위로 신호를 복구하기 때문이다. 수십 개의 고속 아날로그-디지털 변환기에서 병렬 데이터를 처리하는 디지털 신호 처리기는 현재까지도 동등한 성능의 아날로그 이퀄라이저 대비 전력 소비량이 더 크다. 그러나 아날로그 이퀄라이저로는 복원이 불가능한 수준의 신호 손실을 디지털 이퀄라이저와 아날로그 이퀄라이즈와의 조합으로는 복원이 가능하다. 따라서 아날로그-디지털 변환기와 디지털 신호 처리기 기반의 수신기는 최대 40dB의 손실로 채널(금속 선로)을 이퀄라이징할 수 있는 초고속, 장거리 인터페이스에 사용되는 사례가 점점 더 증가하고 있다.

* 클럭(Clock): 전자 기기에서 주기적으로 발생하는 진동 신호로, 전자 장치의 작동 속도를 조절한다. 예를 들어 CPU는 클럭의 신호에 맞춰 데이터를 처리하며, 클럭의 주파수가 높을수록 CPU의 처리 속도가 빨라진다.

입출력 인터페이스 디지털화의 미래

지금까지 고속 입출력 인터페이스의 기본 개념, 역할, 그리고 서로 다른 분야에 이용되는 송신기와 수신기의 구조 상 차이점을 살펴보았다. 요약하면 데이터 송수신 지연시간을 감소시키는 것이 채널(금속 선로)의 신호 손실을 보상하는 것이 더 중요한 어플리케이션의 경우, 상대적으로 저속의 아날로그 이퀄라이저만 사용하는 수신기를 선택해도 충분하다. 그러나 채널(금속 선로)의 신호 손실이 큰 초고속 인터페이스의 경우 아날로그 이퀄라이저를 사용하되 디지털 신호 처리기를 추가하여 신호 보상을 얻을 수 있는 구조의 수신기가 활용되고 있다.

지난 5년 동안 초고속 유선 송신기의 다양한 블록을 ‘디지털화’하는 설계 기술이 발전했다. 반도체 공정의 미세화가 아날로그 회로보다는 디지털 회로에 더 유리하기 때문에 이러한 추세는 가까운 미래에도 계속될 것으로 예상된다. 또한 DSP의 활용 범위가 확대되면서, 상대적으로 간단한 알고리즘이었던 이퀄라이저의 구조도 더욱 복잡하고 다양한 통신 알고리즘을 활용하게 될 것으로 예상된다.

※ 본 칼럼은 반도체에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.