반도체 Fab 공정의 첫 단계인 FEOL(Front End Of Line, 전공정)을 통해 반도체 소자 구조를 완성하면, 중간 단계인 MEOL(Mid End Of Line)을 거쳐 BEOL(Back End Of Line, 후공정)을 진행합니다. BEOL에서는 수평면으로 금속선 회로를 깔고, 수직 방향으로는 소자가 외부와 소통할 수 있도록 소자의 4개 단자와 연결하는 콘택트(Contact)와 비아홀(Via Hole)을 형성합니다. 소자와 소자, 소자와 외부를 잇는 이 같은 과정을 바로 ‘금속배선 공정’이라고 하지요.

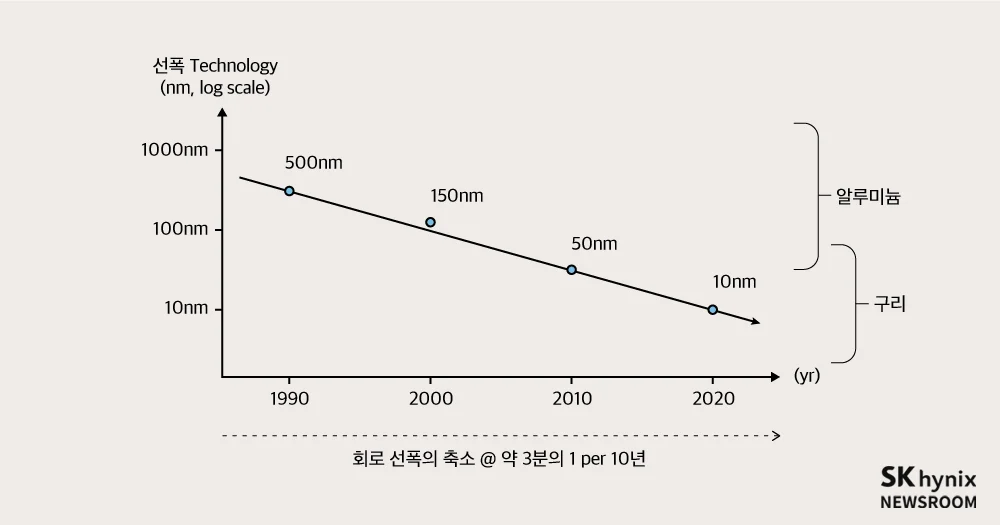

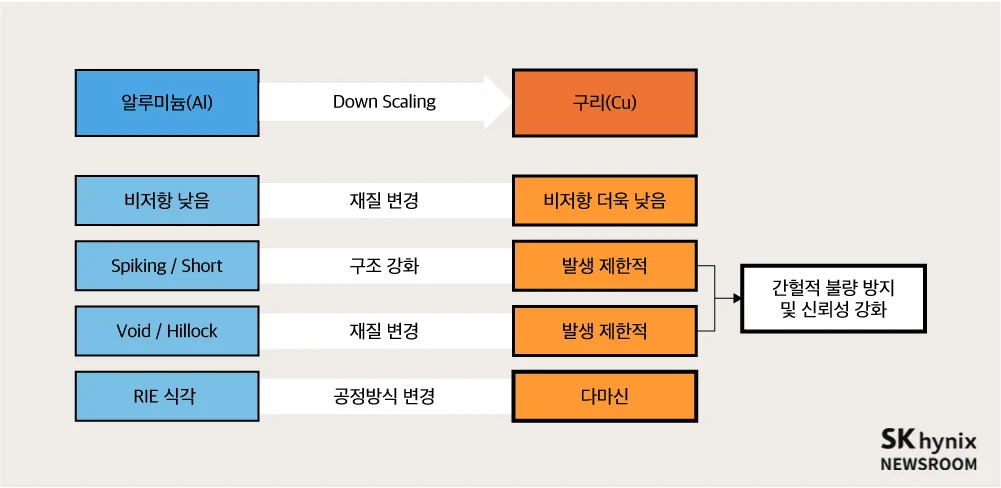

배선 물질은 소자의 구조가 고밀도로 발전하고 기능이 고속화됨에 따라, 알루미늄(Al)에서 구리(Cu)로 전환됐습니다. 현재 구리는 가장 보편적으로 널리 사용되는 배선 물질이지요. 구리는 내구성과 신뢰성 측면에서 알루미늄보다 우수하지만, 공정이 복잡해 원가가 높으며 새로운 공정 방식을 도입해야 한다는 부담이 있습니다. 그럼에도 불구하고 구리를 전해도금(Electroplating) 방식으로 채우는 다마신(Damascene) 공정이 새롭게 개발되면서 10nm(나노미터)의 선폭까지 구현이 가능해졌고, 이로써 구리 재질은 오래 사용해도 선폭이 유지될 수 있는 높은 신뢰성을 갖게 됐답니다.

1. 배선의 대표 재질, 알루미늄

반도체 금속배선에는 알루미늄(Al), 텅스텐(W), 티타늄(Ti), 구리(Cu) 등 다양한 재질이 사용될 수 있지만, 그중 많은 장점을 가진 알루미늄이 가장 오랫동안 사용되어 왔습니다. 텅스텐의 경우, 알루미늄으로는 채워 넣기 힘든 비아홀(Via Hole)에 주로 적용했지요. 낮은 비저항 성분을 갖는 알루미늄은 전자들이 비교적 쉽게 통과할 수 있는 재질입니다. 여기서 비저항이란, 일종의 저항 성분의 상수값을 의미합니다. 저항값은 단면적과 길이에 따라 달라지는 반면, 전기 비저항 성분은 재질마다 일정하지요. 따라서 비저항치로 재질 내에서 전자들이 이동하는 전도도를 절대치로 나타낼 수 있습니다.

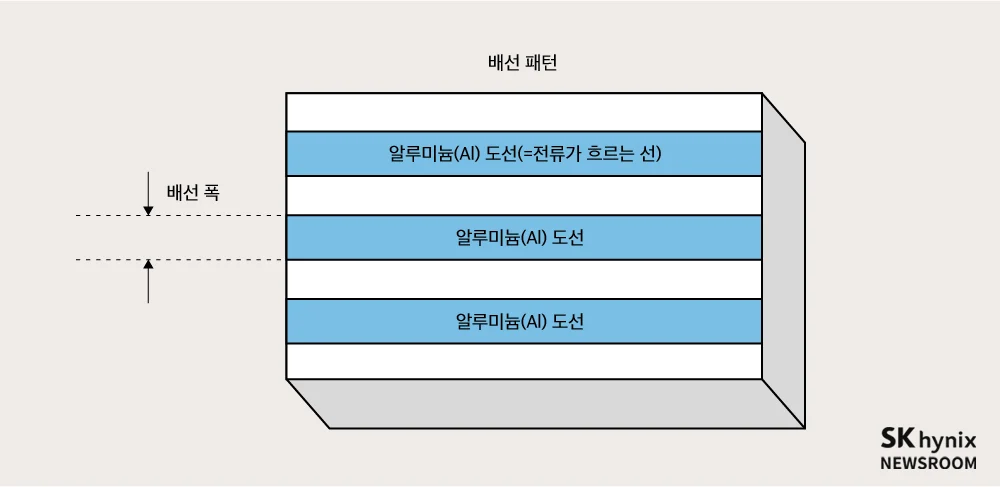

또한, 알루미늄은 식각(Etching)을 통해 이리저리 금속 패턴(Pattern)을 내기 쉬운 재질입니다. 이때 패턴이란 금속막을 PVD(Physical Vapor Deposition, 물리 기상 증착)의 스퍼터링(Sputtering) 방식 혹은 증발 방식 등으로 증착(Deposition)한 뒤, 포토(Photo)공정과 식각공정을 통해 불필요한 영역을 제거해 드러나는 금속선을 뜻합니다.

2. 알루미늄의 단점

금속선은 어떠한 경우든 최소한의 일정 폭이 유지돼야만 도선으로서 제 역할을 할 수 있습니다. 장마로 도로가 유실되면 차가 지나갈 수 없듯이 말이지요. 그러나 Tech.가 발전하면서 금속선의 선폭이 좁아짐에 따라, 알루미늄을 사용한 금속선은 선이 끊기거나 전류를 제대로 전달하지 못하는 등의 치명적인 문제가 자주 발생하게 됩니다.

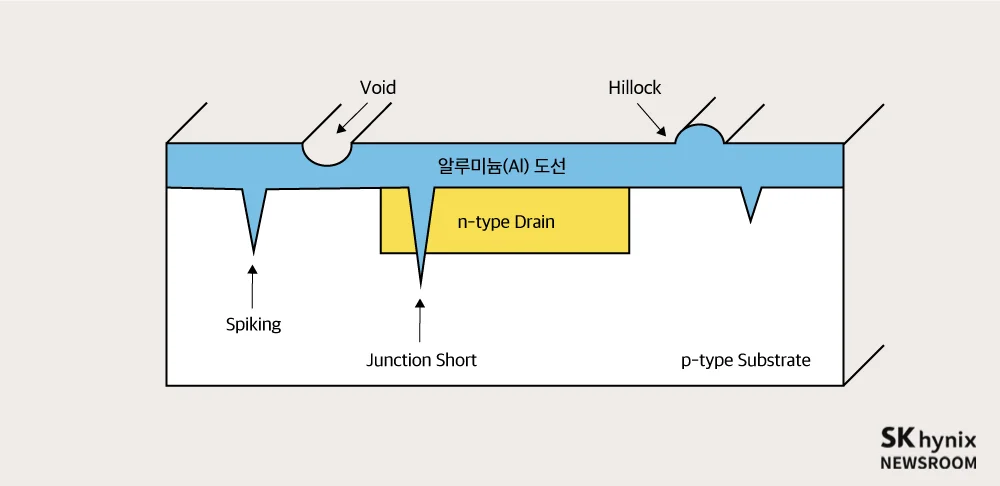

그중 하나로 전자들이 알루미늄 입자와 충돌할 때 알루미늄 입자들이 전자들이 흐르는 방향으로 조금씩 제자리를 이탈하는 현상인 일렉트로마이그레이션(EM: Electromigration)이 있습니다. 이렇게 알루미늄 입자들의 이동량이 많아질 경우, 특정 부분에 입자들이 부족해 공동(Void)이 발생하거나 반대로 입자들이 너무 많아 경계면에 힐럭(Hillock, 돌출)이 생기기도 하지요. 또한 알루미늄은 연한 재질이므로, 양옆에서 압력(응력)이 가해지면 산맥이 불쑥 솟아오르듯 표면에 힐럭이 발생하기도 합니다.

알루미늄이 높은 온도에서 실리콘 위에 증착될 경우, 두 재질이 상호 확산되며 섞이게 돼 경계면이 파괴되는 스파이킹(Spiking) 및 정션 쇼트(Junction Short) 현상이 발생합니다. 특히 실리콘 표면에 크랙(Crack)이나 공동 등이 발생하면, 여기에 알루미늄이 쉽게 파고들게 되지요. 마치 틈새로 물이 스며들 듯 말입니다. 이러한 현상을 방지하기 위해 실리콘과 알루미늄의 경계면에 금속 성질인 베리어(Barrier, 장애물)를 증착합니다. 혹은 알루미늄 재질에 2wt%(weight %) 미만으로 소량의 실리콘을 섞어 넣어 확산 현상을 줄이지요. 그러나 이 또한 다른 전기적인 부작용을 발생시키므로 근본적인 해결책이 될 수는 없답니다.

3. 구리의 등장

금속선의 선폭이 점점 줄어듦(Down Scaling)에 따라, 50nm 이하의 High Tech.에서는 더 이상 알루미늄을 사용하기 어려워집니다. 또한, 2000년대 초 IBM이 반도체 회로 내에서 알루미늄 대신 구리로 배선을 실현한 시기와 10년 정도 중첩되는 기간을 거치면서 구리-다마신(Damascene)이 정착하게 됩니다.

구리는 알루미늄보다 약 30% 정도 낮은 전기 비저항 성질을 갖고 있어 전도도가 높기 때문에, 알루미늄보다 더 작은 선폭을 구현할 수 있습니다. 비저항이 낮으므로 알루미늄보다 신호를 더욱 빠르게 통과시켜 유리하지요. 전력 소모도 낮아 소자에서 발생하는 열도 줄일 수 있습니다. 더 중요한 요소는 알루미늄의 단점이었던 전자 충돌에 의해 구리 입자가 움직이는 EM의 발생 확률이 급격히 줄어들게 되어, 공동이나 힐럭 등의 발생을 줄일 수 있다는 것입니다. 이로써 배선이 끊어지는 간헐적 불량을 방지할 수 있었으며, 내구성과 신뢰성도 한층 더 우수해진 것이지요.

4. 구리, 문제와 해결책

금속선으로 사용하기에 최적의 물질인 듯하지만, 사실 구리는 배선으로 모양을 내기가 매우 어렵다는 치명적인 단점을 안고 있습니다. 배선 패턴을 형성하려면 구리 재질을 RIE(Reactive Ion Etching, 반응성 이온 식각) 방식으로 깎아내야 하는데, 이 과정이 매우 어렵습니다. 구리를 식각하려면 식각 시 발생하는 화합물이 가스 형태로 배출돼야 하는데, 구리 화합물은 휘발되지 않기 때문입니다. 따라서 나중에 다마신 방식이 완료된 후에도, 불필요한 구리를 제거하기 위해 식각이 아닌 CMP(Chemical Mechanical Polishing, 화학적 기계적 연마) 방식으로 연마(Polishing)해야 합니다. 또한, 구리는 실리콘뿐 아니라 SiO2(이산화규소) 속으로도 확산될 수 있어 알루미늄보다 더욱 치명적인 스파이킹(Spiking) 현상과 정션 쇼트(Junction Short)를 발생시킵니다.

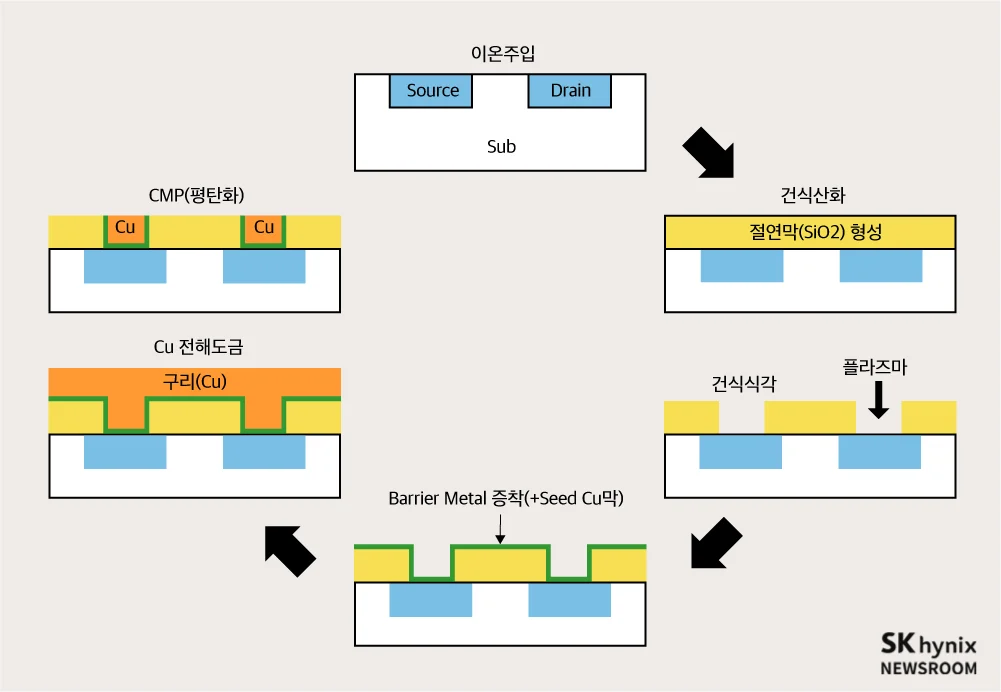

이같은 구리의 문제점을 해결하기 위해서는, 먼저 구리의 확산을 막기 위한 베리어를 설치합니다. 이는 알루미늄인 경우와 유사하게 실리콘/SiO2와 구리 사이에 추가적인 베리어를 형성하는 방법입니다. 또한, 구리막이 식각되지 않는 문제는 다마신이라는 상감 기법을 적용해 해결합니다. 다마신이란 미리 만들어 놓은 틀 속에 용융된 금속 액체를 주입해 넣듯, 전해도금(Electroplating)으로 구리를 채워 넣는 방식을 말합니다.

5. 다마신(상감) 방식

구리로 패턴을 채워 넣을 때는, 전해도금 방식 외 다른 증착 방식을 적용할 수도 있습니다. 예를 들어 빈 공간에 채워 넣는 방식으로 PVD나 ALD(Atomic layer deposition, 원자층 증착) 등이 있지요. 그러나 PVD는 주로 스퍼터링 방식이나 증착 방식을 적용하는데, 이는 단차 피복(Step Coverage)이 매우 불량하게 형성돼 채우고자 하는 갭필(Gap Fill) 밑에 공동이 형성될 수 있어 피해야 할 방식입니다. 또 다른 방식으로 ALD 방식이 있지만, 증착 속도가 너무 느리다는 단점이 있지요. 게이트옥사이드(Gate Oxide)나 커패시터(Capacitor) 막을 형성할 때는 사용해야 하지만, 막질의 품질이 비교적 덜 중요한 금속막에 ALD를 적용하는 것은 불필요한 비용(Cost)을 발생시킵니다. 그 외에도 CVD가 있지만, 이 방식은 갭(Gap)을 완전히 채워도 심(Seam, 틈)이 남는다는 문제가 있습니다.

하지만 전해도금 방식은 이러한 결함(Defect)이 발생하지 않습니다. 이 역시 증착 방식의 일종이나, 전해도금 방식을 이용할 경우 촉매가 증착율을 높여 거의 완벽하게 빈 공간을 채울 수 있다는 이점이 있습니다.

※ 본 칼럼은 반도체/ICT에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.