반도체 디바이스의 강자인 CMOS는 1960년 개발된 이후 괄목할 만한 성장을 이루었습니다. 안정성, 활용도, 신뢰성 등 각종 지표적으로도 현존하는 물질 중 가장 적합하다고 판단되어 사용된 실리콘을 기반으로 개발된 CMOS는 현재의 반도체 르네상스 시대를 연 주역이 되었지요. 주로 IC 등 비메모리 영역에 적용되는 CMOSFET는 소비전력을 최소화할 수 있음은 물론, 면적당 디바이스의 개수를 나타내는 집적도를 크게 향상시킬 수 있습니다. 또한 bit당 가격을 기하급수적으로 떨어뜨려 공급자와 소비자 모두에게 긍정적으로 작용하고요. 집적도의 향상은 CMOS구조의 혁신과 제조 공정상의 최적화에 의한 결과로 볼 수 있는데요. 이번 장에서는 CMOS 일괄공정과 CMOS와 연관된 개발 및 공정 요소들에 대해 알아보도록 하겠습니다.

CMOS를 위한 기초공사

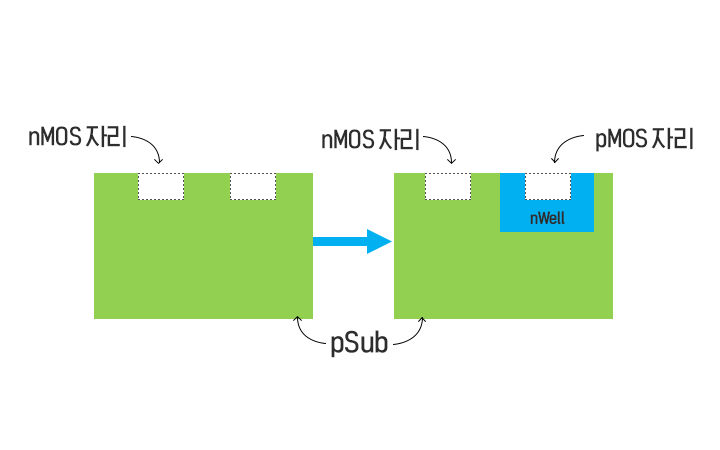

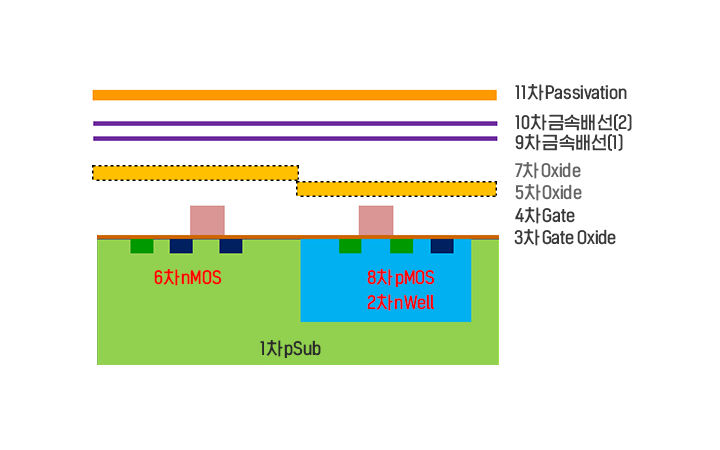

▲ CMOS의 기본 구조 : 기판상의 n_Well 형성 @ p_Type Wafer

DRAM 메모리는 트랜지스터(Transistor, Tr)를 통해서 커패시터(Capacitor)에 데이터를 저장합니다. 그리고, NAND 메모리는 아예 Tr속에 저장하지요. 이렇듯 모든 메모리, 비메모리 디바이스들은 Tr을 응용하여 동작하고 있는데요. 이런 Tr 2개를 포함하는 CMOS는 제조 공정 수를 줄이고, 단자 농도의 통일성을 기하기 위해 nMOS와 pMOS를 동시에 형성합니다. 그런데 Tr이 형성되기 위해서는 각각의 Tr특성에 맞는 기초공사가 필요한데요. pMOS는 반대 Type인 n_Well 위에 집을 짓고, nMOS를 세울 자리에도 nMOS의 반대 Type인 p_Well을 깔아야 합니다. 왜냐하면 케리어를 움직일 다리인 채널을 건설해야 하는데, 채널 Type이 Well Type과 서로 같으면 채널 자체가 형성되지 않기 때문이지요.

자, 그럼 먼저 연마(Polished) 웨이퍼든 혹은 에피(Epi) 웨이퍼든 p_Type Wafer로부터 시작해봅시다. nMOSFET는 Sub(p_Type 불순물 반도체)가 이미 마련되어 있으므로 Well을 별도로 형성하지 않고 Sub 위에 직접 건설합니다. 그런 후 pMOS를 세우기 위해서는 p_Type Sub위에 별도의 n_Well 하나를 추가하면 되겠네요. 이와 반대로 n_Type Wafer일 경우는 p_Well을 심습니다.

Well의 의미

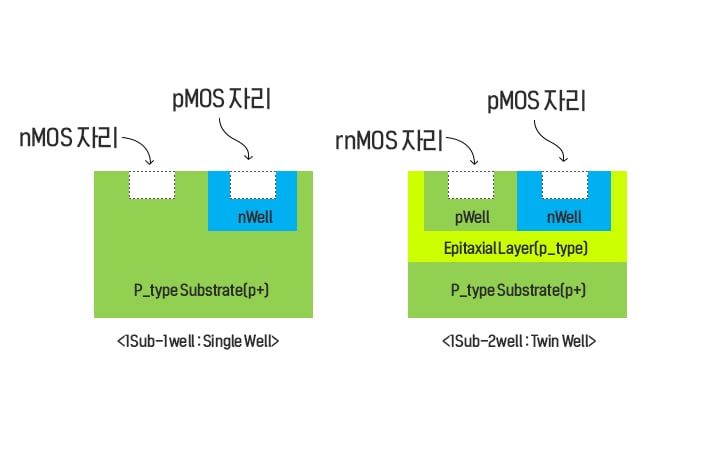

▲ Well의 다양화, 1Sub-1Well(Single Well) vs 1Sub-2Well(Twin Well)

기초공사는 곧 기판과 Well을 다지는 것을 의미합니다. Sub에 첫 번째 MOSFET를 형성한 후 두 번째 MOSFET를 형성하려면 기판 위에 또 다른 작은 영역의 기판을 형성해야 하는데, 이를 Well이라 부른답니다.

Old 방식으로는 1Sub-1Well(Single Well)로 2개의 Tr을 형성했지만, New 방식으로는 1Sub – 2Well(Twin Well)을 형성합니다. Twin Well은 Sub에 Well 2개를 형성 한 후에 각각의 Well이 1개씩 Tr을 지니도록 합니다. 이때 Well Type은 p/n_Type 각각 1개씩 구성해야 합니다. Twin Well에서 p_Sub위에 p_Well을 추가 하는 것은 nMOS의 주변 환경을 좀 더 이상적으로 만들기 위함이지요. 이렇게 했을 때, 단독 기판(연마웨이퍼)과 마찬가지로 에피텍셜(Epitaxial) Layer Type도 p_Type과 n_Type 모두 Single Well 혹은 Twin Well에 적용 할 수 있답니다.

트랜지스터의 단자 형성

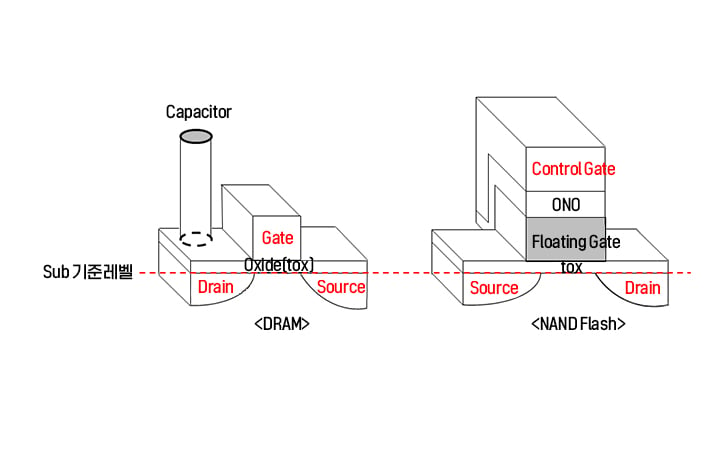

▲ MOS트랜지스터를 구성하는 3개 단자인 게이트와 소스/드레인의 구성 @ MOSFET 1개를 사용하는 메모리 소자의 예

Tr를 만드는 과정은 건물을 짓는 과정과 유사합니다. 건물은 땅 표면을 기준으로 위로 쌓기도 하고, 아래로 지하층을 만들기도 하는데요. MOSFET를 만들 때도 기준 레벨을 웨이퍼 표면 혹은 기판 표면으로 정한 다음, 게이트 단자는 기준 레벨 위로 쌓아 올리고 소스/드레인단자는 기준 레벨 밑으로 형성합니다. Tr는 3개 단자를 만드는데 먼저 증착을 통하여 게이트 단자를 만든 후, 아래로 향하는 소스/드레인은 임플란트&확산방식을 이용해 2개 단자를 동시에 만듭니다. MOSFET 하나만을 사용하는 메모리 제품인 DRAM에서 Tr 옆에 붙은 커패시터는 위로 쌓기도 하고 아래로 쌓기도 했는데, 지금은 모두 위로 쌓는답니다. NAND는 DRAM의 커패시터에 해당하는 플로팅게이트가 있는데, 이 또한 위로 쌓는 스텍 방식을 적용하지요.

CMOS 일괄공정

▲ CMOS 일괄공정 : 트랜지스터 Layer들의 형성 순서

일괄공정이라 함은 개별적 단위공정을 연결한 전체공정의 진행을 의미합니다. CMOS 층 쌓기는 Gate Oxide층 > 게이트 단자층 > 소스/드레인 단자층 > 금속선 배선층 순으로 진행됩니다. 웨이퍼가 준비되면 반도체 개발에서는 회로를 설계한 Layout을 CAD로 디자인하여 별도로 본을 뜨는데, 이를 마스크(Mask)라고 합니다. 마스크는 MOS를 위에서 보았을 때 각 층을 구성하는 평면 형태를 기하학적으로 모양을 낸 것입니다. 마스크는 각 층별로 약 2~5개를 사용합니다.

웨이퍼 준비에서부터 반도체를 패키징하여 양품을 골라내는 Final Test까지 약 250개 공정에서 500개 공정이 되지요. Sub공정까지 포함하면 이것의 두, 세 배가 된답니다. 이런 공정들을 거치는 기간은 약 6주에서 9주 정도 걸립니다. 즉, 반도체 칩은 웨이퍼 투입 후 약 2달 후에 완제품이 나온다고 보면 되겠습니다.

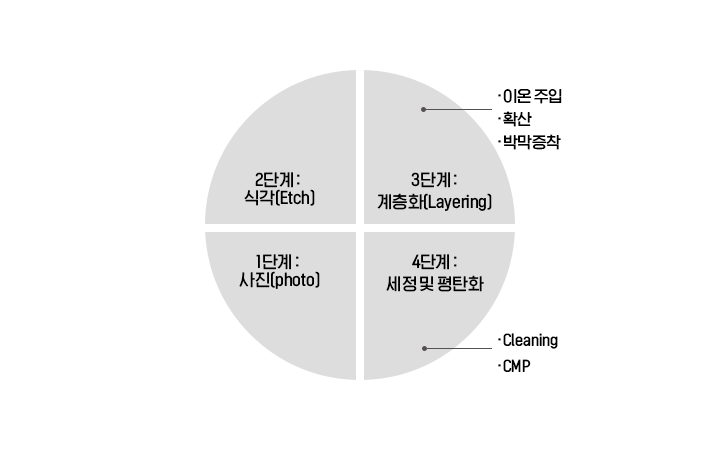

반도체 Fab공정의 4단계 Step (각 Layer별 Routine작업)

▲ Layer를 형성하기 위한 4단계 @ Fab Line

반도체 Fab공정에서 거의 대부분의 층(Layer)은 4단계 Step의 Routine작업을 되풀이 하여 형성되고 있습니다. 즉, 층 하나를 만들려면 1단계 : 사진(Photo) / 2단계 : 식각(Etch) / 3단계 계층화(Layer 형성) : 이온주입(Ion Implantation)/확산(Diffusion) 혹은 박막증착(Deposition) / 4단계 : 세정(Cleaning) 및 평탄화(CMP)라는 과정을 거쳐서 겨우 1개의 Layer가 형성됩니다(단, 단계별 순서는 서로 바뀔 수도 있고, 어떤 층은 일부 단계를 생략하기도 합니다). 물론 Well 같은 경우는 이온주입과 확산만을 이용하고요. 다른 Layer들도 반드시 4개 단계의 Routine공정을 순서대로 밟아야 한다는 것은 아닙니다. 또 더미(Dummy) Layer들도 있어서, 습식산화층(Oxidation Layer)같은 경우는 이온주입 시에 Masking 역할로 이용하고는 없애버리는 경우도 있지요. (그림4 이미지의 5차/7차 Oxide층과 같이).

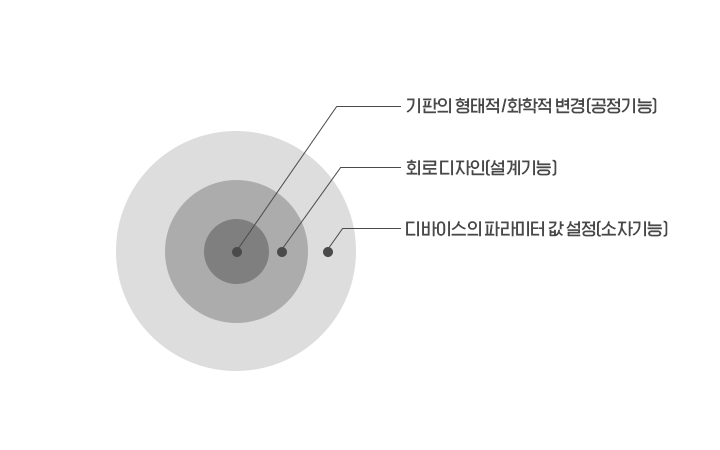

디바이스를 탄생시키기 위한 3가지 영역

▲ 디바이스(반도체 제품)를 완성하기 위한 3가지 기능 영역 : 소자, 설계, Fab공정

반도체 디바이스를 만들기 위해서는 기본적으로는 소자기능, 설계기능, 공정기능 등 3개 영역에서 기여를 해야 합니다. 소자기능에서는 제품을 일정한 범위 내에서 동작시키는 데 있어 모든 파라미터들의 적정한 값들이 사전에 설정되고 예측되어, 목표에 도달하지 못하면 다시 설계를 하거나 Fab공정상의 방법들이 재조정되어야 합니다. 이러한 소자 역할의 영역은 다른 기능에 비해 가장 넓다고 할 수 있습니다.

다음으로 설계기능에서는 소자기능에서 정해준 값들을 맞추기 위한 디바이스 회로의 Design이 나와야 하고 Design에 넣을 수 없을 때에는 소자기능에서 산출한 파라미터 값들이 재조정되어야 합니다. Fab공정에서는 디자인된 형태를 근거로 한 Mask를 확보하고, 소자에서 공급한 공정상의 세팅값(제품별 공정 Base Line 설정)들을 투입하여 기판의 형태적/화학적 변경을 진행합니다.

CMOS를 넘어서

반도체는 전세계적으로 볼 때, 획기적인 제품이나 급격한 특성의 개발 보다는 오랜 기간에 걸쳐 반도체 제조 공정이 구현 가능한 한계 내에서의 제품 업그레이드 수준 정도로 발전해왔습니다. 이러한 환경은 우리나라가 세계 제일의 메모리 반도체 경쟁력을 유지하는 데에도 유리했었지요. 그러나 집적도의 한계로 인해 앞으로는 지금까지 발전해온 2~30년의 단계를 한꺼번에 뛰어 넘어 반도체 개벽이 되는 수준으로 제품개발이 될 전망입니다. 그러므로 지금까지 누려온 CMOS의 전성기 역시 CMOS나이 약 60세~70세(2020년 ~ 2030년) 전후로 마감이 될 것으로 추정됩니다.

CMOS 이후의 미래 디바이스는 기반물질(실리콘)의 변경뿐만 아니라, 현재의 디바이스 특성 자체를 월등히 능가하는 발전을 거쳐야 할 것입니다. 더 나아가 전류를 발생시키는 이동자인 전자 대신 다른 매개체를 사용하는 것까지도 검토되고 있지요. 이는 디바이스의 동작속도를 빠르게 하기 위해 전자의 이동시간 조차도 줄여야 하기 때문입니다. 지금까지 반도체 분야가 실리콘을 기반으로 한 CMOS의 ‘천상천하유아독존’이었다면, 앞으로는 CMOS를 넘어선 ‘Beyond CMOS’라는 다양성이 증가한 제품다변화 체제로 점점 변해갈 것입니다. 반도체의 미래 기술방향은 기반물질, 디바이스특성, Fab 제조공법 등 설계에서 공정까지 디바이스와 관련된 모든 기술과 물질들이 획기적으로 도약하게 되는 새로운 양상으로 전개되어 갈 것입니다.

본장에서는 CMOS의 개별 공정에 들어가기에 앞서 CMOS라는 전체 그림을 이해하기 위해 전반적인 흐름을 살펴보았습니다. 다음 장부터는 조금 더 구체적으로 들어가서, 기판이 어떻게 형태적으로 혹은 화학적으로 변경이 되어 CMOS의 각 층을 형성하는지, Oxide에서부터 마지막 Passivation 공정까지 살펴보겠습니다. 또한, 각 Layer별 적용되는 4단계 Routine 공정에 대해서도 좀 더 깊이 있게 다뤄보도록 하겠습니다.

※ 본 칼럼은 반도체/ICT에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.