트랜지스터가 점유하는 체적을 지속적으로 축소시키기 위해서는 표면을 둘러싸고 있는 막의 두께를 줄여야 합니다. 반면, 박막 내 막질 조성과 트랜지스터의 전기적 특성은 갈수록 우수해져야 하죠. 막의 두께가 두꺼워야 신뢰성이 높아지고 공정을 진행하기도 수월합니다. 하지만 테크놀로지가 고도화되면서 커페시터나 게이트 옥사이드와 같이 대부분의 구조는 오히려 얇아져야 하는 모순이 발생하게 됩니다. 현재는 박막을 만들 때 CVD, PVD 등을 적용해야 하는데요. 이러한 기법들은 두께를 단단위 나노미터로 얇게 하는 데에 한계를 가집니다. 따라서 원자층을 한층 한층 쌓아 올려 막을 형성하는 ALD라는 적층방식을 사용합니다.

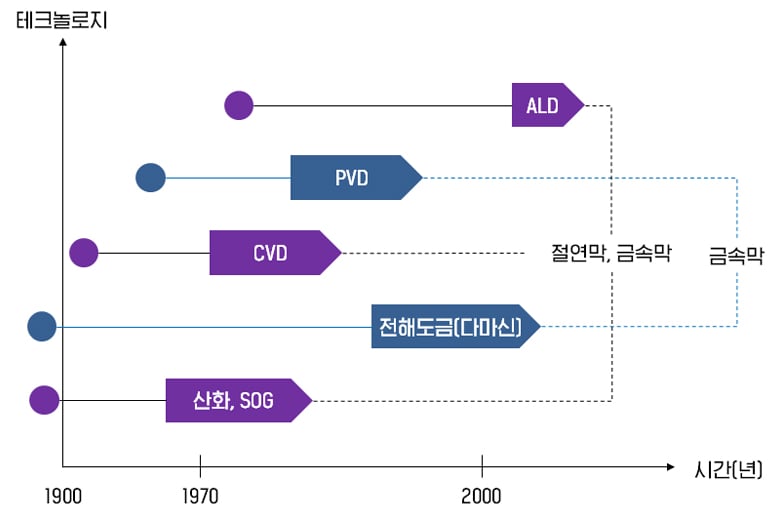

박막을 형성하는 방법들

▲ 박막을 형성하는 방법들의 기술발전 (반도체 특강, PVD편 참조)

반도체 박막을 만드는 방법으로는 대표적으로 두 가지가 있습니다. 화학적인 방법으로 절연막(혹은 금속막) 등을 형성하는 CVD(Chemical Vapor Deposition)와, 물리적인 방법으로 금속막을 이루게 하는 PVD(Physical Vapor Deposition)입니다. 그 밖에 산소를 이용한 산화막 및 막을 구성시킬 용액을 분사시킨 웨이퍼를 회전시켜 형성하는 SOG가 있고, 용액을 분해시켜 전기적으로 구리막을 형성하는 다마신방식 등이 있습니다.

최근에는 막의 얇은 두께와 신뢰성을 동시에 만족시킬 수 있는 ALD(Atomic Layer Deposition) 기법을 선호하는 추세입니다. ALD는 DRAM의 커패시터, 게이트 옥사이드, 메탈 베리어(Metal Barrier), 특히 NAND의 3D(Cell Stacking 구조)를 구성하는 가장 중요한 절연막/금속막에 쓰이고 있습니다.

반도체 테크놀로지 발전에 따른 박막 두께 이슈

반도체 테크놀로지가 고도화된다는 것은 회로의 금속 배선 폭이 줄었다는 것이고, 혹은 게이트 단자의 길이가 축소되었다는 의미입니다. 좀 더 구체적으로는 소스 단자와 드레인 단자 사이의 채널 길이가 점점 가까워진다는 뜻으로, 이런 현상을 집적도가 향상되었다고 합니다. 집적도 향상을 위해서는 공정에서 박막의 두께를 줄이거나, DRAM 커패시터의 종횡비(구조적으로 밑변 대비 높이에 대한 비율)를 높입니다. (물론 선 폭의 길이를 줄이는 것도 매우 중요하답니다) 이에 따라 증착이 중요해지는 만큼, 증착 장비의 변신이 최대의 화두가 되고 있습니다.

그런데 증착 기술의 커다란 변곡점은 테크놀로지 노드 90nm와 30nm에서 있었고, 앞으로 10nm 노드에서 또 한 번 요동칠 것입니다. 선폭이 30nm를 전후하여 증착법은 PVD, CVD에 이어 ALD로 변신을 하고 있으며, 특히 각 공법에서는 PECVD, PEALD 등 플라즈마의 접목이 활발해지고 있습니다. 엄밀하게는 ALD도 분자가 화학적 변화를 겪는다는 면에서 CVD의 파생기술로 볼 수 있는데, CVD에 비해 혁신적으로 발전된 기술입니다.

소스와 드레인의 간격이 30nm 이하일 때는 게이트 옥사이드나 DRAM 커페시터의 절연막 두께를 Xnm에서 1nm 이하(0.Xnm)로 줄여야 하는데요. 막 두께의 미세한 조정이 어려운 CVD나 PVD 방식은 고도화된 테크놀로지가 원하는 극한의 얇은 막을 만들어내기 힘듭니다. 박막 두께 조정의 측면에서 CVD나 PVD는 아날로그 방식이고, ALD는 디지털 방식이라고 보면 됩니다.

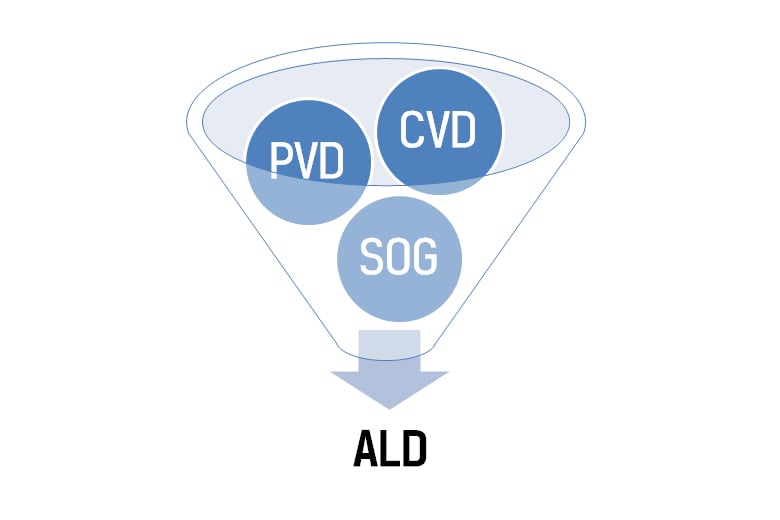

PVD, CVD의 단점을 극복한 ALD

▲ 박막공정을 만드는 방식의 변천

초창기 ALD는 ALE(atomic layer epitaxy)란 이름으로 1970년대에 핀란드에서 원자층을 성장시켜 적층하는 방식으로 개발되었습니다. ALE는 여기서 더 발전해 ALD라는 이름으로 반도체에 적용하기 시작했습니다. 원자층을 적층하는 방법은 말 그대로 원자 정도의 두께로 박막층을 한 층 한 층 형성해가는 자기 제한적 표면처리 공법입니다. 자기 제한적 표면처리란 웨이퍼 프로세싱 시에 아무리 소스를 많이 공급을 해도 원자층은 1개 층만 쌓인다는 것을 의미합니다. 1Cycle에 1개 층만 허용되므로 프로세스 회수를 계산하면 적층된 원자들의 층수를 알 수 있고, 원자들의 층수를 알면 막의 전체 두께가 쉽게 관리되겠죠.

그러므로 ALD는 얇은 층을 만드는 데 있어서, 앞으로 화학적 방식인 CVD나 물리적 방식인 PVD의 응용분야 중 많은 영역을 대체할 수 있는 획기적인 방식이라고 할 수 있습니다. ALD는 개발된 이후 산업분야에서 미미하게 적용되다가, 우리나라가 처음으로 반도체 분야에 응용하기 시작했는데요. 현재 세계적으로 ALD 기술은 SK하이닉스나 삼성이 가장 앞서 나가고 있답니다.

ALD 원리 : 증착(CVD/PVD)방식에서 흡착(ALD)으로

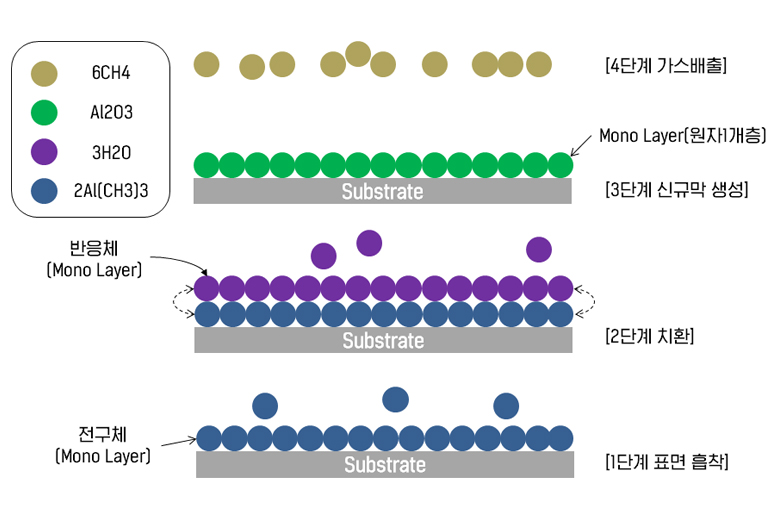

▲ ALD의 사이클(흡착/치환/생성/배출): 원자 1개층 생성 –> 사이클 반복(여러개 원자층 생성) : 막이 계획된 두께로 됨

ALD의 특징은 PVD와 같은 물리적 방식이 아닌, CVD와 유사한 화학적 방식이라는 것입니다. 하지만 PVD나 CVD는 여러 입력 소스를 동시에 공급해 여러 분자들이 표면에서 반응하면서 한꺼번에 막이 쌓이게 하는 방식인 반면, ALD는 입력 소스들을 순서에 맞추어 차례로 공급하여 단원자(혹은 분자) 층이 한 사이클 당 한 개 원자층(Mono Layer: ML)이 쌓이도록 합니다. 또한 쌓이는 방식은 엄밀히 말해 PVD나 CVD같은 증착이 아닌 흡착방식으로, 갭이나 트랜치의 벽면에도 잘 달라붙는 성질을 갖습니다. 1차 소스(전구체)를 프로세스 챔버에 넣으면 먼저 표면에 흡착이 일어나고, 뒤이어 다른 종류의 2차 소스(반응체)를 넣으면 1차 흡착된 물질과 화학적 치환이 일어나서 최종적으로 제3의 신규물질(막)이 생성됩니다. 결국 1개 층만 표면에 흡착되어 달라붙게 되는 것이죠.

ALD 적용의 예 : 게이트 옥사이드 유전막

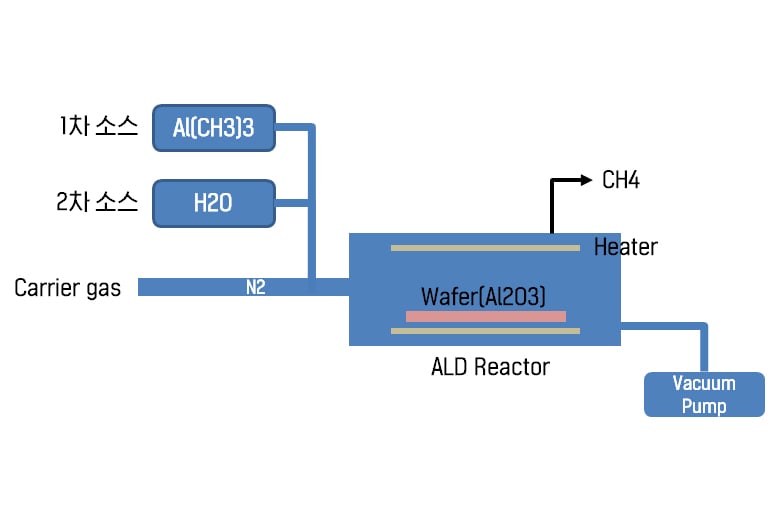

높은 유전체(High-k) 성질을 적용하는 게이트 옥사이드 유전막을 예로 들어봅시다. ALD 방식으로 층을 쌓기 위해 먼저 1차 소스로 Al(CH3)3를 공급합니다. 그러면 Al(CH3)3의 분자[2Al(CH3)3]가 Silicon 기판 위에 흡착되는데요. 이때 1차 소스로 Al(CH3)3를 계속 인가해도 CVD 처럼 두껍게 막이 형성되지 않고 오직 1개 층만 쌓이게 됩니다. 이를 자기제어반응 혹은 Self 제한적 표면포화반응(Self-limitation)이라고 합니다. (CVD나 PVD는 자기제어반응을 하지 못하여 소스를 계속 공급하면 비례하여 증착막 두께가 두꺼워집니다.) 그런 다음 2차 소스인 H2O 분자[3H2O]를 공급하면 H2O가 1차 소스인 Al(CH3)3와 화학적 치환반응을 하여 고체인 Al2O3만 남고, CH4(6개 분자) 가스는 배출됩니다. 이때 마찬가지로 2차 소스인 H2O를 계속 공급해도 1개 층만 흡착/치환반응이 일어납니다. 이렇게 1개 층만 쌓이게 하여 프로세싱 시간은 CVD에 비해 오래 걸리지만, 반복되는 횟수를 조절하면 두께를 정확하게 계산할 수 있습니다. ALD 사이클 반응을 화학기호로 나타내면, 2Al(CH3)3 + 3H2O = Al2O3 + 6CH4가 됩니다.

▲ ALD 장치 구조(유전막에 적용 시)

이렇듯 ALD는 자기제어반응으로 단단위nano 미터급 두께를 정밀하게 쌓을 수 있습니다. 또한, 층 내의 전체 격자가 정형적인 각을 이뤄 매우 질서정연하고 얇은 두께를 형성합니다. 1개 사이클에 원자층이 1개 층씩 쌓인다는 것은 두께 조절에는 획기적인 장점이지만, 속도가 느리다는 단점이 있어서 이에 대한 개선이 활발하게 이루어지고 있습니다. ALD에서는 두께 조절과 속도가 상반된 관계에 있는데요. 반도체에서는 이런 Trade off 관계가 곳곳에 널려있기 때문에 적정한 공정 레시피의 튜닝이 중요합니다. (반도체 공정 중, 여러 번 프로세싱을 반복해서 목표하는 두께를 이루는 공정에는 소스/드레인 단자를 형성하는 이온 임플란테이션 방식도 있습니다.)

단차피복성

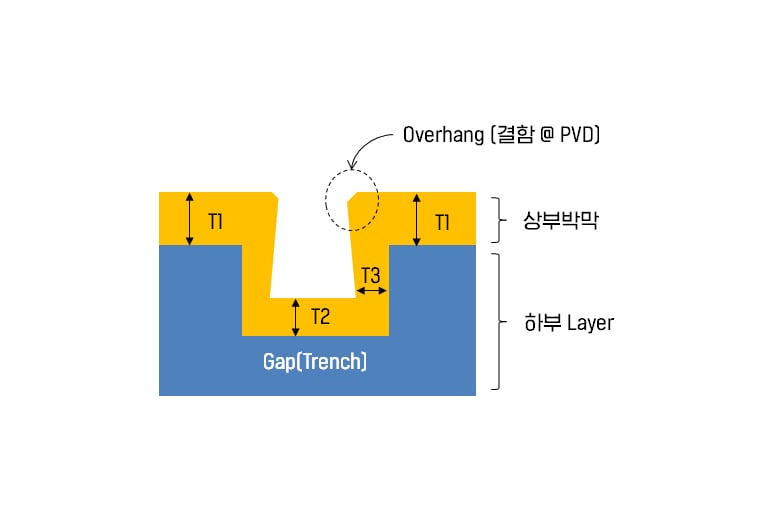

▲ PVD방식일 때, 단차의 스탭 커버리지 문제점 발생

단차피복성(Step Coverage)은 웨이퍼의 패턴 공정 진행 시 패턴의 밑면과 벽면 위치에 따라서 박막의 두께가 얼마나 서로 다르게 입혀지는지를 알아보는 지수입니다. 즉 Step Coverage는 뜻처럼, 패턴의 입체 모양이 갭(Gap)/트랜치(Trench) 형태의 계단식일 때 모든 방향 면에 대해 얼마나 동일한 두께로 균일하게 막이 형성되었는지 알아보는 척도이지요. 막이 형성될 땐 모든 면이 같은 두께로 형성되어야 가장 이상적이지만, 실제로는 단차의 어께 상부가 노출이 가장 크므로 가장 많이 쌓이게 됩니다. 그 다음이 갭의 하부이며, 가장 얇게 형성되는 곳이 갭의 벽면입니다. (금속원자가 표면에 눈처럼 쌓이는 PVD 방식을 적용할 때는 특히 갭 상부의 Edge 부분에 가장 두텁게 막이 형성되는데, 이는 불필요한 두께로써 Overhang이라 부르는 결함이지요.) 어느 정도 Step Coverage가 진행되었는지를 보기 위해 정상적인 막 두께(T1) 대비 갭 밑면(T2)과 옆면의 두께(T3)를 비율로 나타내며, 이를 각각 Bottom Step Coverage(T2/T1), Side Step Coverage(T3/T1)라 부른답니다.

CVD나 PVD는 계단층(단차Layer)을 만들 때 ALD에 비해 벽면의 피복이 잘 되지 않는다는 단점이 있습니다. 단차피복 결핍 시 DRAM의 경우 커페시터의 절연막을 만들 때 세로 막의 벽 두께가 얇아지면 커페시터 안에 가둬 놓은 전자들이 쉽게 빠져나가게 됩니다. 그러므로 전자들을 커페시터에 보충해주는 주기를 64ms (Refresh Time)보다 더 짧게 해야 합니다. (그러면 소모전력이 더욱 커지겠지요.)

ALD의 장단점

▲ ALD 방식의 장단점 (반도체 특강, PVD편 참조)

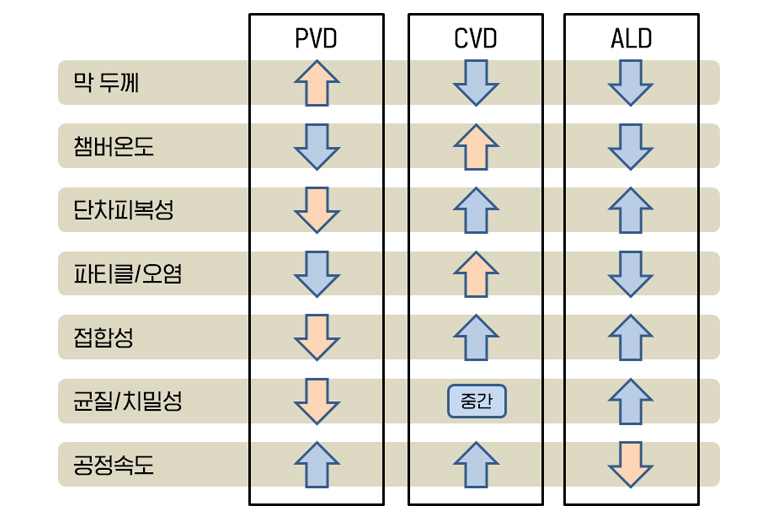

ALD는 흡착방식을 적용하므로 PVD의 약점인 단차피복성(Step Coverage)이 거의 없을 뿐 아니라, 막 내부에 형성되는 Void나 표면에 직경이 극히 작게 뚫리는 Pinhole도 거의 없다고 보아야 합니다. 막 전체가 균질한 격자 조성(정합증착능력)을 갖고, 나노 단단위의 일정한 두께로 코팅이 가능하다는 장점이 있기 때문에 ALD는 CVD나 PVD의 단점을 거의 보완한 코팅 방식입니다.

특히 ALD는 섭씨 400도 이하(200 ~ 400도)의 낮은 온도에서 공정 진행이 가능한데요. 그렇기 때문에 섭씨 600도 이상의 높은 온도에서 진행하여 다른 막에 영향을 끼치는 CVD의 단점을 보완할 수 있습니다. 그러나 ALD의 가장 치명적인 문제는 시간당 막을 성장시키는 공정 속도가 느리다는 것입니다. (원자층을 차례로 하나씩 쌓아 올리니 느린 것이 당연하겠지요.) 이외에도 ALD는 오히려 저온에서 진행하기 때문에 막의 물성이 떨어지는 문제가 있고, 1차 소스와 2차 소스들을 선택하는 데 한정적인 제한 등 여러 가지 자잘한 단점을 갖고 있습니다. 그러나 장점이 단점을 충분히 보상하고도 남기 때문에 ALD는 반도체뿐만 아니라 솔라셀, 각종 마이크로 디바이스 등에 활용도가 점점 높아지고 있습니다.

ALD 속도 개선

▲ ALD Loading 방식 (Semi-batch Type)

최근에는 ALD도 속도를 높일 수 있는 방식으로 플라즈마를 이용한 플라즈마 ALD, ‘PEALD’가 있습니다. 이는 ALD보다도 낮은 온도에서 반응성을 높일 수 있다는 장점이 있습니다. 20nm 이하의 테크놀로지나 새롭게 도입되는 구조인 3D 구조를 구현하는 데 적격이지요. 특히 종횡비(Aspect Ratio)가 높은 막인 커페시터나 게이트 스페이서 같은 경우는 더욱 PEALD가 필요합니다.

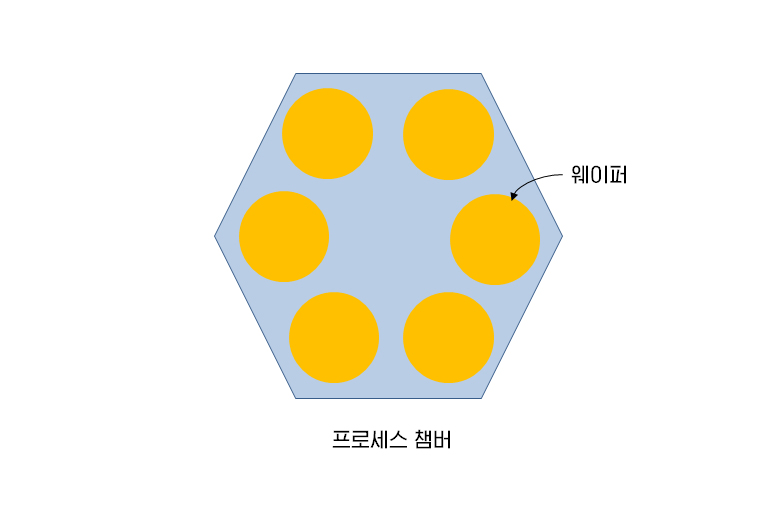

장치 Loading 방식에서도 Semi-batch Type이 개발되어 한 번에 1장씩 프로세싱 하던 것을 한꺼번에 여러 웨이퍼를 프로세싱 할 수 있게 되었습니다. ALD의 최대 단점인 공정 속도를 높이는 데 크게 기여하게 되었습니다.

90nm에서부터 이슈가 된 얇은 막의 실현은 CVD, PVD을 거쳐 ALD로 귀결되고 있습니다. 현재까지 가장 얇고, 막질의 품질이 높으며, 단차 구조를 극복할 수 있는 방안이기 때문입니다. 그중 플라즈마를 적용한 PEALD는 대부분의 박막 공정의 단점을 많이 보완한 ‘꿈의 박막기술’로 불리게 되었습니다.

※ 본 칼럼은 반도체/ICT에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.