스마트폰, 노트북, 전기차, 그리고 AI까지. 세상의 모든 디지털 기술은 반도체 ‘칩’ 위에 새겨진 정교한 회로 덕분에 작동한다. 하지만 이 칩은 매우 작고 얇으며, 무엇보다 외부 자극에 취약해 깨지기 쉽다. 이처럼 칩 위에 섬세하게 구현된 회로들을 외부 자극으로부터 보호하고 다른 부품들과 연결해 우리가 아는 ‘반도체’로서 기능하도록 하는 과정이 바로 ‘패키징(Packaging)’이다.

반도체 패키징은 단순히 부품을 조립하는 데 그치지 않고, 칩의 성능을 온전히 구현하고 사용 환경에서의 신뢰성을 확보하는 핵심적인 역할을 한다. SK하이닉스는 이러한 패키징의 기술적 중요성을 일찍부터 알아채, 지속적인 R&D 투자와 공정 혁신을 통해 패키징 경쟁력을 강화해 오고 있다. 이에 이번 콘텐츠에서는 반도체 패키징의 정의와 역할, 그리고 주요 공정까지 전반적인 내용을 자세히 살펴봤다.

패키징이란?

반도체 패키징은 쉽게 말해 ‘칩에 옷을 입히고, 길을 만들어주는 작업’으로, 외부 충격, 열, 습기 등에 매우 민감한 반도체 칩을 안정적으로 감싸 외부 자극으로부터 보호하고 전류가 흐를 수 있는 구조를 형성해 시스템과 전기적으로 연결하는 공정이다. 이러한 패키징 기술은 단순히 칩을 보호하는 개념에서 더 확장돼, 최근에는 반도체의 성능과 수명을 좌우하는 요소이자 제품의 완성도를 결정짓는 핵심 기술로 여겨지고 있다.

예를 들어 온라인 쇼핑몰에서 제품을 구매할 때 완충재로 안전하게 포장된 제품은 운송 과정에서 어떤 충격이 발생해도 손상 없이 배송되지만, 그냥 박스에 아무 조치 없이 제품만 넣어둔 제품은 작은 충격에도 손상되기 쉽다. 반도체 패키징 역시 마찬가지로, 칩의 구조나 기능이 같더라도 어떻게 포장하고 연결하는지에 따라 성능과 수명에 큰 차이가 발생할 수 있다.

패키징의 역할과 중요성

기존 반도체 기술은 회로 선폭을 줄여 ‘더 작고 빠른 칩’을 만드는 데 집중해 왔다. 그러나 단일 칩의 크기를 작게 만드는 것은 기술적 한계에 가까워져, 이제는 단일 칩 안에 모든 기능을 담는 방식보다 여러 개의 칩을 효율적으로 연결하는 방식이 새로운 기술적 방향성으로 떠오르고 있다.

이러한 변화의 중심에 패키징 기술이 있다. 대표적으로 HBM(High Bandwidth Memory)*, 칩렛(Chiplet)* 구조, 2.5D/3D 패키징 등 첨단 기술들은 칩과 칩 사이를 어떻게 연결하는지에 따라 그 성능이 천차만별이다. 패키징은 단순히 보호막을 만드는 데서 더 나아가, 전력을 효율화하고 신호 전달 체계를 최적화하거나 열을 분산하는 등 복합적인 성능 요소까지 아우르는 고난도 기술로 진화하고 있다. 다시 말해 패키징이 반도체 제품의 경쟁력을 좌우하는 핵심 요소로 부상하고 있다는 뜻이다.

* HBM: HBM(High Brandwidth Memory)은 여러 개의 DRAM 칩을 수직으로 쌓고, 그 사이를 관통하는 미세한 연결 구조(TSV, Through-Silicon Via)를 통해 데이터를 빠르게 주고받을 수 있도록 만든 초고속·고대역폭 메모리

* 칩렛(Chiplet): 하나의 큰 반도체 칩을 여러 개의 작은 칩(칩렛)으로 나누어 각각 기능별로 설계·제조한 뒤, 이를 패키징 단계에서 하나로 연결해 작동시키는 모듈형 반도체 설계 방식

패키징 공정, 어떻게 이뤄질까?

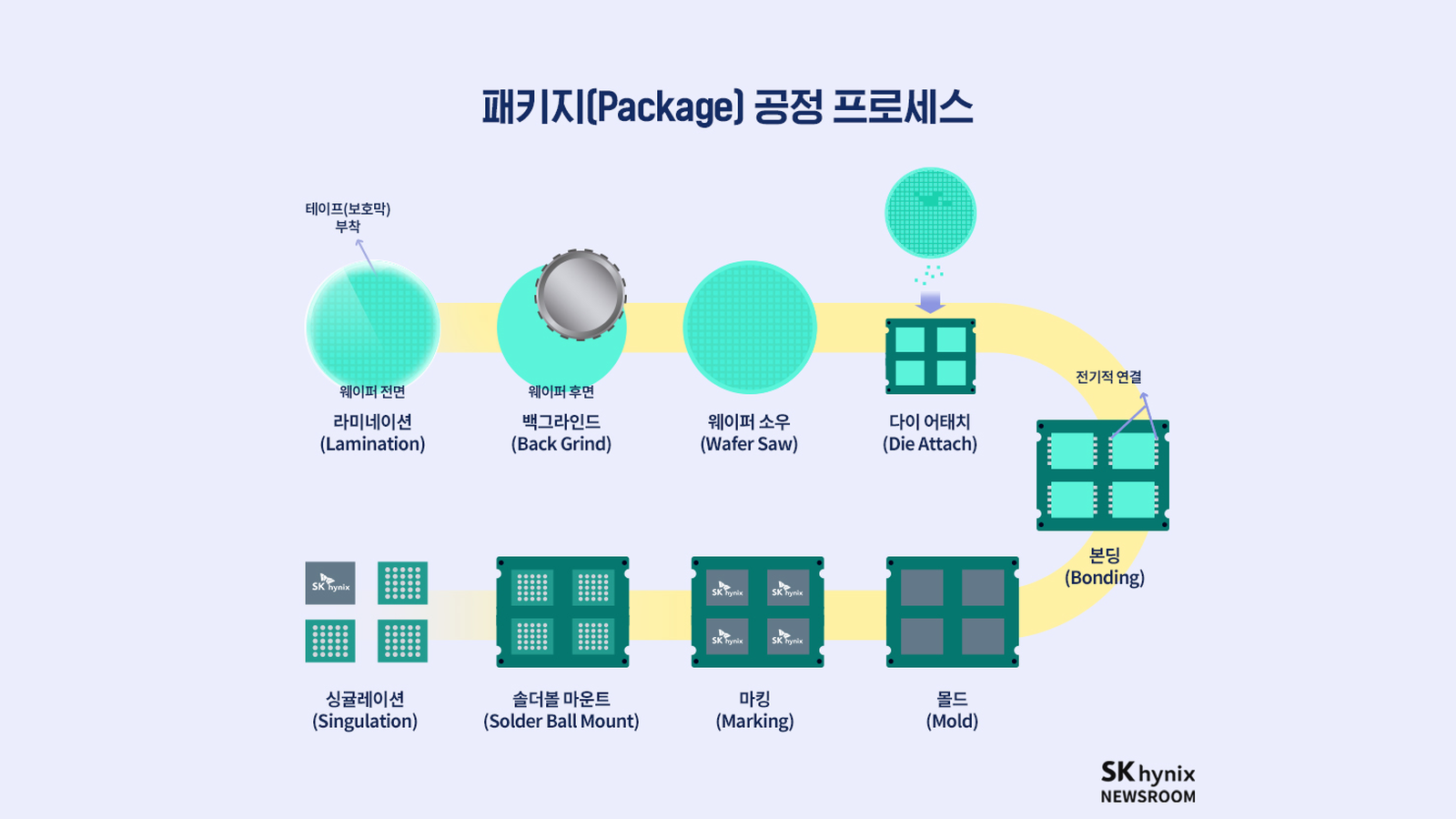

패키징은 반도체 제조 공정 중 후공정(Back-end Process)’에 해당된다. ‘전공정(Front-end Process)’에서 만들어진 웨이퍼를 개별 칩으로 자르고, 보호하고, 연결하는 공정들이 모두 후공정에 속한다. SK하이닉스는 패키징 기술을 소개하는 다양한 콘텐츠 시리즈를 통해 전문적인 역량을 선보여 왔으며, 그중 핵심 공정은 아래와 같다.

▲ 패키지 공정 프로세스

- 래미네이션(Lamination)

웨이퍼 표면에 보호 필름을 부착하여 이후 공정에서 발생할 수 있는 오염이나 물리적 손상을 방지하는 단계이다.

- 백 그라인드(Back Grind)

웨이퍼의 뒷면을 정밀하게 연마해 두께를 얇게 만드는 공정이다. 제품의 경량화와 고집적화를 위한 필수 과정으로, 패키징 전체 두께를 줄이는 데 기여한다.

- 웨이퍼 소우(Wafer Saw)

연마가 완료된 웨이퍼를 개별 칩(다이, Die) 단위로 절단하는 과정이다. 레이저 또는 다이아몬드 블레이드를 사용하여 고정밀 절단이 이뤄진다.

- 다이 어태치(Die Attach)

절단된 칩을 패키지 기판 위에 정밀하게 배치하고 접착하는 단계이다. 접착제 또는 솔더 소재를 이용하여 열전도 및 기계적 고정성을 확보한다.

- 본딩(Bonding)

칩과 기판 또는 칩과 다른 칩 사이의 전기적 연결을 형성하는 공정이다. 와이어 본딩(Wire Bonding), 플립칩 본딩(Flip Chip Bonding) 등 다양한 방식이 활용된다.

- 몰드(Mold)

패키지 전체를 에폭시 수지(Epoxy Molding Compound) 등으로 감싸 외부 충격, 습기, 오염 등으로부터 보호하는 단계이다. 패키지의 내구성과 신뢰성을 확보하기 위한 핵심 과정이다.

- 마킹(Marking)

완성된 패키지 상단에 제품 식별 정보(제조일, 제품 코드 등)를 인쇄하는 단계이다. 자동화된 레이저 또는 잉크 마킹 방식이 주로 사용된다.

- 솔더볼 마운트(Solder Ball Mount)

패키지 하단에 솔더볼(Solder Ball)을 부착하여, 기판이나 시스템 보드와의 전기적 연결을 준비하는 단계이다. 이 과정을 통해 패키지는 납땜을 통한 최종 조립이 가능해진다. SK하이닉스는 각 공정 단계에 최적화된 자동화 설비와 품질 관리 시스템을 적용해, 패키지의 정밀도와 신뢰성을 극대화하고 있다.

기술 고도화의 핵심, 패키징

지금까지 소개했듯, 패키징 기술은 고집적 메모리, AI 반도체, 고성능 서버용 칩 등 다양한 응용 분야에서 제품 차별화의 중요한 기준이 되고 있다. 이에 SK하이닉스는 HBM, TSV*, Micro Bump*, Fan-Out* 패키징 등 차세대 기술 기반의 패키징 역량을 바탕으로 제품 경쟁력을 확보하고 고객 신뢰를 높이는 데 힘쓰고 있다. 패키징은 그냥 거쳐 가는 반도체의 ‘마지막 단계’가 아닌 ‘성능을 완성하고, 가능성을 확장하는 출발점이자 핵심 기술’로 자리 잡고 있다.

* TSV: TSV는 실리콘 웨이퍼를 수직으로 관통하는 미세한 구멍을 통해 칩 내부 또는 칩 간 신호와 전력을 전달하는 고속 연결 기술

* Micro Bump: 칩과 기판 또는 칩과 칩 사이를 전기적으로 연결하기 위해 사용하는 미세한 납땜 볼(Solder ball)의 일종

* Fan-Out: 반도체 칩 외부에 재배선층(RDL, Redistribution Layer)을 넓게 확장해, 칩보다 더 넓은 면적에 입출력(I/O) 단자를 배치하는 패키징 기술

SK하이닉스 대학생 앰버서더_하닉어사전: 양산기술 P&T

▲ SK하이닉스 대학생 앰버서더 하닉어사전 양산기술 P&T 숏츠 이미지

이번 콘텐츠는 뉴스룸을 통해 공개된 이후 카드뉴스와 숏츠(Shorts) 형태로도 함께 발행된다. SK하이닉스 대학생 앰버서더들이 직접 기획·제작한 이번 시리즈는 자칫 어렵게 느껴질 수 있는 반도체 패키징 관련 내용을 보다 쉽고 흥미롭게 전달하고자 기획돼, 짧은 영상과 시각적인 콘텐츠를 통해 기술적 개념을 친근하게 풀어낼 뿐 아니라 위트 있는 표현과 감각적인 구성으로 정보 전달력도 높였다.

앞으로도 ‘하닉어사전’ 시리즈는 다양한 주제를 중심으로 뉴스룸, SNS 등 여러 채널을 통해 독자들과 꾸준히 소통할 예정이다. 기술을 향한 진입장벽을 낮추고 SK하이닉스의 전문성과 진정성을 널리 알리는 이 여정에 많은 관심과 기대를 부탁한다.