트랜지스터(Transistor, Tr)의 기능 중 메모리 반도체에서는 스위칭 기능이 매우 중요합니다. MOSFET Tr의 스위칭 기능은 드레인 전류로 ON/OFF를 결정하는데, 드레인 전류는 소스 단자를 떠난 전자들이 채널(Channel)을 거쳐 드레인 단자로 건너가면서 흐르게 됩니다. 반도체의 주기능 중 하나는 이러한 역할을 수행하는 자유전자를 생성하고 운반하는 것인데요. 이번 장에서는 Tr 단자를 형성하기 위해 불순물을 주입한 후(농도 변화) 잉여전자와 자유전자를 생성하는 과정과 그에 따라 전자가 존재하는 확률에 대해 알아보겠습니다.

자유전자의 생성

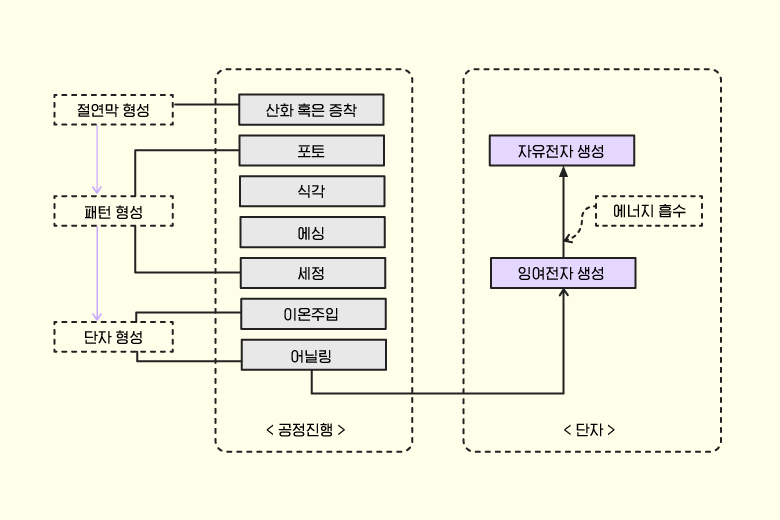

▲ 자유전자의 생성 과정

반도체에서 필요한 자유전자는 실리콘(Substrate)에 불순물 원자의 이온을 주입한 후, 온도를 약 800℃~1,000℃까지 올려 담금질하는 어닐링(Annealing)을 거쳐 형성된 소스 단자에서 생성됩니다. 소스 단자는 3족 혹은 5족의 원소(도펀트)가 4족인 실리콘과 공유결합한 후 공유결합에 참여하지 못한 잉여전자 혹은 정공들을 만들어냅니다. 이 잉여전자를 떼어내는 데는 공유결합에 참여한 전자들을 떼어내는 에너지보다 1/20 정도로 약한 에너지를 투입해도 가능하지요. 자유전자를 취득하는 데 있어 이같은 이점은 반도체 산업을 흥하게 한 요인 중 하나가 되기도 했지요. 전자뿐 아니라 정공 역시 조건만 약간 상이할 뿐 생성과정은 전자와 유사합니다.

▶<이온-임플란테이션 방식> 편/ <어닐링: 웨이퍼를 담금질하다> 편 참고

캐리어의 존재와 페르미-디락분포 확률함수의 의미

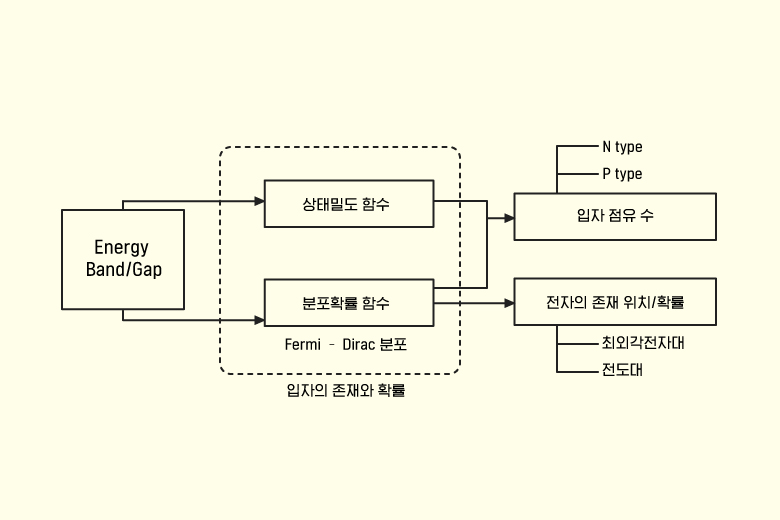

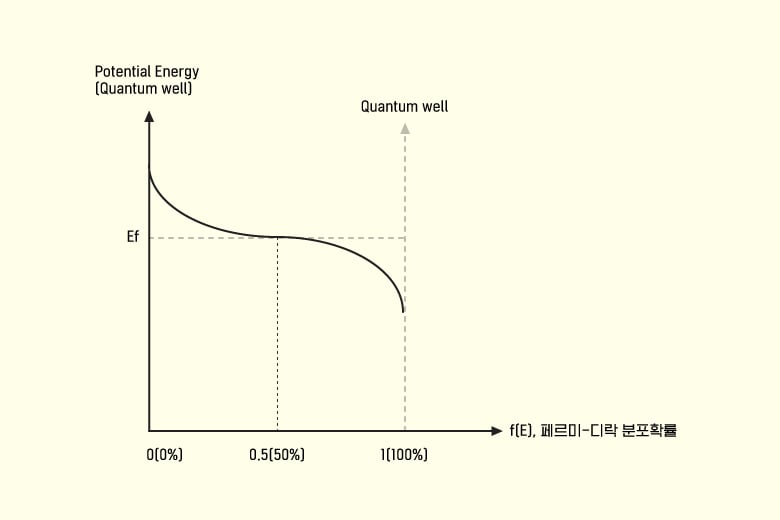

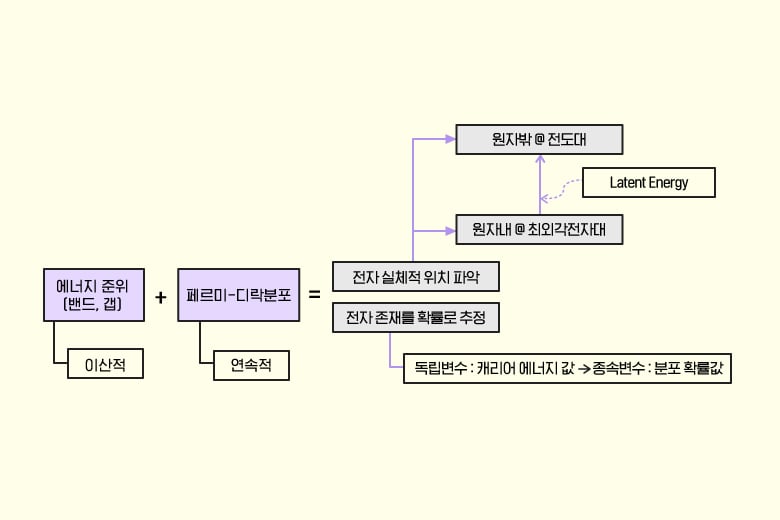

▲ 페르미-디락분포 확률함수의 역할

반도체 내 전자는 반도체를 구성하는 원자 내 궤도(오비탈)를 돌거나 혹은 원자와 원자 사이를 자유롭게 떠다니는 (자유전자) 2가지 경우로 존재합니다. 페르미-디락분포 확률함수는 캐리어(Carrier, 전자 혹은 정공)가 원자 내(최외각 껍질)에 머무는 확률을 지표로 나타낼 수 있는 함수인데요. 이를 통해 n형 반도체 및 p형 반도체 내에서 각각 Major 캐리어, Minor 캐리어를 확률값으로 나타내어 캐리어의 존재 여부를 확인할 수 있습니다. 페르미-디락분포 함수의 확률값이 높다는 것은 캐리어가 원자 내 최외각 껍질에 많이 머문다는 것이고, 확률값이 낮다는 것은 전자가 원자의 굴레로부터 탈출하여 자유전자로 많이 전이되었다는 의미입니다. 또한, 온도 변수와 농도 변수는 전자의 행동과 위치에 큰 영향을 끼치게 되는데요. 특히 이온 주입 시 도핑가스를 웨이퍼 표면에 얼마나 노출시켰느냐로 잉여전자(원자 내 포획된 전자)와 자유전자(원자로부터 탈출한 전자)를 확률적으로 예측할 수 있습니다. 단, 이는 어닐링(RTA)에 의해 도펀트들이 모두 실리콘과 공유결합에 성공했다는 전제가 성립되어야 가능합니다.

전자의 포텐셜 에너지 @ 페르미-디락분포 확률함수의 독립변수

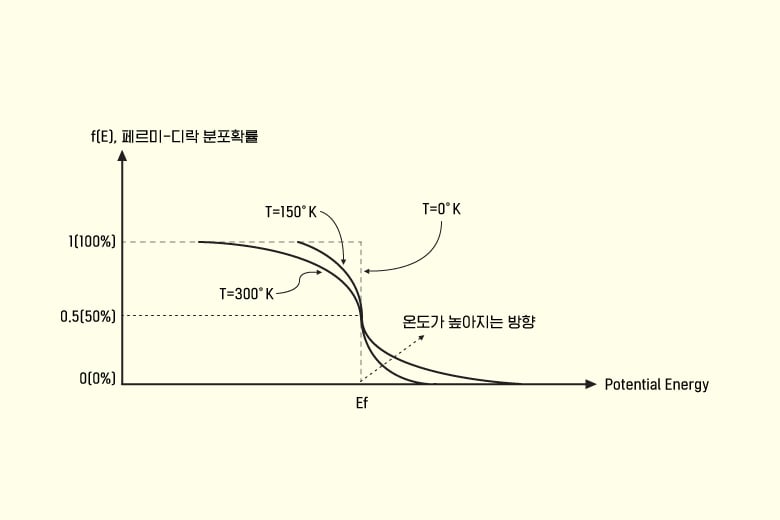

▲ 페르미-디락분포 함수 @2개 그래프는 x축(potential energy)과 y축(확률)값을 서로 교환한 그래프

반도체에서 페르미-디락 함수를 응용할 때 주어지는 조건인 독립변수는 캐리어(전자 혹은 정공을 의미하지만, 이하는 전자로 통칭)의 포텐셜 에너지(Potential Energy)입니다. MOSFET의 소스 단자와 채널, 혹은 드레인 단자 내 전자들이 어디(원자 내 혹은 밖)에 얼마나 있는지를 알아내기 위해 페르미-디락분포를 적용할 때, 전자가 가진 포텐셜 에너지를 독립변수로 페르미-디락분포에 대입하여 위치를 확률적으로 추정합니다(단, 정확한 전자 개수는 상태밀도함수를 함께 적용하여 계산해야 함). 여기서 전자의 위치를 통해 전자가 몇 퍼센트의 확률로 원자 내 최외각 껍질에 존재하는지 혹은 몇 퍼센트의 확률로 최외각 껍질에서 탈출했는지를 알아낼 수 있습니다.

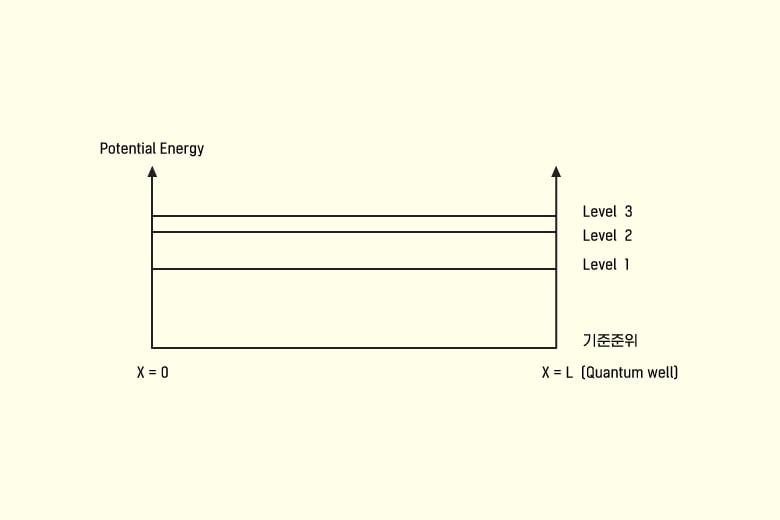

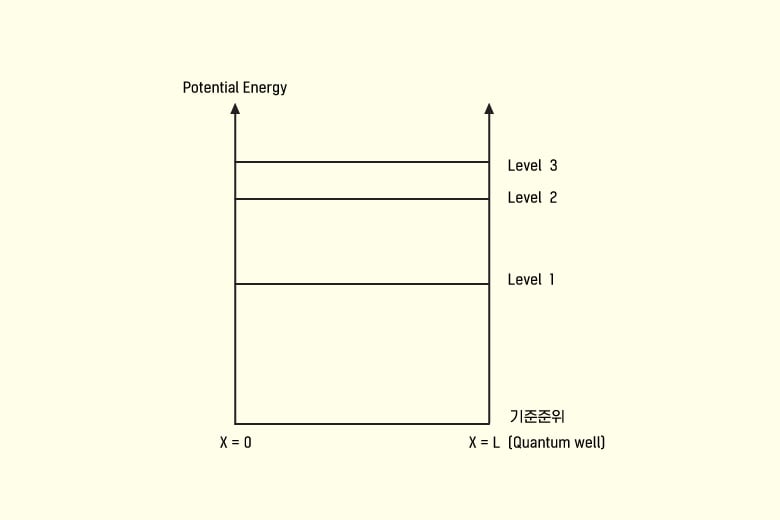

양자우물과 포텐셜 에너지

▲ 양자우물과 포텐셜 에너지 @ 입자 사이의 거리변수에 따른 영향

밀집대형을 이룬 결정성 실리콘 격자구조에 있어서는, 전자의 포텐셜 에너지는 양자우물의 에너지와 동일하다고 볼 수 있습니다. 다시 말해 원자와 원자 간 거리가 가까워지면 원자를 구성하면서 궤도를 돌고 있는 전자들의 포텐셜 에너지가 높아진다는 것이지요(슈뢰딩거 파동방정식: 전자의 양자화 개념을 베이스로 볼 때 양자우물의 길이가 좁아지면 양자우물에서의 입자에너지 준위level가 높아짐). 따라서 이온 주입 시 도즈량을 조절하여 불순물 농도에 변화를 주는 방식으로도 전자(입자)의 포텐셜 에너지값을 조절할 수 있습니다. 이렇게 얻은 전자의 포텐셜 에너지값을 페르미-디락분포 함수에 독립변수로 대입하여, 전자가 도펀트 원자 내 최외각 껍질에 존재할 확률을 알아낼 수 있습니다.

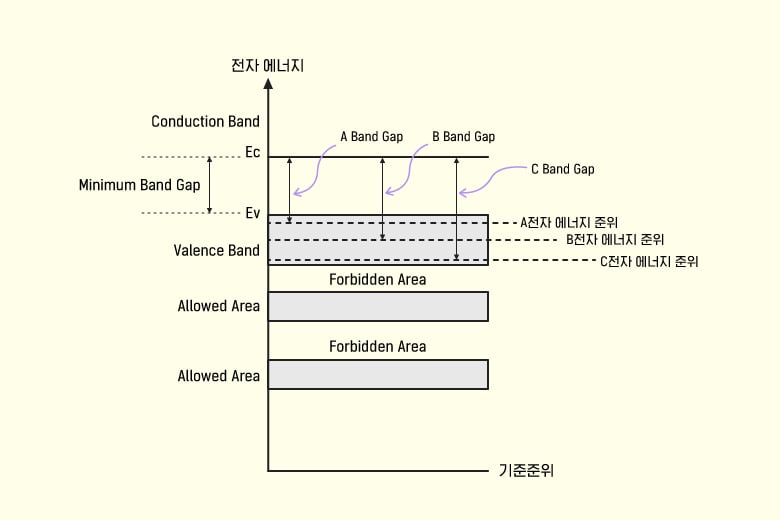

에너지 갭의 실체적 차이

▲ 에너지 갭의 실체적 차이

원자의 에너지 준위 Level이 고체 내에서는 원자 간 거리가 가까워지면서, 에너지밴드(대표적으로는 Valence band) 및 에너지 갭(밴드갭, 최외각 껍질의 전자를 원자로부터 탈출시키는데 소요되는 최소에너지)의 개념으로 발전했습니다. ▶ <반도체 전자와 에너지> 편 참고 에너지 밴드의 각 준위값들은 각 원자들의 최외각전자들이 보유하고 있는 에너지 준위값과 1:1로 대응되지요. 즉 여러 원자들이 모여 밴드를 형성(파울리의 배타원리에 의거)함으로써 각 원자 내 최외각전자들의 에너지 준위값은 제각각 달라집니다. 따라서 실리콘의 에너지 갭이 1.12eV(최소치)이지만 에너지 준위는 실체적 전자들의 포텐셜 에너지를 나타내므로, 각 원자들의 실제 에너지 갭 값들은 매우 미세하게 상이(1.12eV보다 높은 쪽으로)하다고 볼 수 있습니다. 이러한 에너지 갭 차이는 드레인 전류를 구성하는 최소한의 전자 개수를 예측하는 데 어려움을 줍니다. 다른 모든 공정변수가 이상적이라 할지라도 결국은 이상적이지 않은 상황(에너지 갭이 동일하지 않은 상황)이 발생할 수밖에 없다는 의미이지요.

전자 위치와 에너지

▲ 전자 위치와 Latent 에너지

#. Latent 에너지

반도체를 설계하거나 제품을 개발하는 입장에서는, 웨이퍼가 Fab out이 된 후 MOSFET 소자가 제대로 동작하느냐가 최대의 관심사입니다. 태아가 태어나서 숨을 쉬지 않으면 큰일이듯이 말입니다. 디바이스 동작의 주인공은 드레인 전류고, 드레인 전류의 핵심은 자유전자(정공)의 확보입니다. 자유전자는 최외각 껍질에 존재하던 전자가 일정량의 잠복 에너지(Latent 에너지)를 얻어야만 원자의 최외각 궤도를 이탈할 수 있습니다. Latent 에너지가 진성반도체인 경우는 에너지 갭인 셈이지요. 그런데 에너지 갭은 실리콘 결정격자가 형성되면서 고정되지만, Latent 에너지는 전자의 포텐셜 에너지(불순물 주입이 완료된 후 고정)에 따라서 가변적입니다(Latent 에너지=에너지 갭–불순물 주입으로 추가로 상승된 포텐셜 에너지). 포텐셜 에너지는 소스 단자 형성 시 도핑하는 불순물 농도가 높아지면 함께 상승합니다. 따라서 3족 혹은 5족의 불순물 도핑 농도를 높이면, 전도대까지 도달하는 경우 Latent 에너지를 줄일 수 있어 더욱 쉽게 자유전자를 획득할 수 있습니다. 또한, 도핑 농도를 높이면 페르미-디락분포 확률함수 전체가 상승합니다.

#. 에너지 개념에 대한 오해

전자의 존재와 이동은 미시세계의 물리적 현상이기에 고전물리학 개념으로 파악하기에는 어려움이 따릅니다. 에너지 개념은 이러한 반도체 전자를 이해하기 위해 도입되었지만, 전자의 물리적 현상을 에너지 개념(특히 페르미 에너지 레벨)으로만 해석하려다 보면 오해가 발생하기도 합니다. 물리적 현상과 에너지 개념을 함께 고려하면서, 반도체 내에서 전자의 존재와 이동을 이해해야 합니다.

먼저 전자의 물리적 위치는 원자 내(원자핵에 속박) 혹은 원자 밖(속박에서 해제), 2가지 경우로만 존재합니다. 전자/정공이 전도대 혹은 최외각전자대로 근접했다가 에너지 획득으로 jump하여 전도대(전자)/최외각전자대(정공) 속으로 들어가는 것이 아니라, 최외각 껍질에서 타원운동을 하던 전자가 Latent 에너지를 공급받아 물리적으로 원자 속박에서 탈출하는 형태이지요. Latent 에너지를 공급받는 동안에는 전자는 최외각궤도에 그대로 위치해 있습니다. 정공인 경우는, 옆에서 공유결합을 하고 있던 전자가 Latent 에너지를 공급받아 바로 이웃한 정공으로 뛰어 들면서 원래 있었던 자리에 정공을 만들어 놓는 형국이지요.

#. 에너지 금지대에 대한 오해

또한 궤도와 궤도 사이에 전자가 침범할 수 없는 물리적인 금지대가 있는 것은 아닙니다. 전자는 물리적으로 원자 내에 확률적으로 넓게 펴져 존재하며, 심지어 상위궤도를 도는 전자가 하위궤도를 도는 전자와 위치가 공간적으로 중첩(전기적 배타성으로 충돌되지는 않음)되기도 하지요. 하지만 전자들을 물리적으로 추적할 수 없어 이를 에너지로 환산하여 나타낸 것이 에너지 준위 혹은 밴드입니다. Ev는 최외각궤도 상에서 최외각전자가 어떤 위치에 있던 최대로 보유할 수 있는 포텐셜 에너지 값을 나타낸 것이지요. 또, 전자가 보유한 에너지 Level(에너지값)을 계산해 보았더니, 전자가 보유할 수 없는 에너지 영역(Ev보다 더 높은 에너지 영역)이 있어 이를 에너지 금지대(에너지 갭)라고 정의했습니다. 그러나 에너지 금지대는 Intrinsic 실리콘(혹은 저마늄) 상태일 때의 에너지 갭이고, 불순물이 첨가되면 전자의 포텐셜 에너지 Level이 Ev보다 상승하게 됩니다.

오늘은 원자 내 전자의 미시적인 세계에 대해 에너지를 매개체로 해석해보았습니다. 전자와 에너지의 관계를 설정하였고, 잉여전자와 자유전자의 차이점 및 에너지 밴드와 에너지 갭에 대하여도 알아보았습니다. 반도체 과학은 현재의 모순을 찾아내고 이를 해결하는 과정에서 계속 발전해나가야 합니다. 다음 장에서는 전자가 고체인 반도체 내에서 곧바로 드레인 전류로 투입 가능한 상태인지 예측할 수 있도록, 페르미-디락분포 함수를 이용하여 Intrinsic 및 Extrinsic, 절대온도 0도[K] 및 상온인 경우 등에 대해 확률적으로 알아보도록 하겠습니다.

※ 본 칼럼은 반도체/ICT에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.