지금까지 반도체는 경우의 수가 2개인 bit를 기준으로 시스템이 형성되고 발전해왔습니다. 이후 D램은 경우의 수가 3개, NAND는 4/8/16개 등으로 다(多)변화되었지요. 다만 D램에 3진법을 적용하려면 bit 체계를 trit 체계로 변경해야 하므로 향후 적용될 가능성은 희박합니다. 반면 NAND와 같이 경우의 수가 2진법 체계로 구성된 다(多)진법 반도체는 bit 체계를 연속적으로 발전시킬 수 있어 MLC, TLC, QLC 등 다양한 제품으로 개발되어 왔습니다. 오늘은 메모리 반도체가 어떠한 진법을 사용하는지를 알아보고, 이를 뒷받침하는 경우의 수가 bit 개념과 결합해 만들어내는 메모리 제품들을 쉽게 구분할 수 있는 시간을 마련했습니다.

1. 진법의 의미

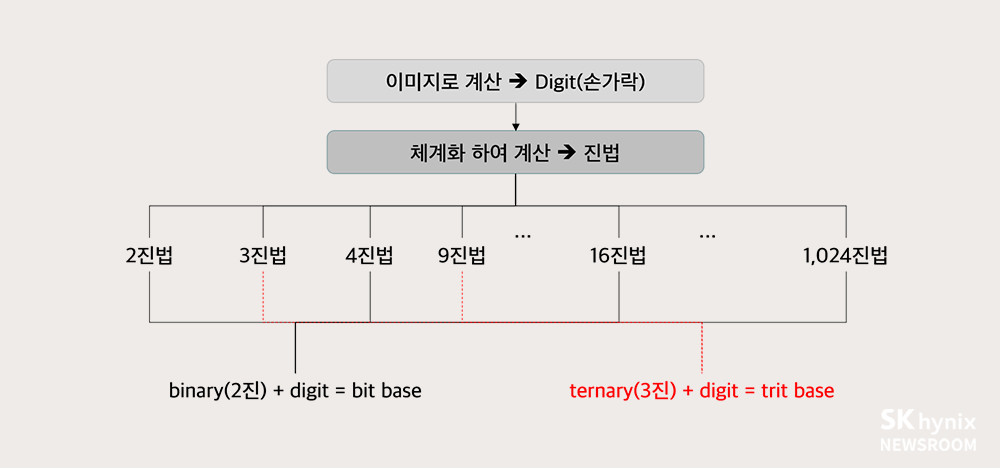

<그림1> 다양한 진법

숫자를 세거나 계산을 할 때, 인류는 약 250만 년 전부터 손가락을 이용했습니다. 우리가 흔히 쓰는 단어인 Digital(디지털)은 손가락을 뜻하는 Digit에서 파생된 것으로, ‘손가락화’라고 해석할 수 있습니다. 이렇듯 Digit으로 출발한 인류의 셈법은 오랜 세월을 거쳐 ‘진법’으로 발전했습니다. 진법은 2진법부터 3진법, 16진법, 64진법 등 무수히 다양한 종류로 만들어낼 수 있지요. 2의 제곱 진법은 2진법을 기본으로 표현하며, 3의 제곱 진법은 3진법을 기초로 전개할 수 있습니다. 따라서 반도체에서 2진법은 binary(2진)+digit=bit로 계산하고, 3진법은 ternary(3진)+digit=trit으로 계산합니다. 현재 모든 반도체의 시스템은 bit를 베이스로 구성돼 있습니다.

2. 진법과 반도체

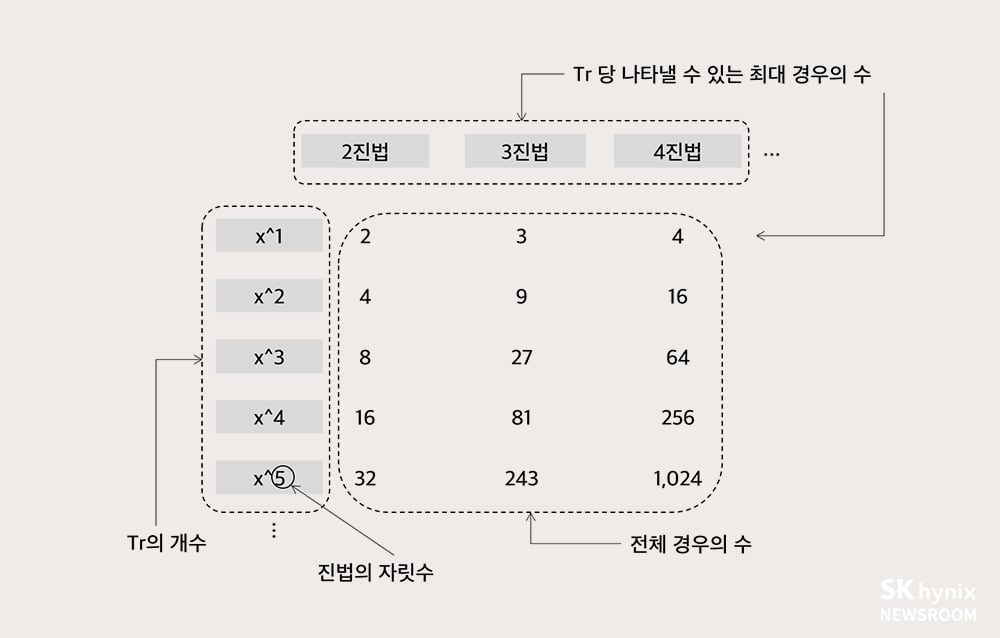

<그림2> 경우의 수와 Tr의 관계

점점 복잡한 연산이 요구됨에 따라 최근에는 반도체가 인간을 대신해 셈을 수행하게 됩니다. SW(소프트웨어)인 진법을 HW(하드웨어)인 반도체를 이용해 계산할 때에는, 1개 트랜지스터(Transistor, Tr)가 표현할 수 있는 최대 경우의 n개수가 n진법이 됩니다. Tr을 병렬방식으로 나열해 계산하면 각각의 Tr 개수는 진법의 자릿수가 됩니다. 예를 들어 2진법 “1011(2)”을 구현하려면 Tr이 4개가 필요하고, 각각의 자릿수는 ‘0’ 아니면 ‘1’로 표현됩니다.

3. 입력전압과 출력전류, 그리고 경우의 수

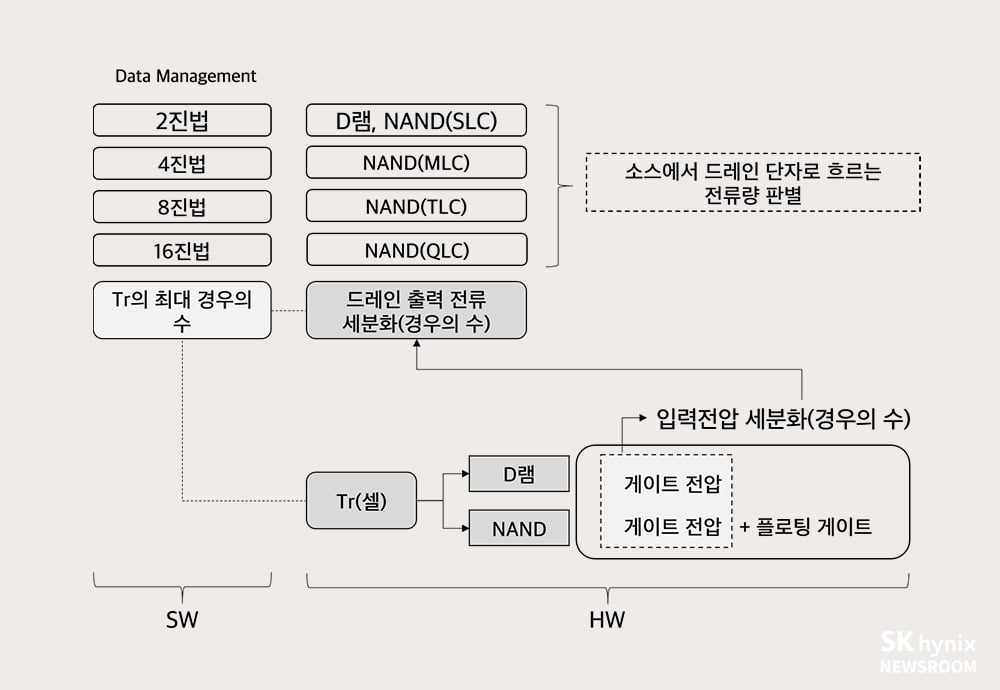

<그림3> 입력전압 세분화에 의한 드레인 출력전류의 세분화

Tr로 계산을 할 경우, 핵심은 1개 Tr(셀) 당 나타낼 수 있는 최대 경우의 수입니다. Tr에서 경우의 수는 주로 채널을 통과하는 드레인 전류(소스에서 드레인 단자로 흐르는 전자의 흐름)의 많고 적음으로 구분합니다. 이는 게이트 단자에 가해지는 전압(문턱전압)의 크기에 의해 영향을 받지요. ▶<문턱전압, MOSFET 동작의 첫걸음> 편 참고

D램에서는 게이트 전압의 Level을 2가지로 나눠 드레인 전류를 구분해 2진법 반도체로만 사용합니다. NAND에서는 입력되는 게이트 전압을 2/4/8/16가지로 구분해, 가짓수에 따라 SLC(2진법), MLC(4진법), TLC(8진법), QLC(16진법) 등 다양한 진법의 반도체로 양산 적용합니다. 문제는 게이트 전압 구간은 5[Vmax] 혹은 7[Vmax] 정도로 한정된 반면, 구분해야 할 세부 구간(경우의 수)은 많아진다는 것입니다. 그에 따라 드레인 전류를 구분하는 Step(경우의 수) 또한 더욱 세분화되어 드레인 전류의 미세한 차이를 판별하기 어려워집니다. ▶<낸드플래시 메모리의 원리> 편 참고

4. D램과 NAND의 진법

<그림4> 메모리 소자(Tr)로 구현 가능한 진법의 종류

경우의 수는 게이트 전압(NAND의 문턱전압)으로도 구분할 수 있지만, 드레인 전류(D램과 NAND)를 센싱하여 구분하는 데 사용합니다. 드레인 전류의 Level(경우의 수)이 2가지(ON+OFF)인 2진법은 현재 D램과 SLC NAND에 적용됩니다. 다만 3개의 Level로 구분되는 3진법은 D램에서 개발용 Working Sample에만 적용되고 있으며, NAND로도 2005년도에는 가능했으나 효용성 저하로 개발 자체를 하지 않았습니다. 4개의 Level로 구분되는 4진법은 MLC NAND에 적용됩니다. 8개 Level은 8진법으로 TLC NAND에 적용되며, 현재 가장 널리 쓰이는 제품이기도 합니다. 마지막으로 16개 Level로 구분되는 16진법은 읽기 위주의 기능을 하는 QLC NAND에 적용되어 양산되기 시작했지요. 그 외 다른 진법은 현재 반도체로 나타낼 수 없습니다.

5. TLC/QLC의 제품 표기 방식 바로잡기

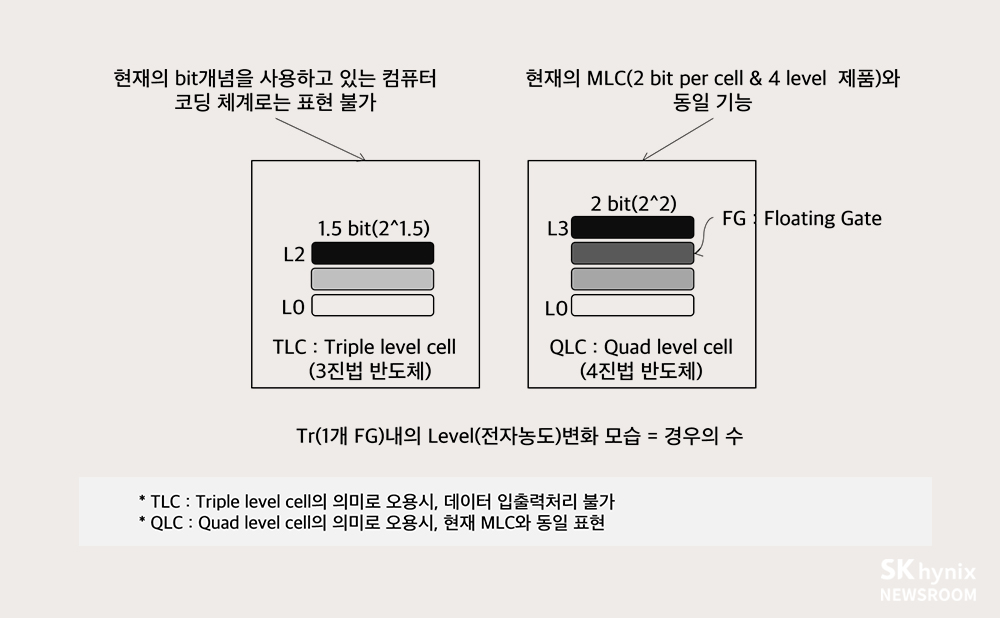

<그림5> 오용되고 있는 TLC/QLC의 표기 방식과 그에 따른 개념 해석

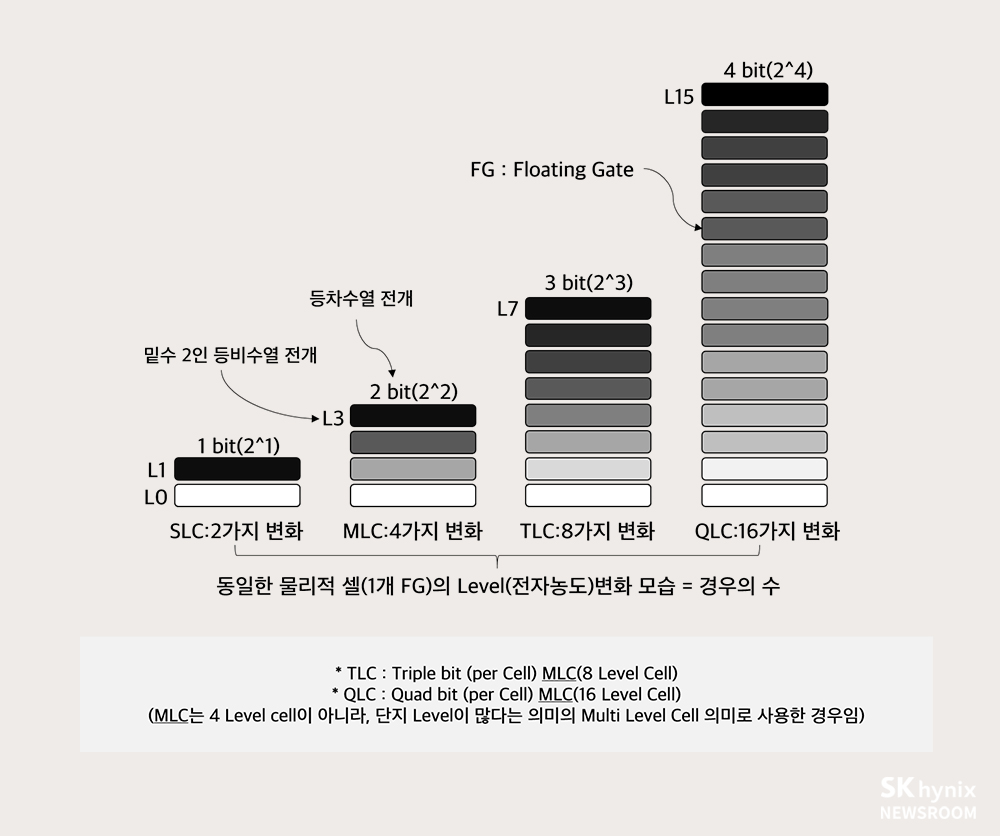

반도체의 용량과 직결되는 경우의 수는 2 Level이 1bit 동작을 나타낼 수 있습니다. 마찬가지로 4 Level은 2bit, 8 Level은 3bit, 16 Level은 4bit의 동작 특성을 보이게 되지요. 경우의 수는 진법으로 나타낼 수 있으므로 ‘n Level’은 곧 ‘n 진법’이 됩니다. 마치 Level과 bit의 관계는 2를 밑수로 하는 지수함수와 로그함수의 관계이지요. Level은 등비수열 이고, bit가 등차수열에 해당합니다.

하지만 현재 NAND 제품 중 TLC와 QLC는 본래의 의미와는 다르게 각각 Triple Level Cell, Quad Level Cell로 잘못 표기되어, Cell 당 표현 가능한 Level이 최대 3개 혹은 4개로 해석되고 있습니다. 이는 Level과 bit의 관계를 흐트러뜨리고, 메모리 용량을 기본으로 저장하고 읽기를 하는 메모리 반도체의 기능을 혼동하게 하는 표기입니다. 오기(誤記)된 제품의 명칭대로 풀이해보면 상기 <그림5>와 같이 해석됩니다.

<그림6> NAND플래시, TLC/QLC의 제품 표기에 따른 개념 해석

TLC, QLC와 같은 NAND의 제품명은 SK하이닉스에서 처음 사용하기 시작했습니다. 이는 필자가 8 Level NAND를 TLC(Triple bit per Cell MLC*), 16 Level NAND를 QLC(Quad bit per Cell MLC*)로 명명(命名)한 후, SK하이닉스 NAND개발본부 재직 시 이를 상정하여 사내 협의체에서 사용하기로 결정했던 것이 이후 전 세계로 통용된 것입니다(여기서 MLC*는 기존의 4 Level Cell이라는 MLC 제품 자체에 대한 의미가 아닌, 단지 Level이 많다는 뜻의 Multi Level Cell로 사용함). 따라서 제품의 개념은 본래의 취지대로 TLC는 Cell 당 3개 bit & 8개 Level, QLC는 Cell 당 4개 bit & 16개 Level로 표기해야 정확합니다. ▶저서 『NAND Flash 메모리』中 5장 문턱전압과 제품 다변화 참고

모든 경우의 수가 곧바로 반도체에 응용될 수는 없습니다. 이에 이번 장에서는 어떠한 Level이 bit 체계에 적용 가능한지를 되새겨보았습니다. 더불어 현재 전 세계적으로 오용되고 있는 NAND 제품(TLC/QLC)의 표기 방식에 대해 잘못된 부분과 정확한 의미를 짚어보았습니다. 진법-bit 개념-Tr-경우(Level)의 수를 이해하는 데 있어 오늘 충분히 다루지 못한 부분은 지난 반도체특강▶<낸드플래시 메모리의 원리> 편, <디램과 낸드플래시의 차이> 편 참고의 내용과 비교해보면 더 깊이 이해할 수 있을 것입니다.

※ 본 칼럼은 반도체/ICT에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.