반도체 기술력의 상징이었던 미세화(Scaling) 공정의 끝은 어디일까요? 반도체 발전을 추동해온 ‘무어의 법칙’이 더는 유효하지 않은 격변의 시대, 글로벌 반도체 기업들은 앞다퉈 치열한 생존 방안을 모색하고 있습니다. 미래 시장을 선점을 하기 위해선 지금까지와는 차원이 다른 기술이 필요하기 때문이죠. 반도체 칩의 핵심 소자인 트랜지스터 개발을 위해 4차원 차세대 기술인 ‘게이트 올 어라운드(Gate-All-Around, GAA)’ 구조 연구에 IBM과 인텔 등 대표적 반도체 기업들이 역량을 쏟는 것도 이 때문입니다.

반도체 업계의 차세대 기술, GAA의 등장

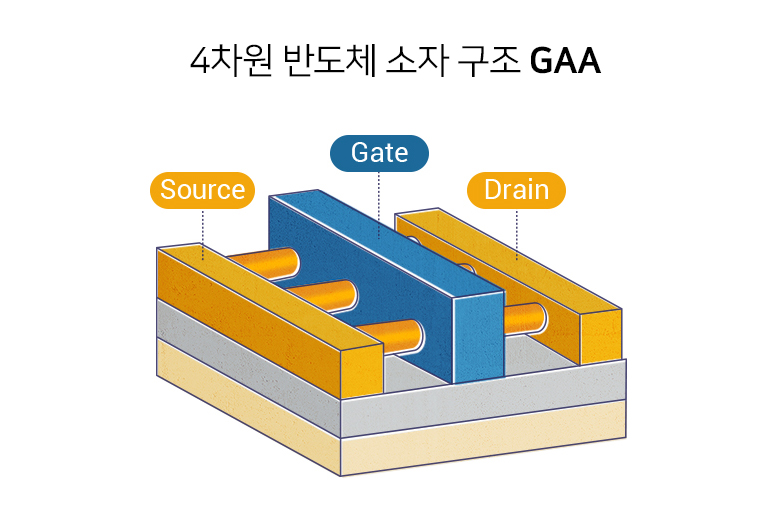

GAA는 로직 반도체 업계에서 ‘핀펫(FinFET)’ 다음 차세대로 꼽히는 기술을 말합니다. 현재의 메인스트림 기술인 핀펫이 윗면-앞면-뒷면 등 총 3면을 트랜지스터의 게이트로 쓰는 3차원이라면, GAA는 게이트의 아랫면까지 모두 쓰는 4차원 방식입니다. 업계에서는 14나노~5나노까지 핀펫 기술이 대체적으로 사용되고, 3나노부터 GAA 기술이 적용될 것으로 보고 있습니다.

반도체 회로를 구성하는 트랜지스터 소자의 Gate length를 줄이는 ‘미세화’는 그동안 업계의 지상 과제였습니다. 트랜지스터에서 게이트는 말 그대로 전류의 흐름을 조절하는 문 역할을 합니다. 문의 폭을 줄일수록 전자의 이동량이 많아져 회로의 동작 속도가 빨라지죠. 그러나 gate length를 줄일수록 누설전류가 커지고 단채널 효과(Short Channel effect)가 나타나는 부작용이 늘 문제였습니다. 이를 극복하기 위해 개발된 기술이 3차원 핀펫 공정과 4차원 GAA 구조입니다.

‘미세화 한계’의 구원투수, GAA

트랜지스터는 게이트에 일정 전압 이상을 걸면 게이트 아래에 채널이 형성되고, 이 채널을 통해 소스(Source)에서 드레인(Drain)으로 전자가 흐르며 동작하게 됩니다. 이때 게이트와 채널이 맞닿은 접점이 1차원 (Planar) 구조를 갖는 경우에는 게이트가 채널을 컨트롤할 수 있는 능력이 다차원 구조에 비해 부족하기 때문에 앞서 이야기한 누설전류와 단채널 효과 문제가 심각해집니다.

이를 극복하기 위한 3차원 핀펫 공정은 핀(Fin) 모양의 3D 구조를 적용, 채널의 3면을 게이트가 감싸면서 반도체 성능을 획기적으로 향상시키고 누설전류를 줄였습니다. 여기에서 한 차원 진화한 GAA 구조는 채널의 아랫면까지 모두 감싸 4면에서 게이트가 채널을 컨트롤합니다. 원통형을 앞-뒤-위-아랫면까지 모두 놓치지 않고 감싸 쥐는 듯한 구조라고 보면 쉽습니다.

나아가 업계에서는 유효채널 너비 (effective gate width)를 늘리는 방안도 연구 중입니다. 줄여야 좋은 gate length와 달리 gate width는 커질수록 전류량이 많아져서 반도체 성능이 향상되는데, GAA 구조에서도 여러 개의 채널을 수직으로 적층(stack)하는 방식을 적용하면 유효채널 너비를 늘릴 수 있어 다양한 특허기술들이 속속 나오는 추세입니다. 반도체 업계의 바람대로 아직 가보지 않은 3나노 이후 세대에서는 GAA가 보란 듯이 미세화의 한계를 극복할 수 있을까요?

벨기에 반도체 연구기관인 IMEC의 룩 반덴 호브 최고경영자(CEO)는 새로운 차원의 기술혁신을 통해 ‘미세화’가 계속돼야 한다고 강조했습니다. 그는 지난해 세미콘코리아 기조연설에서 “한가지 확실한 것은 반드시 ‘무어의 법칙’이 지속될 수 있도록 기술의 방향을 바꿔야 한다는 것”이라며 “현재 메인스트림인 핀펫 기술을 넘어 미세화 로드맵이 3나노, 2.5나노, 1.8나노까지 진전될 수 있는 솔루션이 있다고 확신한다”고 말했습니다. 미세화 한계를 돌파하기 위해 구원투수로 등장한 GAA가 열어나갈 새로운 시대를 기대해봅니다.

※ 본 칼럼은 반도체/ICT에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.