PC, 스마트폰의 용량과 속도 향상에 영향을 준 것 중 하나는 바로 D램의 발전입니다. D램은 CPU 성능 향상을 따라잡기 위해 변화를 시도했는데요. 발열 등 변화에 따른 문제점을 해결하면서 성장하고 있습니다. 지속적인 발전을 위한 D램의 뜨거운 도전사(史)를 알아보겠습니다.

무어의 법칙이 가져다 준 득과 실

반도체 업계에서 가장 큰 영향을 끼친 이론이라면 인텔 창업자 고든 무어가 만든 ‘무어의 법칙(Moore’s Law)’을 빼놓을 수 없습니다. 단순히 개인용 컴퓨터(PC) 시대를 넘어서 정보통신산업(ICT)으로의 진입을 가능케 했다는 점에서 더욱 그렇습니다. 시장조사업체 IHS마킷(IHS Markit)에 따르면 지난 20년 동안 무어의 법칙을 통해 형성된 직간접적인 영향은 최소 3조 달러(약 한화 3,369조원)에서 최대 11조 달러(약 한화 12경 353조원)에 이르는 미국 국내총생산(GDP) 성장을 만들어낸 것으로 나타났습니다. 그만큼 중앙처리장치(CPU)의 발전이 눈부셨다는 의미이기도 합니다. CPU의 발전에 발맞춰 PC는 전 세계적으로 확산되기 시작했고 오늘날과 같은 스마트폰 시대가 등장할 수 있는 계기를 만들게 됩니다.

▲ ‘무어의 법칙’의 주인공 고든 엘 무어(Gordon Earle Moore)

CPU는 크게 두 가지 관점에 맞춰 생각할 수 있습니다. 하나는 아키텍처이고 다른 하나는 클록입니다. PC에 장착되는 CPU는 인텔이 아니면 AMD이고 두 회사의 제품은 ×86 아키텍처를 씁니다. 스마트폰의 경우 지난해 소프트뱅크가 인수한 영국 설계자산(IP) 업체 ARM의 아키텍처가 대부분입니다. 아키텍처가 다른 CPU의 소프트웨어는 호환이 되지 않습니다. 안드로이드 앱을 윈도우가 설치된 PC에 곧바로 설치할 수 없는 이유죠. 가상운영체제 등을 이용하면 가능하긴 하지만 불편한 건 사실입니다.

클록은 어떨까요? 같은 아키텍처를 가지고 있는 경우라면 작동주파수인 클록이 높을수록 빠른 속도를 낼 수 있습니다. 당연히 데이터를 더 많이 처리할 수 있죠. 그런데 이게 전부는 아닙니다. 무어의 법칙 덕분에 CPU는 나날이 성능이 높아졌지만 주변에 있는 반도체는 그렇지 못했습니다. 그래서 일종의 완충장치인 버퍼를 두게 됐고 PC 성능의 발목을 잡는 병목현상을 줄이기 위한 처절한 줄다리기가 시작됩니다.

용량과 속도 모두 잡아야 하는 D램

퀴즈를 하나 내보겠습니다. PC 성능을 높이려면 D램의 클록을 높이는 게 좋을까요, 아니면 용량을 키우는 것이 더 나을까요? 일반적인 경우라면 정답은 용량입니다. 운영체제(OS)와 CPU에 따라 상황이 다르지만 주메모리 용량이 클수록 PC를 구성하는 각 부품의 부담이 한결 줄어듭니다. 이는 워크스테이션이나 서버, 심지어 슈퍼컴퓨터도 다르지 않습니다. 최근 반도체 호황의 이유도 여기서 찾을 수 있습니다. 클라우드를 통해 다양한 서비스를 제공하기 위해서는 한정된 인터넷데이터센터(IDC)와 전력소비량, 운용비용 등을 고려했을 때 서버의 수를 늘리기보다는 서버의 성능을 높여주는 것이 더 유리합니다. 가상화를 원활하게 돌리려면 서버에 탑재되는 주메모리 용량을 크게 늘려줘야 합니다.

PC의 경우는 조금 다른 이유로 무조건 주메모리 용량이 크다고 해서 좋은 것은 아닙니다. 오히려 별로 체감이 되지 않거나 이론적으로 성능이 떨어지는 경우도 있죠. 가령 4GB, 8GB보다는 12GB나 16GB가 더 성능이 좋아야 하지만 꼭 그렇다는 보장은 없습니다. 여기에는 CPU 속도, OS, 사용하는 소프트웨어 종류 등 다양한 요소가 영향을 끼치기 때문입니다. 성능을 좋게 만들려면 속도도 뒷받침되어야 합니다. 전력소비량도 마찬가지지요. 단순히 노트북뿐 아니라 서버에서도 매우 중요합니다. 단 0.1볼트(V)의 전압만 낮출 수 있어도 전체 서버와 1년 내내 운용되는 상황을 고려하면 상당한 에너지를 절약할 수 있습니다.

잠시 CPU 이야기로 돌아오겠습니다. 앞서 CPU 속도가 너무 빨라 버퍼를 둬야 한다고 설명했는데요. 상대적으로 D램 속도가 느리다는 의미이기도 합니다. 그래서 D램보다 빠른 S램을 캐시메모리로 활용하기로 했습니다. S램은 D램보다 훨씬 속도가 빠르지만 가격이 비싸 무작정 용량을 늘릴 수 없습니다. 처음에는 CPU 밖에 설치되어 있어서 동기화, 그러니까 CPU와 같은 클록으로 작동하지 못했지만 그래도 1/3이나 절반 정도의 속도로 움직여서 D램 사이에서 충분한 역할을 해줬습니다. 이후에는 CPU 내부에 함께 통합됐는데요. CPU의 내부 구조가 복잡해지고 코어 수가 늘어나면서 보통 레벨1(L1), 레벨2(L2), 레벨3(L3)까지 이용하게 됐습니다. 용량은 L3>L2>L1 순으로 작습니다.

CPU 속도를 뒷받침하라!

반도체 업계에서는 캐시메모리에 그치지 않고 D램 속도를 높일 수 있는 방법을 연구하기 시작합니다. 그래서 주목한 것이 버스(BUS)죠. 버스는 데이터가 오고 가는 통로를 말합니다. 단순하게 D램의 속도가 느리니 버스를 넓혀서 성능을 높여보자는 연구진들의 생각에서 출발했습니다. 단순하지만 이게 생각보다 쉬운 방법은 아닙니다. 가장 큰 문제는 ‘돈’이죠. 예컨대 ‘CPU↔메모리’ 버스를 16비트에서 32비트로 확장하면 확실히 성능은 좋아지지만 그만큼 인쇄회로기판(PCB)을 두껍게 설계해야 해서 가격이 비싸집니다. 그래서 그래픽카드에서 그래픽처리장치(GPU)와 그래픽메모리 사이의 버스가 높아질수록(64비트→128비트→256비트→512비트) 가격이 올라갑니다.

버스를 넓혀서 ‘채널’을 한 개(Single)가 아닌 두 개(Dual)로 만들고 인터페이스도 병렬(Parallel)이 아닌 직렬(Serial)을 사용해보는 등 다양한 시도를 거듭합니다. 과거에는 반도체 소자 하나하나의 성능이 부족했기 때문에 직렬보다는 병렬 인터페이스를 더 많이 썼습니다. 대표적인 병렬 인터페이스에는 흔히 프린터 포트라 부르던 Parallel Port, 그리고 오랫동안 하드디스크드라이브(HDD)에 쓰였던 IDE가 있습니다. 워크스테이션과 서버에서 쓰던 SCSI(small computer system interface)도 대표적인 병렬 인터페이스인데요. 이 병렬 인터페이스는 속도를 높일수록 케이블이 두꺼워져서 비용적으로 부담이 될 뿐 아니라 설치와 사용이 불편하다는 단점이 생겼습니다.

지금은 IDE와 SCSI가 시리얼ATA(SATA), SAS로 바뀐 상태입니다. 한편으로는 직렬·병렬 인터페이스가 한층 개선되면서 USB와 썬더볼트로 발전하게 됩니다. 솔리드스테이트드라이브(SSD)와 같은 낸드플래시는 Non-Volatile Memory Express(NVMe)가 등장하기도 합니다. NVMe나 eMMC(Embedded Multi Media Card), UFS(Universal Flash Storage)에 대해서는 기회가 닿으면 자세히 알아보겠습니다.

램버스D램의 탄생

버스와 인터페이스와 함께 D램 자체의 성능, 그러니까 CPU와 마찬가지로 클록을 높이는 노력도 함께 이어졌습니다. 그 즈음에 나온 D램이 ‘램버스D램(RDRAM)’이죠. 이 제품을 한 마디로 ‘고속으로 작동하는 직렬 D램’이라고 생각하면 됩니다. 경쟁했던 S(Synchronous)D램(SDRAM)이 16비트에 싱글 채널이었다면, 램버스D램은 32비트에 듀얼 채널로 작동했습니다. 여기에 쓰인 기술이 그 유명한 DDR(Double Data Rate)이고요. 반도체는 일정 주기(클록)로 작동하는 부품입니다. 헤르츠(Hz) 단위로 표기하는데요. 한 번의 클록으로 인해 발생한 사이클(주기)에서 두 번 데이터를 내보냅니다. 클록 한 번에 두 번(더블) 데이터를 내보낸다고 보면 되죠.

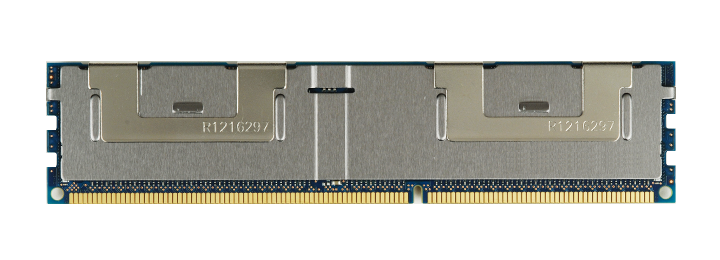

▲ 서버용 메모리는 안정성을 높이고 D램에서 발생하는 열을 식히기 위해 방열판을 장착하는 경우가 있다.

이렇게 빠른 속도가 필요했던 이유는 인텔이 내놓은 펜티엄4의 철학을 맞추기 위해서였습니다. 내부 파이프라인을 깊게 설계해 클록을 크게 높였던 펜티엄4를 램버스D램과 결합해 PC 성능을 높이려고 한 것이죠. 결과적으로는 실패했지만 램버스D램의 개념은 결국 DDR SD램으로 이어졌으니 메모리반도체 업계 입장에서는 나쁠 것이 없었습니다. 흥미롭게도 빠르게 작동하는 램버스D램에는 기본적으로 방열판이 달려서 판매됐습니다. 그만큼 열이 많이 났다는 이야기입니다. 요즘 판매되는 일부 서버용과 오버클록킹을 위한 마니아용 D램에도 방열판이 달리는 경우가 많으니 선구자적인 역할을 톡톡히 한 셈이네요.

여러 가지 무기를 달고 CPU의 속도를 맞추기 위해 노력했던 D램은 또 하나의 변화를 겪습니다. 바로 메모리 컨트롤러의 통합입니다. 버퍼로 쓰인 S램이 CPU 외부에 있다가 내부로 통합됐다는 이야기를 했습니다. 같은 경우입니다. 직전까지 FSB(Front Side Bus)를 활용한 일종의 3요소(CPU↔메모리 컨트롤러↔D램) 개념에서 메모리 컨트롤러를 CPU에 넣어 성능 향상을 꾀한 것입니다. 이로써 D램에게는 또 하나의 숙제가 주어졌습니다. 결국 용량은 용량대로 구현하면서 성능을 높이는 본질적인 부분을 어떻게 해결하느냐가 관건이 된 것이죠.

열 줄이기 또한 성능 향상을 위한 D램의 숙제 중 하나입니다. 여름철 PC나 스마트폰 열을 줄이기 위해서는 D램의 열을 빠르게 식혀줘야 합니다. 물리적으로는 램버스D램이나 일부 고가 제품처럼 방열판을 달아주는 것이 좋지만 이것이 능사는 아닙니다. 스마트폰은 그럴 수 없으니까요. 오히려 애플리케이션프로세서(AP) 바로 위에 패키징 온 패키징(PoP) 형태로 얹어져 있어서, AP가 내는 열을 고스란히 받아내야 합니다. 손쉬운 방법은 메모리 정리 기능을 작동시키는 것입니다. 그리고 불필요한 애플리케이션과 소프트웨어를 삭제하고 주기적인 업데이트로 기기를 관리하면 발생하는 열을 한결 낮출 수 있습니다.

D램의 미래, 적층에서 시작해 뉴로모픽칩으로

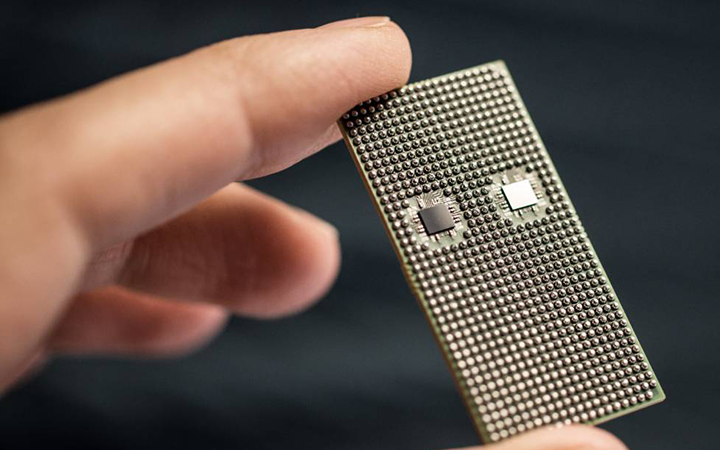

▲차세대 D램은 결국 적층을 통해 하나의 칩으로 구현될 가능성이 높다.

앞으로 D램의 미래는 어떻게 될까요? 다양한 뉴메모리 후보가 있지만 D램만큼 성능과 검증이 이뤄진 제품은 아직 없습니다. 홍성주 SK하이닉스 미래기술연구소장(부사장)의 설명에서 팁을 얻을 수 있습니다. 그는 “연관 공정 사이의 매칭이 중요하고 빅데이터를 활용해서 수율에 미치는 특이한 패턴의 발견과 피드백을 받아야 한다”며 “더 엄밀한 과학적 접근을 통해 연구개발(R&D)이 이뤄져야 한다”고 강조한 바 있습니다. 가장 유력한 방법은 ‘적층’입니다. 이미 HBM(High Bandwidth Memory)과 같은 제품이 등장했죠.

이후에는 CPU 내부로 통합된 S램이나 메모리 컨트롤러, 혹은 GPU처럼 D램도 궁극적으로는 시스템온칩(SoC)화가 되리라 예상됩니다. 실제로 유럽 최대 반도체 기술 연구소(IMEC)는 CPU, 메모리, 컨트롤러, 각종 입출력(I/O)가 하나의 칩에 적층될 것으로 보고 있습니다. 각 칩을 아파트처럼 쌓아 올려 여러 개의 코어를 하나로 통합하고 메모리는 위쪽에, I/O를 아래쪽에 배치해 3D로 적층하는 것이 가능하다는 이야기입니다.

▲SK하이닉스가 뉴로모픽칩과 같은 신기술 개발에 매진하는 이유는 결국 모든 반도체가 하나로 통합되리라 보기 때문이다.

SK하이닉스가 뇌를 모사한 ‘뉴로모픽칩’ 연구에 들어간 이유도 여기에 있습니다. 미국 스탠포드대학교와 강유전체 물질을 활용한 ‘인공신경망 반도체 소자 공동 연구개발’을 진행하고 있죠. 뉴로모픽칩은 인공신경망 반도체 소자를 기반으로 사람 뇌의 사고과정을 모방한 반도체인데요. 최근 빅데이터 시대에 방대한 양의 데이터 중에는 사람과는 달리 기계가 쉽게 인식하기 어려운 비정형적인 문자·이미지·음성·영상 등이 혼재해 있습니다. 뉴로모픽칩은 이러한 비정형적인 데이터를 처리하는 데 효율적인 것으로 알려져 있습니다.

흔히 과거를 돌아보며 미래를 내다봐야 한다는 말을 합니다. D램의 미래는 결국 적층이 될 겁니다. 그러나 그 모습은 지금의 적층과는 많이 다를 것으로 예상됩니다. 그때의 SK하이닉스는 단순히 메모리 반도체를 주력하는 기업이 아니라 SoC까지 아우르는 역량을 갖추게 될 가능성이 큽니다. 그러려면 D램을 넘어서서 뉴메모리까지 멈추지 않는 열정으로 R&D가 이뤄져야 합니다. SK하이닉스가 그 중심에 있기를 바랍니다.

※ 본 칼럼은 반도체/ICT에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.