SK하이닉스의 성공 신화의 밑바탕이 된 기술은 셀 수 없이 많지만, 그중에서도 가장 놀라운 것은 바로 ‘미세공정’이다. 육안으로는 보이지 않을 정도로 작은 회로를 더욱 세밀하게 만들어 내는 SK하이닉스는 압도적인 기술력으로 이미 글로벌 반도체 업계를 선도하고 있으며, 이러한 위상의 근간에는 ‘원팀 스피릿(One Team Spirit)’이 있다.

3편에서는 업계 최고 수준인 SK하이닉스의 미세공정 역량을 살펴보고, D램 산업을 이끌어온 원팀 스피릿이 발현된 순간들을 되돌아본다.

미세공정, 반도체 혁신의 ‘핵심 오브 핵심’

반도체 회로를 작게 만드는 미세공정은 기술 혁신에 있어 선택이 아닌 필수로 여겨져 왔고, 오늘날에도 중요한 경쟁력으로 꼽힌다.

미세공정이 중요한 이유는 반도체 성능 및 생산성과 직결되기 때문이다. 이 기술을 통해 반도체가 작아지면 같은 크기의 웨이퍼에서 더 많은 칩을 생산하는 것이 가능해진다. 또한, 하나의 칩 안에 집적할 수 있는 트랜지스터 수가 늘어나 동일 면적에서의 데이터 처리 능력이 높아진다. 뿐만 아니라, 트랜지스터 등 소자의 크기가 작아져 칩 전체의 소비 전력과 발열량이 감소한다.

이처럼 처리 속도, 에너지 효율, 신뢰성까지 모두 끌어올리는 미세공정 기술을 SK하이닉스는 ‘원팀 스피릿’을 통해 세계 최고 수준으로 구현하고 있다.

기술 한계란? 결국 돌파해 내는 것

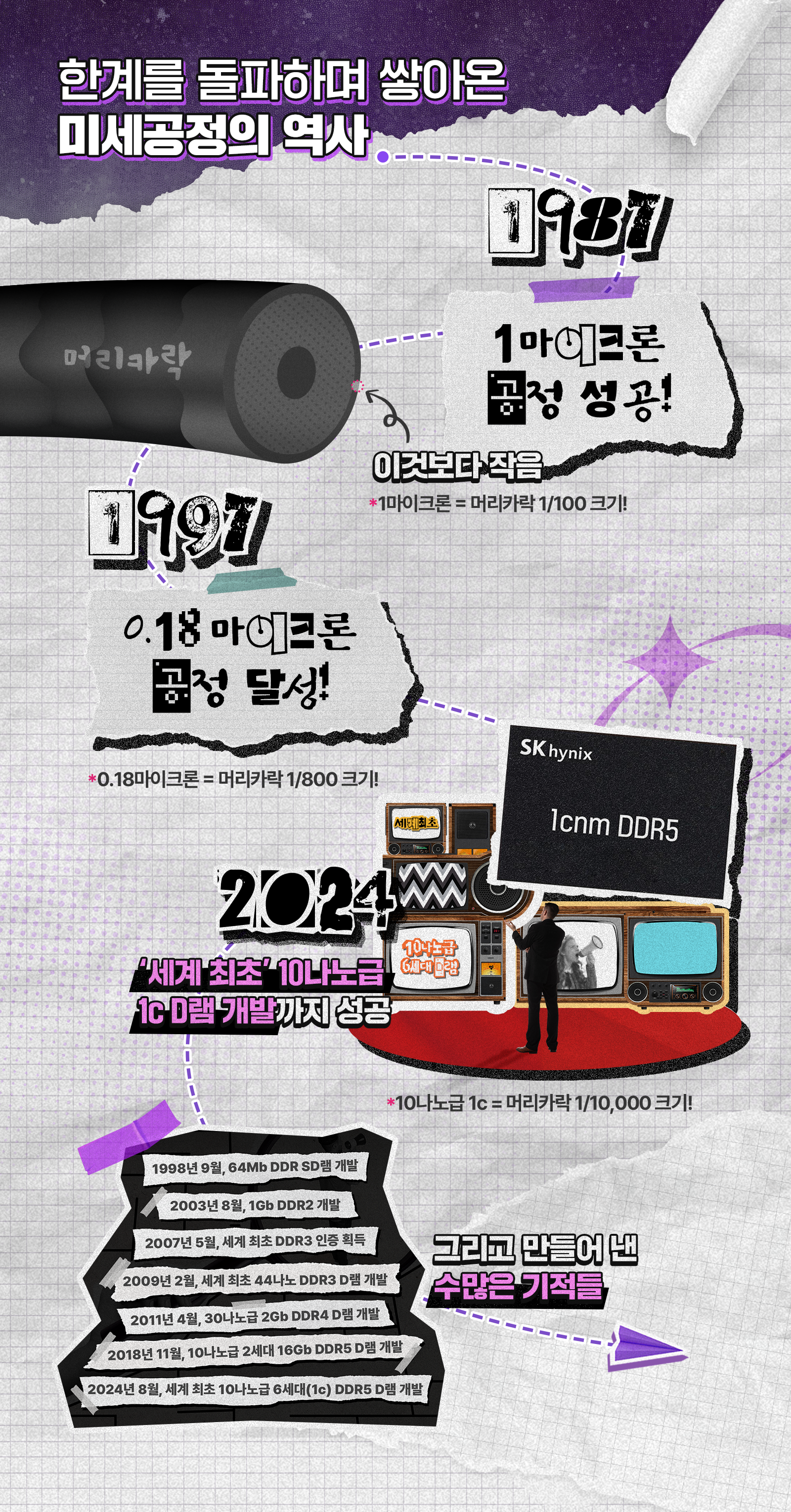

SK하이닉스가 걸어온 미세공정 기술개발의 역사는 ‘한계’와의 싸움, 그 자체였다. 1983년 처음 반도체 산업에 발을 들인 SK하이닉스는 후발주자였음에도 불과 4년 만인 1987년, 머리카락 100분의 1 정도로 얇은 1마이크론(μm)* 공정 개발에 성공했다.

* 마이크론(μm): 100만분의 1m(미터). 수치가 낮을수록 미세화 정도가 높아짐

회사는 여기서 멈추지 않고 연구개발과 투자를 이어가며 1997년 외환위기(IMF) 속에서도 머리카락 두께의 800분의 1 수준인 0.18마이크론 공정을 개발해 다시 한번 업계를 놀라게 했다.

미세공정은 계속해서 발전을 거듭해 오다 2000년대에 들어서는 10억분의 1미터(m)인 나노(nm) 단위에 이르게 된다. SK하이닉스는 회로 선폭을 더 얇게 줄이며 2006년 60나노급, 2009년 40나노급, 2010년 30나노급, 2012년 20나노급, 2018년 10나노급으로 기술력을 계속 고도화해 왔다.

그동안 업계에서는 2년마다 집적도(미세화)가 2배씩 높아진다는 ‘무어의 법칙(Moore’s Law)’이 통용되어 왔지만, 공정 난이도가 높아지면서 기술이 한계에 다다랐다는 우려가 커졌다.

SK하이닉스는 도전을 멈추지 않고 개발에 매진한 결과, 2024년 세계 최초로 10나노급 6세대(1c)* 기술을 확보하는 데 성공[관련기사]했다. 10나노 초반의 극미세화된 공정인 1c 기술은 무려 머리카락 두께의 1만분의 1 수준이며, 이를 기반으로 SK하이닉스는 성능 면에서 이전 세대인 1b 대비 동작 속도는 11%, 전력 효율은 9%의 개선을 이뤄냈다.

* 10나노급 6세대(1c): 10나노급 D램 공정 기술은 1x-1y-1z-1a-1b-1c 순으로 개발됨

1c D램 개발이 더욱 특별한 이유는 기술적 난이도가 급격히 높아지는 분기점이기 때문이다. 단순히 회로를 미세하게 그리는 차원을 넘어, 원자 단위의 물리적 한계, 전자 이동의 불확실성, 데이터 신호의 간섭 문제 등 수많은 난제가 여기서 발생한다. 이를 극복하기 위해 SK하이닉스는 광원의 파장이 짧아 더 세밀하게 회로를 그릴 수 있는 ‘극자외선(EUV)’ 노광 기술을 적극 도입하는 등 미세 패턴 형성의 정확도를 끌어올리며 1c 기술 개발에 성공했다.

이 밖에도, SK하이닉스는 D램 속도 성능을 높여주는 DDR(Double Data Rate) 기술을 업그레이드해 왔다. ▲1998년 64메가비트(Mb) SDRAM 양산 ▲2003년 세계 최초 1기가비트(Gb) DDR2 개발 ▲2007년 세계 최초 DDR3 인증 획득 ▲2009년 세계 최초 44나노 DDR3 D램 개발 ▲2011년 30나노급 2Gb DDR4 D램 개발 ▲2013년 업계 최초 20나노급 LPDDR4 D램 개발 ▲2018년 10나노급 2세대 16Gb DDR5 D램 개발 ▲2020년 세계 최초 DDR5 D램 출시 등 회사는 시장을 선도하는 기록을 경신해 왔다.

이처럼 기술의 벽을 넘기 위해 SK하이닉스가 계속해서 앞으로 나아가게 한 원동력은 바로 모든 구성원이 하나로 뭉치는 원팀 스피릿이었다.

완벽한 하모니로 이뤄낸 역사적 성과

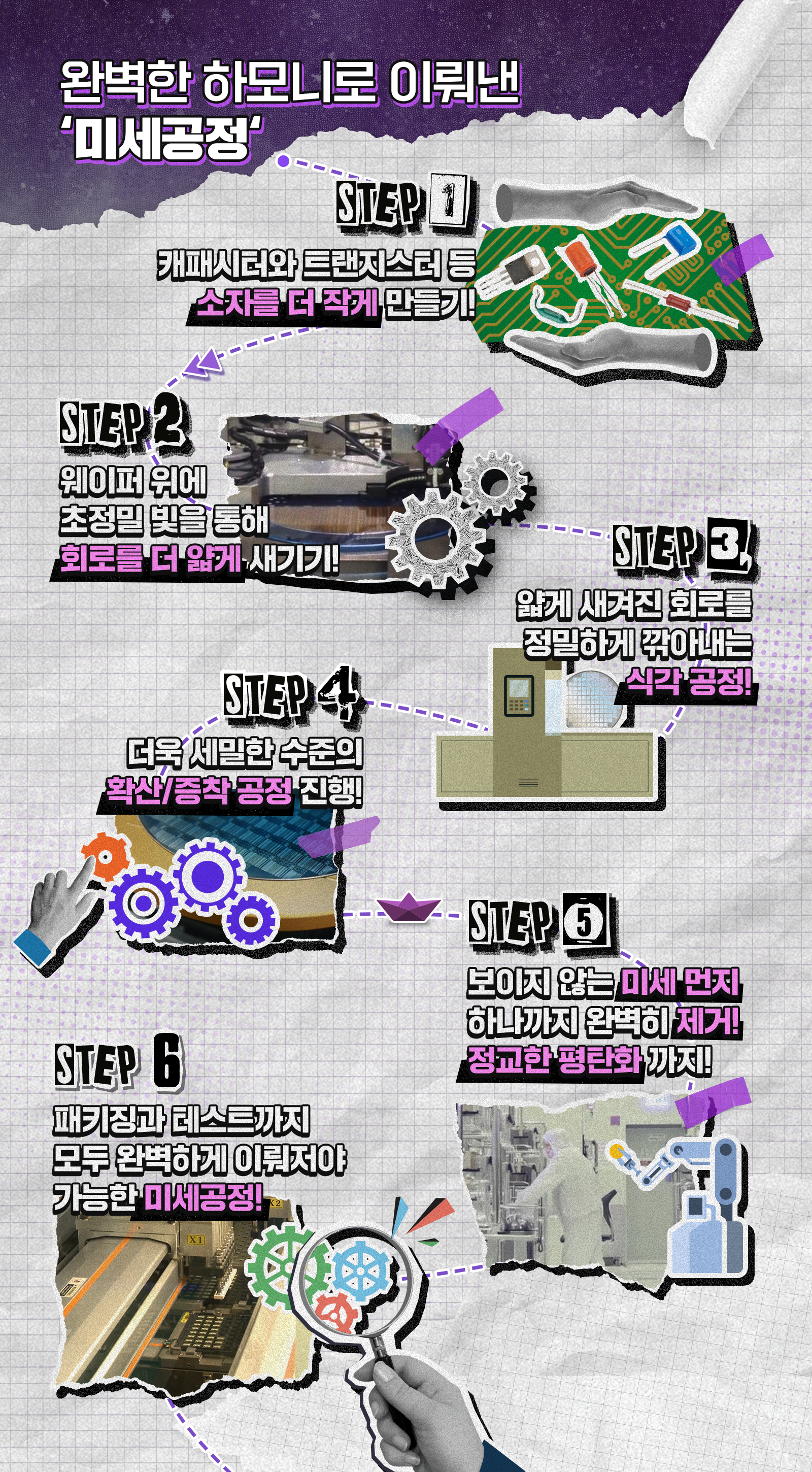

미세공정은 특정 조직이나 한 사람의 개인기만으로 개발할 수 있는 것이 아닌, 다양한 구성원들의 노력을 통해 완성되는 기술이다. 손톱만 한 칩 안에 캐패시터와 트랜지스터 등의 소자를 수십억 개 이상 구현해야 하고 이것들이 제대로 작동하게 하려면, 여러 분야의 전문가들이 한 몸처럼 움직여야 한다.

그중에서도 이 분야 선행 기술 확보는 SK하이닉스 미래기술연구원, D램 제품 기획 및 개발 등의 조직에서 담당한다. 이들은 미지의 영역을 개척하는 첨병 역할을 맡고 있다. 세상에 공개된 기술은 이미 수년 전부터 이들의 치열한 고민과 검토를 거쳤으며, 1c 기술의 태동도 바로 이곳에서부터 시작되었다.

이 기술을 실물로 구현하는 제조공정 조직의 책임도 막중하다. 회로를 작게 그리기 위해서는 웨이퍼에 패턴을 정밀하게 새기는 노광공정을 거쳐야 한다. 최근 극자외선(EUV) 공정으로 더 미세한 패터닝이 가능해졌고, 그만큼 반도체 집적도가 더 높아지고 있다.

이처럼 얇아진 회로를 입체적으로 구현하려면 식각공정을 통해 주변부를 정밀하게 깎아내는 작업이 필요하다. 이 공정은 미세화를 위해 꼭 필요한 부분만 남기는 과정인 만큼, 한번 잘못되면 되돌리기가 어려워 제품 수율과 품질에 직접적인 영향을 끼친다.

웨이퍼 위에 전기적 특성을 띠는 박막을 입혀 다음 공정의 ‘판’을 깔아주는 증착 공정도 중요하다. 특히, 초미세 회로를 구현하기 위해 원자 단위로 박막을 조절하는 ALD(Atomic Layer Deposition, 원자층 증착) 방식 등이 여기서 사용된다.

또, 미세한 패턴 위에 필요한 물질(이온)을 정확한 위치와 깊이로 주입하는 확산 공정, 웨이퍼 상에 더 작은 불순물을 완벽하게 제거하고 표면을 정교하게 연마하는 세정 및 평탄화 공정 등이 전체에서 중요한 몫을 차지한다. 이어, 새로운 기술이 정상 작동할 수 있도록 칩 간 전기적 연결, 칩 내부 발열 제어, 제조된 샘플의 동작 테스트 등을 수행하는 P&T(Package & Test) 공정이 미세화의 한계를 넘어서는 키(Key)가 되어주고 있다.

하나의 제품이 바깥세상으로 나오기까지 이 과정은 수백 번씩 교차로 반복되고 있으며, 여기서 생기는 단 한 번의 실수는 기술의 성패를 좌우하는 결정적 요소로 작용한다. 모든 조직은 완벽에 가까운 정교함을 유지해야 하고, 서로 끊임없이 소통, 보완하는 것이 중요하다. SK하이닉스가 세계 최초로 1c 개발에 성공할 수 있었던 가장 큰 요인이 구성원들의 원팀 스피릿이라고 평가 받는 이유다.

1c 기술은 이전 세대보다 뛰어난 성능과 품질, 생산 효율성 등을 제공하며 또 다른 메모리 혁신을 이끌 것으로 전망된다. 또, AI 메모리인 HBM을 비롯해 서버 및 데이터센터용 모듈, 모바일용 LPDDR, 그래픽용 GDDR 등 모든 차세대 D램 제품군에 적용될 수 있어 앞으로 시장에서의 파급 효과가 클 것으로 예상된다.

SK하이닉스는 현재 수준에 머무르지 않고, 전사 조직이 원팀으로 뭉친 협업 체계를 기반으로 미세공정 기술력을 계속 고도화하고 있다. 이를 통해 회사는 D램 시장 리더십과 함께 고객으로부터 가장 신뢰받는 ‘풀 스택 AI 메모리 프로바이더(Full Stack AI Memory Provider)’ 위상을 강화해 나간다는 계획이다.