전(前)공정 완료 후 웨이퍼 테스트를 마친 웨이퍼는, 백그라인딩(Back Grinding)을 시작으로 후(後)공정을 진행합니다. 백그라인딩이란 웨이퍼의 후면을 얇게 갈아내는 단계를 말하는데요. 이는 단순히 웨이퍼의 두께를 줄이는 것을 넘어, 전공정과 후공정을 연결해 앞뒤 공정에서 발생하는 문제들을 해결하는 역할을 하지요. 반도체 칩(Chip)은 얇을수록 더 높이 적층(Chip Stacking)하여 집적도를 높일 수 있는데, 집적도가 높아지면 기능이 저하되지만, 동시에 이를 통해 제품의 성능도 향상시켜야 하는 모순도 안고 있습니다. 따라서 웨이퍼 두께를 결정짓는 연삭(Grinding) 방식은 반도체 칩당 원가를 줄이고 제품 품질을 결정 짓는 변수 중의 하나가 됩니다.

1. 백그라인딩(Back Grinding)의 목적

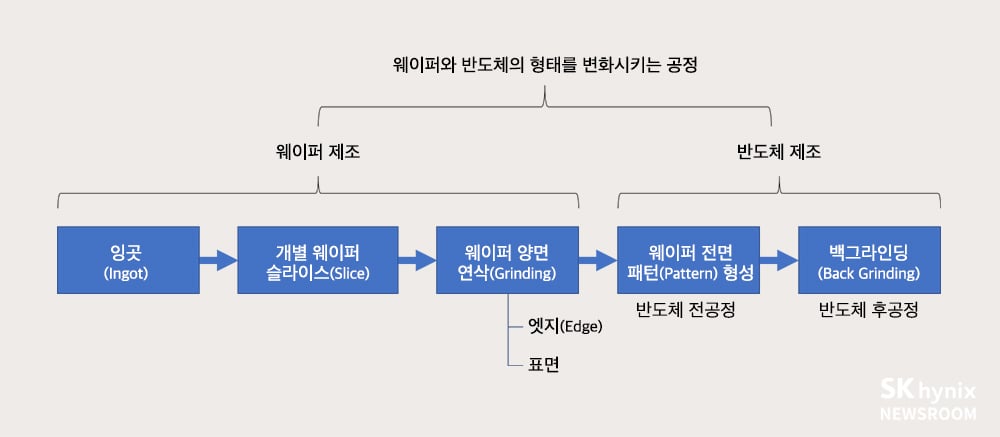

<그림1> 웨이퍼 제조와 반도체 제조상의 형태적 변화

웨이퍼가 반도체로 재탄생하는 과정에서 외형적 형태는 계속 변화합니다. 먼저, 웨이퍼 제조 공정에서는 웨이퍼의 엣지(Edge)와 표면을 연마(Polishing)하는 과정을 거칩니다. ▶<CMOS가 정착할 신대륙, 웨이퍼의 종류와 특성> 편 참고 이때는 일반적으로 웨이퍼의 양면을 모두 연삭하지요. 이후 전공정을 마친 웨이퍼는 후면만을 연삭하는 백그라인딩을 진행합니다. 전공정을 거치며 케미컬(Chemical)로 오염된 부분을 제거하고, 칩의 두께를 줄이기 위함이지요. IC카드나 모바일 기기 등에 탑재되는 매우 얇은(높이 1.4mm 수준) 칩을 만드는 데 유익한 작업입니다. 그 외 저항을 줄일 수 있어 전력 소모를 낮추는 데 기여하고, 열전도율을 높여 반도체가 정상 동작 시에 발생하는 열을 후면으로 빠르게 뺄 수 있는 장점이 있습니다. 대신 얇을수록 외부 힘에 의해 웨이퍼가 부러지고 뒤틀려지기 쉬워 핸들링하기 매우 어려워지지요.

2. 백그라인딩(Back Grinding)의 세부공정

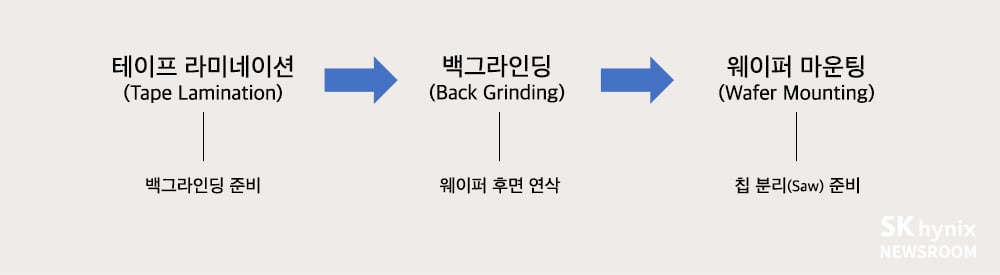

<그림2> 백그라인딩의 3가지 세부공정

백그라인딩은 총 세 가지 세부공정으로 나뉘어 진행됩니다. 먼저 1) 웨이퍼에 테이프를 붙이는 테이프 라미네이션(Tape Lamination)을 진행한 뒤, 2) 본격적으로 웨이퍼의 후면을 연삭합니다. 그리고 웨이퍼에서 칩을 분리하는 소잉(Sawing) 공정에 앞서 3) 웨이퍼를 테이프 위에 올려놓는 웨이퍼 마운팅(Wafer Mounting)을 진행하지요. 웨이퍼 마운팅은 실질적으로 칩을 분리(Chip Saw)하기 위한 준비 단계이므로, 이를 소잉 공정 속에 포함하기도 합니다. 최근에는 칩이 점점 얇아짐에 따라 공정의 순서가 변하기도 하며, 각 공정도 세분화되고 있습니다.

3. 웨이퍼를 보호하는 테이프 라미네이션(Tape Lamination)

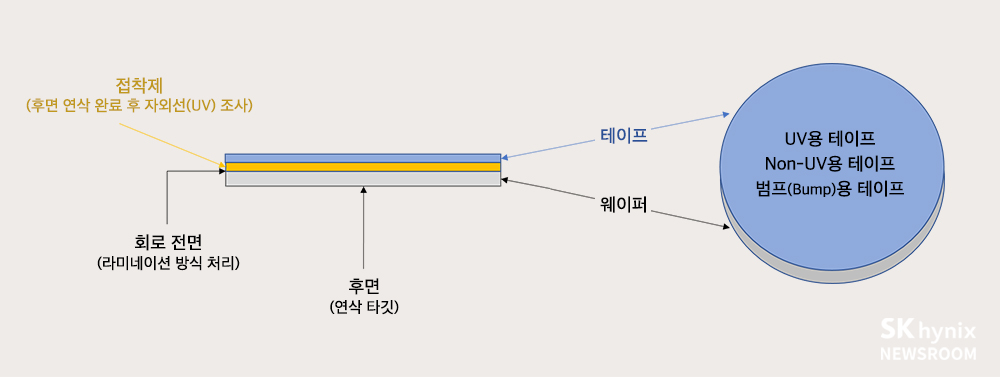

<그림3> 테이프 라미네이션 및 웨이퍼 전면 상태

백그라인딩의 첫 단계는 테이프 라미네이션입니다. 이는 코팅의 일종으로, 접착제를 바른 테이프를 웨이퍼 앞면에 부착시키는 작업을 말합니다. 백그라인딩을 진행하면 실리콘 가루(Silicon Compound)가 사방으로 퍼지게 되고, 연삭하는 힘에 의해 가끔 웨이퍼가 깨지거나(Broken) 뒤틀리기도(Warpage) 합니다. 특히 웨이퍼의 면적이 넓을수록 이러한 현상에 더욱 취약해지지요. 따라서 백그라인딩을 진행하기 전, 파란색의 얇은 UV(자외선)용 테이프를 붙여 웨이퍼를 보호해야 합니다.

백그라인딩을 마치면 다시 웨이퍼에 붙인 테이프를 떼야 합니다. 라미네이팅시에는 웨이퍼와 테이프 사이에 틈이나 기포가 발생하지 않도록 접착력을 높여야 하지만, 이때는 테이프 표면에 UV를 조사해 접착력을 떨어뜨립니다. 박리 후 테이프에 붙은 잔여물이 웨이퍼 표면에 묻어 있으면 안 되겠지요. Non-UV용 테이프를 사용하기도 하지만, 이는 접착력이 낮아 기포에 취약합니다. 단점이 많은 대신 가격이 저렴하지요. 그 외 UV용 테이프 두께의 2배 정도 되는 범프(Bump)용 테이프도 적용되고 있는데, 앞으로는 사용 빈도가 높아질 예정입니다.

4. 웨이퍼 두께와 칩 패키징(Chip Packaging)의 반비례 관계

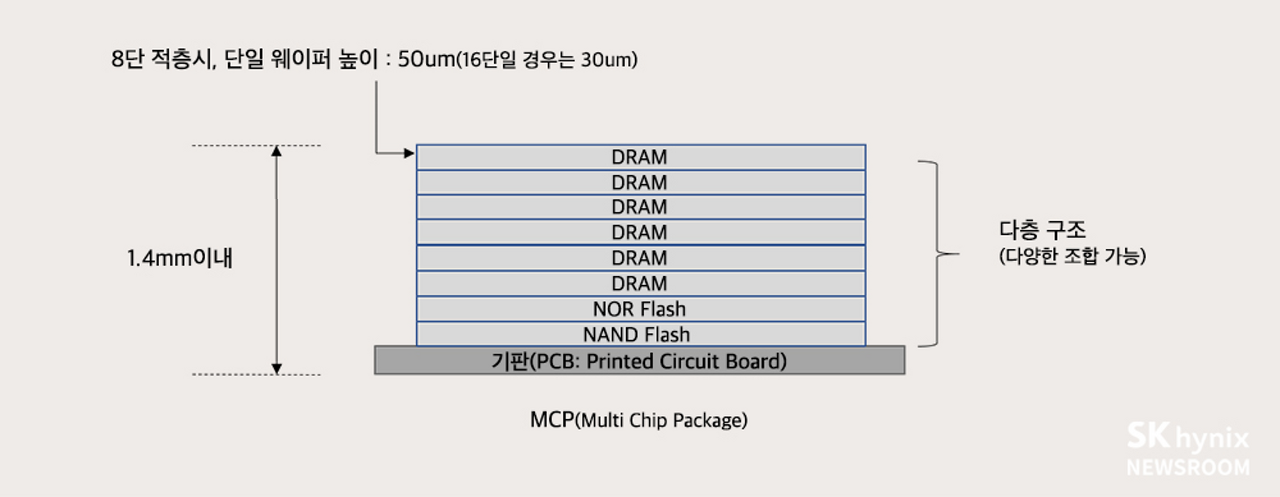

<그림4> MCP(Multi Chip Package) 구조

백그라인딩을 마친 웨이퍼는 두께가 보통 800~700㎛에서 80~70㎛ 수준으로 줄어들며, 약 10분의 1로 얇아진 웨이퍼를 4~6단으로 적층합니다. 최근에는 1차 연삭 후 또다시 5분의 1 수준인 20㎛ 정도로 얇게 만들어, 이를 16단 혹은 32단까지 적층하기도 합니다. 이렇듯 여러 층으로 쌓아 올린 반도체의 다층 구조를 MCP(Multi Chip Package, 이는 수직축 구조용어임)라 부릅니다. 이러한 경우 다(多)층일지라도 패키지 완성품의 총 높이는 1.4mm 이내여야 하기 때문에 웨이퍼를 더욱 얇게 깎아 높이를 맞춰야 하지요. 웨이퍼는 두께가 얇아질수록 결함이 증가해 다음 공정을 진행하기가 어려워지므로 고도의 기술력이 요구됩니다.

5. 백그라인딩(Back Grinding) 방식의 변신

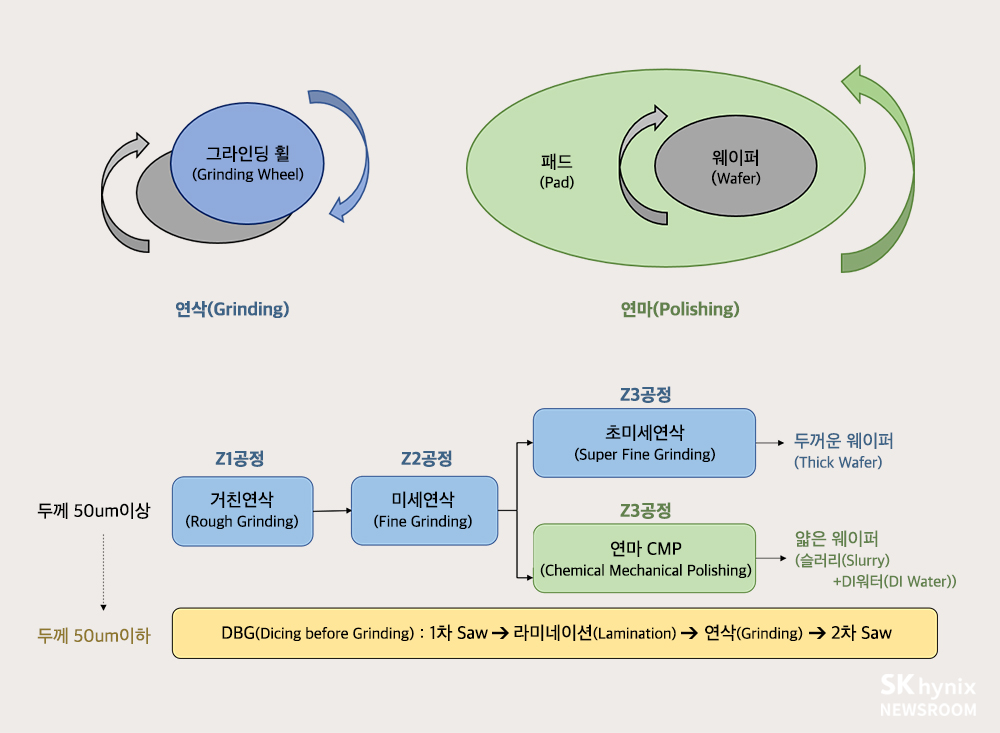

<그림5> 웨이퍼 두께에 따른 연삭 방식의 다변화

백그라인딩은 웨이퍼를 최대한 얇게 깎는 방향으로 가공기술의 한계를 극복하며 발전해왔습니다. 두께가 50㎛ 이상인 일반적인 웨이퍼의 백그라인딩은 총 3단계로 이뤄집니다. 먼저 1차로 거친 연삭(Rough Grinding)을 한 뒤 2차로 미세 연삭(Fine Grinding)을 진행하지요. 두 번의 연삭 과정을 통해 웨이퍼를 깎아낸 뒤, 연마 작업을 통해 거칠어진 웨이퍼의 표면을 다듬습니다. 이때 CMP(Chemical Mechanical Polishing)와 동일하게 슬러리(Slurry)와 DI워터(Deionized Water)를 패드와 웨이퍼 사이에 투입합니다. 이러한 연마 작업은 연삭된 표면에 광택을 내면서, 웨이퍼와 패드 사이의 마찰력을 둔화시키는 역할을 합니다. 웨이퍼가 두꺼울 때는 연마 대신 초미세연삭(Super Fine Grinding)을 진행하기도 하지만, 웨이퍼가 얇아질수록 연마는 반드시 수행해야 하는 필수 공정이 되었습니다.

웨이퍼가 더욱더 얇아지면 백그라인딩 공정 후 소잉 공정시 흠집이 나거나 깨지는 등 외부적 결함이 발생합니다. 따라서 웨이퍼의 두께가 50㎛ 이하인 경우, 공정 순서를 바꾸어 진행하기도 하는데요. 1차로 연삭을 하기 전 웨이퍼의 소잉을 반 정도 미리 실시하는 DBG(Dicing Before Grinding) 방식을 사용합니다. 다이싱(Dicing) > 연삭 > 다이싱 순으로 웨이퍼에서 칩을 안전하게 분리해냅니다. 그 외 특별한 방법으로 튼튼한 유리판을 이용해 웨이퍼가 깨지지 않도록 보호하며 연삭하기도 합니다.

전자기기 소형화 등에 따른 집적도 향상에 대한 요구에 발맞춰, 백그라인딩 기법 역시 꾸준히 한계를 극복하며 발전해야 합니다. 이에 따라 웨이퍼의 결함 문제는 물론 다음 공정에서 발생할 새로운 문제들에 대비해야 하겠지요. 이러한 문제들을 해결하기 위해 공정 순서를 바꾸거나, 반도체 전공정에 적용됐던 화학적 식각 기법 등을 도입해 종합적으로 새로운 가공 방식을 개발해야 합니다. 또한, 웨이퍼의 면적이 넓어지는 자체도 마이너스 요인으로 작용하는데, 특히 두께 50㎛의 12인치 웨이퍼를 기점으로 연삭 방식에도 여러 가지 변혁이 시도되고 있습니다. 그 외 웨이퍼를 연삭한 후 나오는 실리콘 잔여물을 재활용하는 연구도 이뤄지고 있답니다.

※ 본 칼럼은 반도체/ICT에 관한 인사이트를 제공하는 외부 전문가 칼럼으로, SK하이닉스의 공식 입장과는 다를 수 있습니다.